Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Синтез і дослідження лічильниківСодержание книги Поиск на нашем сайте

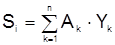

Лічильник ‒ операційний елемент для зберігання слова інформації та виконання над ним мікрооперацій рахування, що полягають у зміні (збільшенні або зменшенні) вмісту лічильника на 1. У лічильнику також виконуються допоміжні мікрооперації: очищення; зберігання вмісту; видача слова тощо. У комп`ютерах лічильники використовують для утворення послідов-ностей адрес команд, рахування кількостей циклів виконання операцій, ділення частоти імпульсів тощо. Лічильники можна класифікувати на основі наступних ознак: спосіб кодування; модуль рахування; напрямок рахування; спосіб організації міжрозрядних зв'язків; спосіб організації рахування. За способом кодування, розрізняють лічильники з позиційним і непозиційним кодуванням. У лічильниках iз позиційним кодуванням, числовий вираз i -ого поточ-ного стану лiчильника визначається формулою У лічильниках iз непозиційним кодуванням: розряди не мають постійної ваги; числовий вираз стану лічильника приписується кожному набору розрядів. Даний тип лічильників на практиці застосовується рідко. Модуль рахування Мліч ‒ кiлькicть різних стійких станів, крiзь які лі-чильник проходить у процесі одного циклу рахування (відображає граничну кiлькiсть імпульсів, яка може бути порахована лічильником). Наприклад, якщо потрібен лічильник, який рахує від 000 до 111 у двійковій системі числення, то у нього має бути 8 різних вихідних станів (вiн буде лічильником по модулю 8). За значенням модулю рахування, розрізняють: двійкові лічильники (Мліч = 2п); лічильники з довільним коефіцієнтом рахування, у яких модуль рахування не дорівнює цілому ступеню числа 2. Кодування лічильникiв iз довільним коефіцієнтом рахування також виконується двійковими кодами. Наприклад: лічильники з Мліч=4, Мліч=16 i Мліч=32 є двійковими лічильниками; лічильники з Мліч =5, Мліч=10 i Мліч=12 є лічильниками з довільним коефіцієнтом рахування (двійково-кодованими лічильниками). Лічильник з Мліч = 10 називають декадним або десятковим лічильником. За напрямком рахування, лічильники розділяють на підсумовувальні, віднімальні та реверсивні. У підсумовувальному лічильнику, надходження одного імпульсу на вхід збільшує вміст лічильника на 1; у віднімальному лічильнику, надходження одного імпульсу на вхід зменшує вміст лічильника на 1; реверсивним нази-вають лічильник, в якому можлива реалізація обох указаних мікрооперацій. За способом організації рахування, розрізняють асинхронні та синхронні лічильники. В асинхронному лічильнику: лічильні імпульси надходять на вхід першого тригеру; кожний наступний тригер перемикається тільки після зміни стану попереднього тригеру. Через послідовне перемикання тригерів, час встано-влення такого лічильника є тривалим: У синхронному лічильнику: лічильні імпульси надходять одночасно на входи всіх тригерів; перемикання тригерів відбувається синхронно з тактовим імпульсом. Структури двійкових лічильників можна отримати наступними спо-собами: синтезувати формальними методами; евристичним шляхом (ви-значенням закономірностей змін двійкових чисел при послідовному рахуваннi). Розглянемо зростаючу та спадаючу послідовності двійкових чотирироз-рядних чисел. Iз таблиці прямого рахування (підсумовування) випливає, що, при переході молодшого розряду з одиниці в нуль, сусідній старший розряд змінює стан на протилежний. Отже, підсумовувальний лічильник можна побудувати з двотактних лічильних тригерів iз управлінням за рівнем: прямий вихід кожного тригеру з'єднують iз входом керування наступного тригеру (рисунок 1, а). Якщо використовувати однотактні тригери з прямим динамічним управлінням, то слід інверсний вихід тригеру кожного молодшого розряду з'єднати з лічильним входом тригеру сусіднього старшого розряду (рис. 1, б). При використанні однотактних тригерів з інверсним динамічним керуванням, прямий вихід кожного тригеру підключають до входу керування наступного тригеру (рисунок 1, в). У цiлому, відповідні варіанти структур підсумовувальних послідовних лічильників на лічильних Т-тригерах подано на рисунку 1. Оскільки в одержаних структурах лічильників кожен тригер перемика-ється вихідним сигналом попереднього тригеру, то такі лічильники називають послідовними. Вказані лiчильники відрізняються простотою схеми, але мають низьку швидкодію; максимальний час встановлення в них спостерігається при переходах, які супроводжуються перемиканням усіх розрядів (наприклад, від 1111 до 0000 у чотирирозрядному підсумовувальному лічильнику).

Рисунок 1 - Структури підсумовувальних лічильників

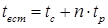

Варіанти структур вiднiмальних послідовних лічильників на лічильних Т-тригерах подано на рисунку 2.

Рисунок 2 - Структури віднімальних послідовних лічильників

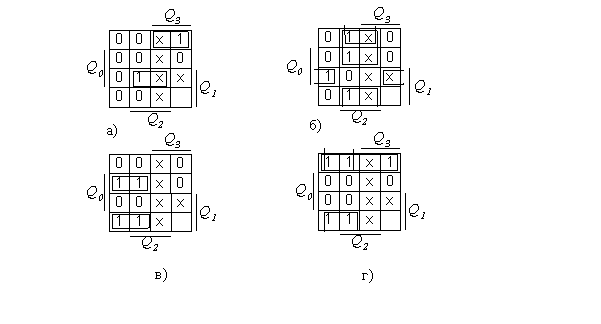

На практиці часто потрібні лічильники, коефіцієнт перерахунку яких відрізняється від цілого ступеня двійки, тобто Розрядність n двійкового лічильника повинна бути вибрана такою, щоб виконувалася умова Мліч > К ліч > 2n-1. При заданому коефіцієнті перерахунку, кількість тригерів лічильника дорівнює Для виключення зайвих станів лічильника з довільним коефіцієнтом рахування, використовують: 1) примусове скидання лічильника в початковий стан; 2) керування інформаційними входами тригерів логічними схемами. Застосування способу примусового скидання лічильника в початковий стан розглянемо на прикладі побудови асинхронного десяткового лічильника (рисунок 3). До схеми двійкового лічильника за модулем 16 було додатково введено логічну схему, що, з надходженням десятого імпульсу, встановлює всі тригери в нульовий стан. Двійковим числом, яке створюється в лічильнику з надходженням десятого імпульсу, є число 1010. При подачі логічної одиницi з виходів тригерів Q1 i Qз на входи логічного елементу І-НЕ, зазначений елемент скине всі тригери в стан 0. Таким чином, після надходження десятого імпульсу, лічильник починає знову рахувати з 0000 до 1001 (з 0 до 9).

Рисунок 3 - Схема асинхронного лічильника за модулем 10

Спосіб управлiння інформаційними входами тригерів для виключення зайвих станів лічильника зручний тим, що передбачає побудову формалізованим шляхом лічильника з будь-яким коефіцієнтом перерахунку. Суть даного методу полягає в тому, що кожний тригер лічильника перемикається окремою логічною схемою, що аналізує в кожному такті стан виходів усіх тригерів та подає на інформаційний вхід тригеру сигнал. Четвертий сигнал перемикає даний розрядний тригер у такий стан, який потрібний для відображення наступного числа. Розглянемо, наприклад, пiдхiд до проектування синхронного десяткового лічильника на Д-тригерах за допомогою формального методу. Даний метод оснований на сумісному використанні таблиці переходів лічильника та таблиці переходів тригерів. Таблиця переходів десяткового лiчильника (таблиця 1) показує значення інформаційних входiв тригерiв, потрiбнi для забезпечення вказаних переходiв.

Таблиця 1 – Таблиця переходів десяткового лічильника

Таблицю переходів D-тригеру представлено у таблицi 2.

Таблиця 2 – Таблиця переходів D-тригеру

Аналіз таблиці переходів D-тригеру показує, що сигнал на вході Di буде відповідати значенню виходу тригеру Qi в наступному такті: D3 = Q3П, D2 = Q2П, D1 = Q1П, Dо = Q0П. Даний факт відображений у таблиці 3 переходів тригеру Тз під час підрахунку десяткових чисел. Аналогічні таблиці можна скласти для інформаційних входів D2, D1, D0 інших тригерів лічильника.

Таблиця 3 – Значення сигналів на вході D3, що забезпечують потрібні переходи тригеру Т3 під час десяткового рахування

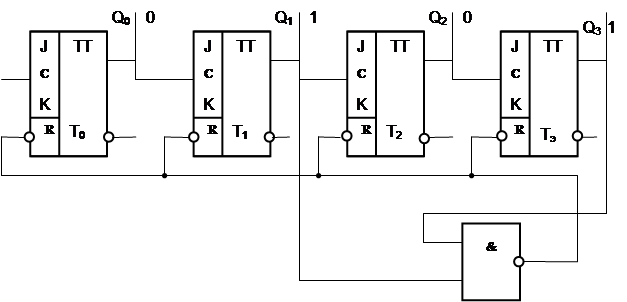

Представлений пiдхiд дає змогу розглядати таблицю 1 як таблицю істиності для логічних функцій Dз, D2, D1, D0, якi управляють інформаційними входами відповідних тригерів: у лівій частині таблиці записано логічні змінні Q3j, Q2j, Q1j, Q0j, де j = 0...9 – номер рядка; до стовпцiв правої частини таблицi занесено значення логічних функцій, відповідні вказаним значенням змінних. А саме, представлено наступнi логiчнi функцiї: D3j = f3(Q3j, Q2j, Q0j), D2j = f2(Q3j, Q2j, Q0j), D1j = f1(Q3j, Q2j, Q0j), D0j = f0(Q3j, Q2j, Q0j). Для отримання мінімізованих виразів функцій Dj за таблицею 1, заповнимо для них карти Карно-Вейча (рисунок 4), де значення функцій у зайвих станах (10, 11, 12, 13, 14, 15) буде позначено знаком невизначеності Х:

3 отриманих діаграм випливає, що:

Знаючи функції управлiння інформаційними входами тригерів, можна побудувати схему десяткового синхронного лічильника на D-тригерах. Випускаються готові інтегральні схеми лічильників iз різними модулями рахування, наприклад: К155ИЕ2 – чотирирозрядний десятковий асинхронний лічильник; К155ИЕ4 – чотирирозрядний лічильник-дільник на 2, 6 і 12; К155ИЕ9, К555ИЕ10 – чотирирозряднi десятковi синхроннi лічильники.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 430; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.2 (0.007 с.) |

, де n – кількість розрядів лічильника, Ak – вага k-го розряду, Yk – логічне значення k-го розряду (0 або 1). Прикладом є лічильник, який рахує в двійковій cистемі числення.

, де n – кількість розрядів лічильника, Ak – вага k-го розряду, Yk – логічне значення k-го розряду (0 або 1). Прикладом є лічильник, який рахує в двійковій cистемі числення. , де tс – тривалість синхро-імпульсу, n – число розрядів лічильника, tр – час перемикання одного тригеру.

, де tс – тривалість синхро-імпульсу, n – число розрядів лічильника, tр – час перемикання одного тригеру.

. Для одержання такого коефіцієнту перерахунку, часто використовують спосіб вилучення зайвих станів у двійковому лічильнику з модулем рахування n: Мліч=2n

. Для одержання такого коефіцієнту перерахунку, часто використовують спосіб вилучення зайвих станів у двійковому лічильнику з модулем рахування n: Мліч=2n , де

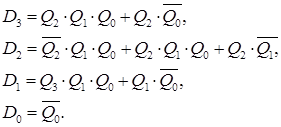

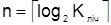

, де  позначає найменше ціле, що є більшим за вираз у дужках. Наприклад, для десяткового лічильника

позначає найменше ціле, що є більшим за вираз у дужках. Наприклад, для десяткового лічильника