Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Техническое описание микроконтроллера MCS-51Содержание книги

Поиск на нашем сайте

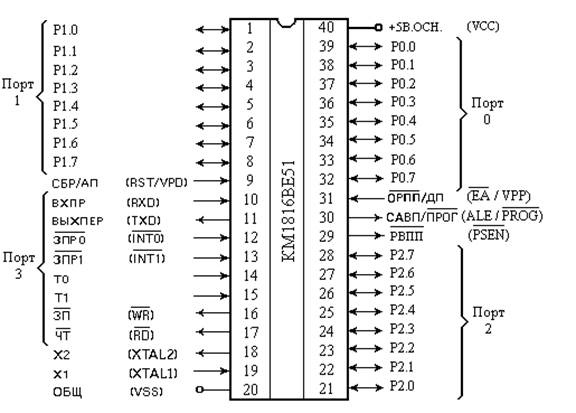

Техническое описание микроконтроллера MCS-51 1. Функциональное назначение выводов корпуса МК51 2. Структурная схема МК51 3. Система команд МК51 4. Порты ввода/вывода информации 5. Доступ к внешней памяти 6. Таймер/счётчик 7. Последовательный интерфейс 8. Система прерываний 9. Особые режимы работы МК51 Функциональное назначение выводов корпуса МК51 Микроконтроллер выполнен на основе высокоуровневой n-МОП[1] технологии и выпускается в корпусе БИС[2], имеющем 40 внешних выводов. Цоколевка корпуса МК51 и наименования выводов показаны на рис. 3.1. Для работы MK51 требуется один источник электропитания +5 В. Через четыре программируемых порта ввода/вывода MK51 взаимодействует со средой в стандарте ТТЛ-схем[3] с тремя состояниями выхода. Корпус МК51 имеет два вывода для подключения кварцевого резонатора, четыре вывода для сигналов, управляющих режимом работы МК, и восемь линий порта 3, которые могут быть запрограммированы пользователем на выполнение специализированных (альтернативных) функций обмена информацией со средой.

Рис. 3.1. Цоколевка корпуса МК51 и наименование выводов Структурная схема МК51 Основу структурной схемы МК51 (рис. 3.2) образует внутренняя двунаправленная 8-битная шина, которая связывает между собой все основные узлы и устройства: резидентную память, АЛУ, блок регистров специальных функций, устройство управления и порты ввода/вывода. Рассмотрим основные элементы структуры и особенности организации вычислительного процесса в МК51.

Резидентная память Память программ и память данных, размещенные на кристалле МК5 физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют разные функции. Память программ (ПЗУ или СППЗУ) имеет емкость 4 Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных сменных и т.п. РПП имеет 16-битную шину адреса, через которую обеспечивается доступ из счетчика команд или из регистра-указателя данных. Последний выполняет функции базового регистра при косвенных переходах по программе или используется в командах, оперирующих с таблицами. Память данных (ОЗУ) предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса регистров специальных функций (РСФ), которые перечислены в табл. 2.1. Память программ, так же как и память данных, может быть расширена до 64 Кбайт путем подключения внешних БИС. Аккумулятор и ССП. Аккумулятор является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвигов, проверка на нуль, формирование флага паритета и т.п. Таблица 2.1. Блок регистров специальных функций

При выполнении многих команд в АЛУ формируется ряд признаков операции (флагов), которые фиксируются в регистре ССП. В табл.2.2 приводится перечень флагов ССП, даются их символические имена и описываются условия их формирования. Таблица 2.2. Формат слова состояния программы (ССП)

Наиболее "активным" флагом ССП является флаг переноса, которые принимает участие и модифицируется в процессе выполнения множеств операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (C) выполняет функции "булевого аккумулятора" в командах, манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делает возможным использование арифметики в дополнительных кодах. АЛУ не управляет флагами селекции банка регистров (RS0, RS1), и их значение полностью определяется прикладной программой и используется для выбора одного из четырех регистровых банков. Широкое распространение получило представление о том, что в микропроцессорах, архитектура которых опирается на аккумулятор, большинство команд работают с ним, используя адресацию "по умолчанию" (неявную). В МК51 дело обстоит иначе. Хотя процессор в МК51 имеет в своей основе аккумулятор, однако, он может выполнять множество команд и без участия аккумулятора. Например, данные могут быть переданы из любой ячейки РПД в любой регистр, любой регистр может быть загружен непосредственным операндом и т.д. Многие логические операции могут быть выполнены без участия аккумулятора. Кроме того, переменные могут быть инкрементированы, декрементированы и проверены (test) без использования аккумулятора. Флаги и управляющие биты могут быть проверены и изменены аналогично. Регистры-указатели. 8-битный указатель стека (РУС) может адресовать любую область РПД. Его содержимое инкрементируется прежде, чем данные будут запомнены в стеке в ходе выполнения команд PUSH и CALL. Содержимое РУС декрементируется после выполнения команд POP и RET. Подобный способ адресации элементов стека называют прединкрементным/постдекрементным. В процессе инициализации МК51 после сигнала СБР в РУС автоматически загружается код 07H. Это значит, что если прикладная программа не переопределяет стек, то первый элемент данных в стеке будет располагаться в ячейке РПД с адресом 08Н. Двухбайтный регистр-указатель данных (РУД) обычно используется для фиксации 16-битного адреса в операциях с обращением к внешней памяти. Командами МК51 регистр-указатель данных может быть использован или как 16-битный регистр, или как два независимых 8-битных регистра (DPH и DPL). Таймер/счетчик. В составе средств МК51 имеются регистровые пары с символическими именами ТНО, TLO и THI, TLI, на основе которых функционируют два независимых программно-управляемых 16-битных таймера/счетчика событий. Буфер последовательного порта. Регистр с символическим именем SBUF представляет собой два независимых регистра - буфер приемника и буфер передатчика. Загрузка байта в SBUF немедленно вызывает начало процесса передачи через последовательный порт. Когда байт считывается из SBUF, это значит, что его источником является приемник последовательного порта. Регистры специальных функций. Регистры с символическими именами IP, IE, TMOD, TCON, SCON и PCON используются для фиксации и программного изменения управляющих бит и бит состояния схемы прерывания, таймера/счетчика, приемопередатчика последовательного порта и для управления мощностью электропитания МК51. Их организация будет описана ниже при рассмотрении особенностей работы МК51 в различных режимах. Таблица 3.1. Команды, модифицирующие флаги результата

Символическая адресация. При использовании ассемблера МК51 (ASM51) для получения объектных кодов программ допускается применение в программах символических имен регистров специальных функций (РСФ), портов и их отдельных бит (рис. 3.21). Для адресации отдельных бит РСФ и портов (такая возможность имеется не у всех РСФ) можно использовать символическое имя бита следующей структуры: < имя РСФ или порта >. < номер бита > Например, символическое имя пятого бита аккумулятора будет следующим: АСС.5. Символические имена РСФ, портов и их бит являются зарезервированными словами для ASM51, и их не надо определять с помощью директив ассемблера.

Рис. 3.20. Карта адресуемых бит

Рис. 3.21. Карта адресуемых бит в резидентной памяти данных блоке регистров специальных функций Рис 3.22. Граф путей передачи данных в МК51 В отличие от МК48 передачи данных в МК51 могут выполняться без участия аккумулятора. Аккумулятор. В отличие от МК48 обращение к аккумулятору может быть выполнено в МК51 с использованием неявной и прямой адресации. В зависимости от способа адресации аккумулятора применяется одно из символических имен: A или ACC (прямой адрес). При прямой адресации обращение к аккумулятору производится как к одному из РСФ, и его адрес указывается во втором байте команды. Использование неявной адресации аккумулятора предпочтительнее, однако не всегда возможно, например при обращении к отдельным битам аккумулятора. Обращение к внешней памяти данных. Режим косвенной адресации ВПД, имеющийся в МК48, реализован также и в МК51. При использовании команд MOVX @Ri обеспечивается доступ к 256 байтам внешней памяти данных. Существует также режим обращения к расширенной ВПД, когда для доступа используется 16-битный адрес, хранящийся в ретистре-указателе данных (DPTR). Команды MOVX @DPTR обеспечивают доступ к 65 536 байтам ВПД. Таблица 3.2. Группа команд передачи данных

Таблица 3.3. Группа команд арифметических операций

Команды ADD и ADDC аналогичны командам сложения МК48, но допускают сложение аккумулятора с большим числом операндов. Аналогично командам ADDC существуют четыре команды SUBB, что позволяет более просто, чем в МК48, производить вычитание байтов и многобайтных двоичных чисел. В МК51 реализуется расширенный (по сравнению с МК48) список команд инкремента/декремента байтов, введена команда инкремента 16-битного регистра-указателя данных. Таблица 3.4. Группа команд логических операций

В отличие от МК48 имеется возможность производить операцию "исключающее ИЛИ" с содержимым портов. Команда XRL может быть эффективно использована для инверсии отдельных бит портов. Таблица 3.5. Группа команд операции с битами

Существуют команды сброса (CLR), установки (SETB) и инверсии (CPL) бит, а также конъюнкции и дизъюнкции бита и флага переноса. Для адресации бит используется прямой восьмиразрядный адрес (bit). Косвенная адресация бит невозможна. Таблица 3.6. Группа команд передачи управления

Длинный переход. Переход по всему адресному пространству ПП. В команде содержится полный 16-битный адрес перехода (ad 16). Трех байтные команды длинного перехода содержат в мнемокоде букву L (Long). Всего существует две такие команды: LJMP - длинный переход и LCALL - длинный вызов подпрограммы. На практике редко возникает необходимость перехода в пределах всего адресного пространства и чаще используются укороченные команды перехода, занимающее меньше места в памяти. Абсолютный переход. Переход в пределах одной страницы памяти программ размером 2048 байт. Такие команды содержат только 11 младших бит адреса перехода (ad 11). Команды абсолютного перехода имеют формат 2 байта. Начальная буква мнемокода - A (Absolute). При выполнении команды в вычисленном адресе следующей по порядку команды ((РС)= (PC) + 2) 11 младших бит заменяются на ad11 из тела команды абсолютного перехода. Относительный переход. Короткий относительный переход позволяет передать управление в пределах -128 - +127 байт относительно адреса следующей команды (команды, следующей по порядку за командой относительного перехода). Существует одна команда безусловного короткого перехода SJMP (Short). Все команды условного перехода используют данный метод адресации. Относительный адрес перехода (rel) содержится во втором байте команды. Косвенный переход. Команда JMP @A + DPTR позволяет передавать управление по косвенному адресу. Эта команда удобна тем, что предоставляет возможность организации перехода по адресу, вычисляемому самой программой и неизвестному при написании исходного текста программы. Условные переходы. Развитая система условных переходов предоставляет возможность осуществлять ветвление по следующим условиям: аккумулятор содержит нуль (JZ); содержимое аккумулятора не равно нулю (JNZ); перенос равен единице (JC); перенос равен нулю (JNC); адресуемый бит равен единице (JB); адресуемый бит равен нулю (JNB). Для организации программных циклов удобно пользоваться командой DJNZ, которая работает аналогично соответствующей команде МК48. Однако в качестве счетчика циклов в МК51 может использоваться не только регистр, но и прямоадресуемый байт (например, ячейка РПД). Команда CJNE эффективно используется в процедурах ожидания какого-либо события. Например, команда WAIT: CJNE A,P0,WAIT будет выполняться до тех пор, пока на линиях порта 0 не установится информация, совпадающая с содержимым аккумулятора. Все команды данной группы, за исключением CJNE и JBC, не оказывают воздействия на флаги. Команда CJNE устанавливает флаг C, если первый операнд оказывается меньше второго. Команда JBC сбрасывает флаг C в случае перехода. Подпрограммы. Для обращения к подпрограммам необходимо использовать команды вызова подпрограмм (LCALL, ACALL). Эти команды в отличие от команд перехода (LJMP, AJMP) сохраняют в стеке адрес возврата в основную программу. Для возврата из подпрограммы необходимо выполнить команду RET. Команда RETI отличается от команды RET тем, что разрешает прерывания обслуженного уровня. Таблица 8.1. Альтернативные функции порта 3

Порт 0 является двунаправленным, а порты 1, 2 и З - квазидвунаправленными. Каждая линия портов может быть использована независимо для ввода или вывода информации. Для того чтобы некоторая линия порта использовалась для ввода, в D-триггер регистра-защелки порта должна быть записана 1, которая закрывает МОП-транзистор выходной цепи. По сигналу СБР в регистры-защелки всех портов автоматически записываются единицы, настраивающие их тем самым на режим ввода. Все порты могут быть использованы для организации ввода/вывода информации по двунаправленным линиям передачи. Однако порты 0 и 2 не могут быть использованы для этой цели в случае, если МК-система имеет внешнюю память, связь с которой организуется через общую разделяемую шину адреса/данных, работающую в режиме временного мультиплексирования. Запись в порт. При выполнении команды, которая изменяет содержимое регистра-защелки порта, новое значение фиксируется в регистре в момент S6P2 последнего цикла команды. Однако опрос содержимого регистра-защелки выходной схемой осуществляется во время фазы Р1 и, следовательно, новое содержимое регистра-защелки появляется на выходных контактах порта только в момент S1P1 следующего машинного цикла. Нагрузочная способность портов. Выходные линии портов 1, 2 и 3 могут работать на одну ТТЛ-схему. Линии порта 0 могут быть нагружены на два входа ТТЛ-схем каждая. Линии порта 0 могут работать и на n-МОП-схемы, однако при этом их необходимо подключать на источник электропитания через внешние нагрузочные резисторы за исключением случая, когда шина порта 0 используется в качестве шины адреса/данных внешней памяти. Входные сигналы для МК51 могут формироваться ТТЛ-схемами или n-МОП-схемами. Допустимо использование в качестве источников сигналов для МК51 схем с открытым коллектором или открытым стоком. Однако при этом время изменения входного сигнала при переходе из 0 в 1 окажется сильно затянутым. Особенности работы портов. Обращение к портам ввода/вывода возможно с использованием команд, оперирующих с байтом, отдельным битом и произвольной комбинацией бит. При этом в тех случаях, когда порт является одновременно операндом и местом назначения результата, устройство управления автоматически реализует специальный режим, который называется "чтение-модификация-запись". Этот режим обращения предполагает ввод сигналов не с внешних выводов порта, а из его регистра-защелки, что позволяет исключить неправильное считывание ранее выведенной информации. Подобный механизм обращения к портам реализован в следующих командах: ANL - логическое И, например ANL Р1, А; ORL - логическое ИЛИ, например ORL P2, А; XRL - исключающее ИЛИ, например XRL РЗ, А; JBC - переход, если в адресуемом бите единица, и последующий сброс бита, например JBC P1.1, LABEL; CPL - инверсия бита, например CPL P3.3; INC - инкремент порта, например INC P2; DEC - декремент порта, например DEC P2; DJNZ - декремент порта и переход, если его содержимое не равно нулю, например DJNZ РЗ, LABEL; MOV PX.Y, C - передача бита переноса в бит Y порта X; SET PX.Y - установка бита Y порта X; CLR PX.Y - сброс бита Y порта X. Совсем не очевидно, что последние три команды в приведенном списке являются командами "чтение-модификация-запись". Однако это именно так. По этим командам сначала считывается байт из порта, а затем записывается новый байт в регистр-защелку. Причиной, по которой команды "чтение-модификация-запись" обеспечивают раздельный доступ к регистру-защелке порта и к внешним выводам порта, является необходимость исключить возможность неправильного прочтения уровней сигналов на внешних выводах. Предположим для примера, что линия Y порта Х соединяется с базой мощного транзистора и выходной сигнал на ней предназначен для его управления. Когда в данный бит записана 1, то транзистор включается. Если для проверки состояния исполнительного механизма (в на

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-15; просмотров: 854; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.78.203 (0.016 с.) |