Мы поможем в написании ваших работ!

ЗНАЕТЕ ЛИ ВЫ?

|

Загальні відомості про лічильники

Лічильником називається цифровий пристрій, сигнали на виході якого у певному коді відображають кількість вхідних імпульсів, що надійшли. Приклад лічильників наведений на рис.7.1 та 7.2.

Рис. 7.1 Структурна схема n - розрядного послідовного лічильника, що додає на базі Т-тригерів.

Рис. 7.2 Структурна схема n - розрядного послідовного лічильника, що віднімає на базі Т-тригерів.

Промисловістю випускаються мікросхеми лічильники, в тому числі мікросхеми реверсивні лічильники типу К155ИЕ6, К555ИЕ6, КР1533ИЕ6, К155ИЕ7, К555ИЕ7, КР1533ИЕ7.

Якщо лічильник складається з декількох мікросхем, то для кожної мікросхеми потрібно визначити код, що подається на входи попередньої установки. Наприклад, якщо необхідно забезпечити Клч=73, то потрібно взяти два лічильника ИЕ7 (вони забезпечують Клч  ) або два лічильники ИЕ6 (вони забезпечують Клч ) або два лічильники ИЕ6 (вони забезпечують Клч  ). ).

Розрахунок коду для ИЕ7.

1-й спосіб.

Переводимо Клч –1=73-1 в двійкову систему числення 7210=0100 10002. На входи D i чотирьох молодших розрядів подаємо 1000, на входи D i чотирьох старших розрядів подаємо 0100 і забезпечуємо роботу лічильника в режимі віднімання. Лічильник послідовно проходить стани від 0100 1000 до 0000 0000.

2-й спосіб.

Переводимо Клч –1=73–1 в двійкову систему числення 7210=0100 10002. Інвертуємо всі розряди 1011 0111. На входи D i чотирьох молодших розрядів подаємо 0111; на входи D i чотирьох старших розрядів подаємо 1011 і забезпечуємо роботу лічильника в режимі додавання. Лічильник послідовно проходить стани від 1011 0111 до 1111 1111.

Розрахунок коду для ИЕ6.

1-й спосіб.

Переводимо Клч –1 = 73-1 в двійково–десяткову систему числення 7210=0111 00102-10. На входи D i чотирьох молодших розрядів подаємо 0010, на входи D i чотирьох старших розрядів подаємо 0111 і забезпечуємо роботу лічильника в режимі віднімання. Лічильник послідовно проходить стани від 0111 0010 до 0000 0000.

2-й спосіб.

Переводимо (100 –Клч)=100 –73=27 в двійково-десяткову систему числення

2710=0010 01112-10. На входи D i чотирьох молодших розрядів подаємо 0111; на входи D i чотирьох старших розрядів подаємо 0010 і забезпечуємо роботу лічильника в режимі додавання. Лічильник послідовно проходить стани від 0010 0111до 1001 1001.

Завдання

ПОРЯДОК ВИКОНАННЯ

1. Вивчити призначення, основи роботи та особливості застосування. Ознайомитися з основними принципами побудови схем лічильників.

2. Використовуючи елементи стенду зібрати схему дослідження лічильника, провести експериментальну перевірку функціонування. Після закінчення досліджень оформити звіт

Зміст звіту

1. Титульний аркуш.

2. Назва та мета роботи.

3. Завдання.

4. Необхідні короткі теоретичні відомості для кожного з виконаних пунктів завдання.

5. Таблиці істинності, необхідні розрахунки, всі схеми лише на елементах, що входять до складу стенду, діаграми та осцилограми.

6. Висновки по роботі.

4. Контрольні запитання

1.Як класифікуються лічильники?

2. Послідовні лічильники та принципи їх побудови

3.Паралелні лічильники та особливості їх побудови і функціонування.

4.Двійкові лічильники ИЕ7 та їх використання в обчислювальній техніці.

5.Двійково-десяткові лічильники ИЕ6 та їх використання в обчислювальній техніці.

6.Методика побудови лічильників з довільним модулем лічби на основі мікросхем ИЕ6 та ИЕ7.

Лабораторна робота № 8

Дослідження багаторежимного буферного регістра

Мета роботи

Вивчити схему, її можливості та особливості застосування; набути навичок у роботі з багаторежимних багаторозрядними буферними пристроями введення - виведення в мікропроцесорних та інших цифрових пристроях.

Основні теоретичні відомості

Багатофункціональний буферний регістр (ББР) - пристрій, що використовується для реалізації схем регістрів, стробовані буферів, мультиплексорів і т. д., тобто для реалізації основних периферійних функцій введення - виведення мікропроцесорних систем.

ББР на прикладі мікросхеми К589ІР12 включає 8-розрядний регістр на D-тригерах з буфером на вході, що має три стани: нульове, одиничне і високоінпендансное (рис. 8.1б). До складу ББР входить схема управління на елементах І, АБО, НЕ і тригер запиту обслуговування (переривання) Тобс, що формує відповідний сигнал управління перериванням мікропроцесора при використанні ББР в комплекті з ним.

Начало формы

На рис. 8.1 а, б наведені відповідно умовне позначення та структура МБР. Регістр імеетдва режиму роботи: введення і виведення, що задаються сигналом на керуючому вході MD: MD = 0 - введення; MD = 1 - висновок. У режимі введення (MD = 0) запис інформації з вхідного каналу DI1... DI8 в регістр МБР здійснюється сигналом STB = 1. Читання інформації проводиться через вихідний канал DO1... DO8 при вступі керуючих сигналів вибору кристала - CS1 ● CS2 = 1. У режимі виводу (MD = 1) читання інформації проводиться постійно, а запис здійснюється подачею керуючих сигналів вибору кристала CS1 ● CS2 = 1.

Скидання інформації, записаної в регістр, проводиться сигналом CLR = 0.

Однією з функцій МБР є формування наявності (INT = 0) або відсутності (INT = 1) запиту обслуговування (переривання), які служать для управління роботою мікропроцесора. Перед початком роботи сигналом очищення CLR = 0 тригер Тобс встановлюється в «1», а сигнали вибору кристала відсутні (CS1 ● CS2 = 0). При цьому на виході INT = 1 МБР формується сигнал відсутності запиту переривання. Одночасно із записом вхідної інформації в регістр МБР (MD = 0) сигналом STB = 1 тригер Тобс скидається в «0». При цьому на виході формується сигнал INT = 0. За цим сигналом мікропроцесор перериває свою роботу, видає сигнали вибору кристала CS1 ● CS2 = 1 і читає інформацію з регістра МБР. Після зчитування чергового байта даних сигнал на виході INT приймає первинне значення INT = 1, тригер Тобс встановлюється у вихідне 1-е стан. Установка тригера Тобс в «1» виробляється сигналом вибору кристала CS1 ● CS2 = 1, а вихідний сигнал INT = 0 присутній протягом дії сигналів вибору кристала і зникає (INT = 1) після їх закінчення.

Na rys. 1.1 a, b navedeni vidpovidno umovne poznachennya ta struktura MBR. Rehistr imeetdva rezhymu roboty: vvedennya i vyvedennya, shcho zadayutʹsya syhnalom na keruyuchomu vkhodi MD: MD = 0 - vvedennya; MD = 1 - vysnovok. U rezhymi vvedennya (MD = 0) zapys informatsiï z vkhidnoho kanalu DI1... DI8 v rehistr MBR zdiy̆snyuyetʹsya syhnalom STB = 1. Chytannya informatsiï provodytʹsya cherez vykhidnyy̆ kanal DO1... DO8 pry vstupi keruyuchykh syhnaliv vyboru krystala - CS1 ● CS2 = 1. U rezhymi vyvodu (MD = 1) chytannya informatsiï provodytʹsya postiy̆no, a zapys zdiy̆snyuyetʹsya podacheyu keruyuchykh syhnaliv vyboru krystala CS1 ● CS2 = 1.

Skydannya informatsiï, zapysanoï v rehistr, provodytʹsya syhnalom CLR = 0.

Odniyeyu z funktsiy̆ MBR ye formuvannya nayavnosti (INT = 0) abo vidsutnosti (INT = 1) zapytu obsluhovuvannya (pereryvannya), yaki sluzhatʹ dlya upravlinnya robotoyu mikroprotsesora. Pered pochatkom roboty syhnalom ochyshchennya CLR = 0 tryher Tobs vstanovlyuyetʹsya v «1», a syhnaly vyboru krystala vidsutni (CS1 ● CS2 = 0). Pry tsʹomu na vykhodi INT = 1 MBR formuyetʹsya syhnal vidsutnosti zapytu pereryvannya. Odnochasno iz zapysom vkhidnoï informatsiï v rehistr MBR (MD = 0) syhnalom STB = 1 tryher Tobs skydayetʹsya v «0». Pry tsʹomu na vykhodi formuyetʹsya syhnal INT = 0. Za tsym syhnalom mikroprotsesor pereryvaye svoyu robotu, vydaye syhnaly vyboru krystala CS1 ● CS2 = 1 i chytaye informatsiyu z rehistra MBR. Pislya zchytuvannya cherhovoho bay̆ta danykh syhnal na vykhodi INT pryy̆maye pervynne znachennya INT = 1, tryher Tobs vstanovlyuyetʹsya u vykhidne 1-e stan. Ustanovka tryhera Tobs v «1» vyroblyayetʹsya syhnalom vyboru krystala CS1 ● CS2 = 1, a vykhidnyy̆ syhnal INT = 0 prysutniy̆ protyahom diï syhnaliv vyboru krystala i znykaye (INT = 1) pislya ïkh zakinchennya.

Словарь

Конец формы

Начало формы

Опис панелі дослідження МБР

Панель дослідження, наведена на рис. 8.2 складається з двох ББР (ББР1 і ББР2), включених так, що вихідні шини ББР2 з'єднані з вхідними шинами ББР1 і навпаки. Для завдання вхідних даних служать контактні площадки, з'єднані через 8-розрядні согласующие регістри на RS-тригерах (СР1, СР2) з шинами DI1... DI8 відповідних мікросхем. Стан входів і виходів тригерів мікросхем индицируется світлодіодами. Комутація керуючих входів кожної з мікросхем здійснюється кнопками SB1... SB4 для ББР1 і SB6... SB9 для ББР2. Скидання регістрів мікросхем в "0" здійснюється кнопками SB5 для ББР1 і SB10 для ББР2. Інформація про стан тригера Тобс кожного ББР висвічується світлодіодами INT. Вхідна інформація через елементи АБО-НЕ записується в узгоджувальний регістр, звідки згодом зчитується на вхідну шину даних ББР. Установка в «0» узгоджувальних регістрів СР1 і СР2 здійснюється кнопками, підключеними на їх вхід R.

Opys paneli doslidzhennya MBR

Panelʹ doslidzhennya, navedena na rys. 1.2 skladayetʹsya z dvokh MBR (MBR1 i MBR2), vklyuchenykh tak, shcho vykhidni shyny MBR2 z'yednani z vkhidnymy shynamy MBR1 i navpaky. Dlya zavdannya vkhidnykh danykh sluzhatʹ kontaktni ploshchadky, z'yednani cherez 8- rozryadni sohlasuyushchye rehistry na RS - tryherakh (SR1, SR2) z shynamy DI1... DI8 vidpovidnykh mikroskhem. Stan vkhodiv i vykhodiv tryheriv mikroskhem yndytsyruet·sya svitlodiodamy. Komutatsiya keruyuchykh vkhodiv kozhnoï z mikroskhem zdiy̆snyuyetʹsya knopkamy SB1... SB4 dlya MBR1 i SB6... SB9 dlya MBR2. Skydannya rehistriv mikroskhem v "0 " zdiy̆snyuyetʹsya knopkamy SB5 dlya MBR1 i SB10 dlya MBR2. Informatsiya pro stan tryhera Tobs kozhnoho MBR vysvichuyetʹsya svitlodiodamy INT. Vkhidna informatsiya cherez elementy ABO -NE zapysuyetʹsya v uz·hodzhuvalʹnyy̆ rehistr, zvidky z·hodom zchytuyetʹsya na vkhidnu shynu danykh MBR. Ustanovka v «0» uz·hodzhuvalʹnykh rehistriv SR1 i SR2 zdiy̆snyuyetʹsya knopkamy, pidklyuchenymy na ïkh vkhid R.

Словарь

Конец формы

Рис.8.2. Панель дослідження ББР

Порядок виконання роботи

Дослідження МБР в режимі стробуємого буфера

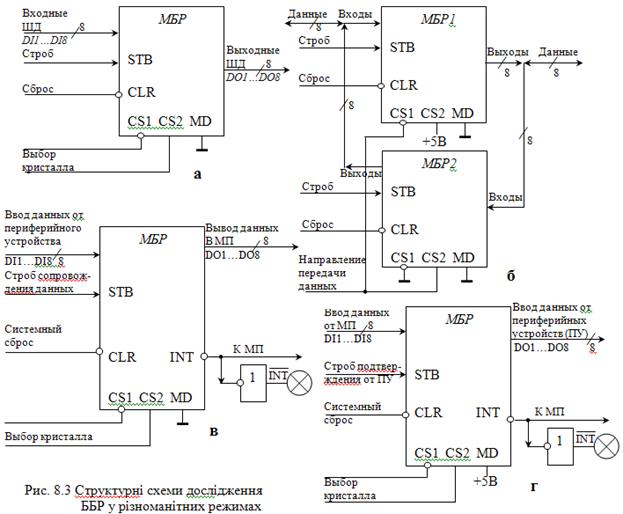

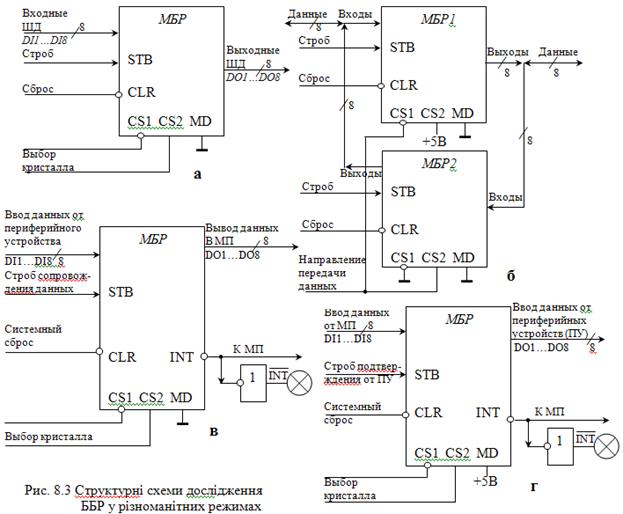

Досліджується робота (структурна схема дослідження показана на рис. 8.3а) одного кристала в режимі запису в нього інформацією з вхідних шин даних Вх.ШД1 (DI1... DI8) і виведення її на вихідні шини Вих.ШД1 (DO1... DO8).

1. Сигналом CLR = 0 скинути ББР1 в початковий стан;

2. За допомогою набору кнопок D1 встановити на входах ББР1 заданий викладачем байт даних;

3. За допомогою кнопок SB3 і SB4 подати відповідно на керуючий вхід MD ББР1 «0» і на стробирующий вхід STB ББР1 «1»;

4. Встановити у початковий стан регістр СР1, при цьому на Вх.ШД1 встановлюється код 00000000;

5. За допомогою кнопок SB1 і SB2 подати на входи CS1 і CS2 відповідно «0» і «1», тобто CS1 ● CS2 = 1.

6. Переконатися, що дані з вхідних шин ББР1 відразу надходять на вихід ББР1.

Дослідження МБР в режимі двунаправленного шинного формувача

Структурна схема проведення дослідження представлена на рис. 8.3 б. Досліджується спільна робота двох кристалів. При цьому МБР1 працює як прямо (зліва направо) пропускає буфер, а МБР2 - як назад (справа наліво) пропускає буфер. Одночасно працює тільки один кристал, а другий у цей час перебуває в високоінпендансном (третьому) стані.

Для дослідження режиму передачі інформації зліва направо регістр МБР1 працює в режимі стробірующего буфера, а МБР2 - в третьому стані (для нього виконується умова CS1 ● CS2 = 0). Для дослідження передачі інформації справа наліво стану МБР1 і МБР2 змінюються на протилежні. Шини даних формувача в залежності від напрямку передачі інформації використовуються як вхідні або вихідні.

Робота виконується в тому ж порядку, що і в попередньому режимі, за винятком необхідності попереднього вибору напрямку передачі. Цей напрямок задається спеціальним сигналом, що приймають значення «0» - напрям передачі зліва направо і «1» - справа наліво.

Начало формы

Дослідження ББР в режимі вхідного порту при передачі даних від периферійного пристрою в мікропроцесор

На рис. 8.3 у представлена структурна схема проведення дослідження. ББР досліджується в режимі сумісної роботи з мікропроцесором, роль якого в даному випадку виконує оператор. Дані вводяться з периферійного устаткування (D1) в мікропрцессор (СР2). У цьому режимі спочатку завантажуються дані, набрані на D1 в порт (ББР1) за умови, що для нього встановлені наступні сигнали: STB = 1, MD = 0, CS1 ● CS2 = 0. Тригер Тобс встановлюється в «0», на виході INT ББР1 з'являється сигнал запиту переривання INT = 0. Цей сигнал інвертується інвертором і индицируется світлодіодом. При цьому оператор ідентифікує порт і формує сигнали вибірки кристала CS1 = 0; CS2 = 1 (CS1 ● CS2 = 1). Дані виводяться на вихідні шини ББР1 (DO1... DO8) і передаються мікропроцесору. Одночасно встановлюється у вихідне (одиничне) стан тригер Тобс і при відключенні сигналів вибору кристала (CS1 ● CS2 = 0) гасне світлодіод (INT = 0).

Послідовність виконання роботи:

1. На шинах даних DI1... DI8 за допомогою пристрою D1 задати заданий викладачем байт даних;

2. Здійснити запис цього байта в ББР1, задавши значення STB = 1, MD = 0, CS1 ● CS2 = 0;

3. При загорянні сигналу запиту переривання INT необхідними кнопками сформувати умову CS1 ● CS2 = 1;

4. Читати на вихідних шинах дані, передані з вхідних шин.

Дослідження ББР в режимі вихідного порту при передачі даних з мікропроцесора в периферійний пристрій

Структурна схема дослідження наведена на рис. 8.3 г. В цьому режимі здійснюється виведення даних з мікропроцесора в периферійне пристрій. Сигнал на вході STB виконує функйію підтвердження отримання даних периферійним пристроєм. Під дією цього сигналу виробляється сигнал переривання INT = 0, який дозволяє мікропроцесору передачу наступного байта даних. Вибір порту забезпечується сигналами на входах CS1 і CS2.

У цьому режимі (MD = 1) при виборі кристала (порту) (CS1 ● CS2 = 1) інформація завантажується в кристал і відразу ж виводиться на вихідні шини DO1... DO8 (тобто надходить в периферійне пристрій. Периферійне пристрій (у даному випадку оператор) фіксує прийом інформації і видає підтвердження, шляхом завдання STB = 1 ББР1. Це призводить до скидання тригера переривання Тобс, який виробляє сигнал INT = 0, що надходить у мікропроцесор як підтвердження прийому даних периферійним пристроєм і тим самим дозволяє передачу наступного байта даних.

Послідовність виконання роботи:

1. На шинах даних DI1... DI8 за допомогою пристрою D1 задати заданий викладачем байт даних;

2. На вхід вибору режиму MD кристала ББР1 подати +5 В;

3. Сигналами CS1 і CS2 ББР1 вибрати кристал (порт);

4. Прочитати на виходах DO1... DO8 прийшов зі входу байт даних;

5. Імітувати прийом інформації периферійним пристроєм шляхом подачі на вхід STB ББР1 логічної «1»;

6. Зафіксувати спрацьовування тригера Тобс (запалюється світлодіод INT).

КОНТРОЛЬНІ ПИТАННЯ

1. Яке призначення ББР?

2. Поясніть основні режими роботи ББР.

3. Назвіть основні команди управління ББР і яке їх призначення.

4. Що таке третій стан виходів ББР і як воно реалізується?

5. Для чого використовується тригер переривання ББР?

6. За якої умови формується сигнал INT = 0?

Doslidzhennya MBR v rezhymi vkhidnoho portu pry peredachi danykh vid peryferiy̆noho prystroyu v mikroprtsessor

Na rys. 1.3 u predstavlena strukturna skhema provedennya doslidzhennya. MBR doslidzhuyetʹsya v rezhymi sumisnoï roboty z mikroprotsesorom, rolʹ yakoho v danomu vypadku vykonuye operator. Dani vvodyatʹsya z peryferiy̆noho ustatkuvannya (D1) v mikroprtsessor (SR2). U tsʹomu rezhymi spochatku zavantazhuyutʹsya dani, nabrani na D1 v port (MBR1) za umovy, shcho dlya nʹoho vstanovleni nastupni syhnaly: STB = 1, MD = 0, CS1 ● CS2 = 0. Tryher Tobs vstanovlyuyetʹsya v «0», na vykhodi INT MBR1 z'yavlyayetʹsya syhnal zapytu pereryvannya INT = 0. Tsey̆ syhnal invertuyetʹsya invertorom i yndytsyruet·sya svitlodiodom. Pry tsʹomu operator identyfikuye port i formuye syhnaly vybirky krystala CS1 = 0; CS2 = 1 (CS1 ● CS2 = 1). Dani vyvodyatʹsya na vykhidni shyny MBR1 (DO1... DO8) i peredayutʹsya mikroprotsesoru. Odnochasno vstanovlyuyetʹsya u vykhidne (odynychne) stan tryher Tobs i pry vidklyuchenni syhnaliv vyboru krystala (CS1 ● CS2 = 0) hasne svitlodiod (INT = 0).

Poslidovnistʹ vykonannya roboty:

1. Na shynakh danykh DI1... DI8 za dopomohoyu prystroyu D1 zadaty zadanyy̆ vykladachem bay̆t danykh;

2. Zdiy̆snyty zapys tsʹoho bay̆ta v MBR1, zadavshy znachennya STB = 1, MD = 0, CS1 ● CS2 = 0;

3. Pry zahoryanni syhnalu zapytu pereryvannya INT neobkhidnymy knopkamy sformuvaty umovu CS1 ● CS2 = 1;

4. Chytaty na vykhidnykh shynakh dani, peredani z vkhidnykh shyn.

Doslidzhennya MBR v rezhymi vykhidnoho portu pry peredachi danykh z mikroprotsesora v peryferiy̆nyy̆ prystriy̆

Strukturna skhema doslidzhennya navedena na rys. 1.3 h. V tsʹomu rezhymi zdiy̆snyuyetʹsya vyvedennya danykh z mikroprotsesora v peryferiy̆ne prystriy̆. Syhnal na vkhodi STB vykonuye funky̆iyu pidtverdzhennya otrymannya danykh peryferiy̆nym prystroyem. Pid diyeyu tsʹoho syhnalu vyroblyayetʹsya syhnal pereryvannya INT = 0, yakyy̆ dozvolyaye mikroprotsesoru peredachu nastupnoho bay̆ta danykh. Vybir portu zabezpechuyetʹsya syhnalamy na vkhodakh CS1 i CS2.

U tsʹomu rezhymi (MD = 1) pry vybori krystala (portu) (CS1 ● CS2 = 1) informatsiya zavantazhuyetʹsya v krystal i vidrazu zh vyvodytʹsya na vykhidni shyny DO1... DO8 (tobto nadkhodytʹ v peryferiy̆ne prystriy̆. Peryferiy̆ne prystriy̆ (u danomu vypadku operator) fiksuye pryy̆om informatsiï i vydaye pidtverdzhennya, shlyakhom zavdannya STB = 1 MBR1. Tse pryzvodytʹ do skydannya tryhera pereryvannya Tobs, yakyy̆ vyroblyaye syhnal INT = 0, shcho nadkhodytʹ u mikroprotsesor yak pidtverdzhennya pryy̆omu danykh peryferiy̆nym prystroyem i tym samym dozvolyaye peredachu nastupnoho bay̆ta danykh.

Poslidovnistʹ vykonannya roboty:

1. Na shynakh danykh DI1... DI8 za dopomohoyu prystroyu D1 zadaty zadanyy̆ vykladachem bay̆t danykh;

2. Na vkhid vyboru rezhymu MD krystala MBR1 podaty +5 V;

3. Syhnalamy CS1 i CS2 MBR1 vybraty krystal (port);

4. Prochytaty na vykhodakh DO1... DO8 pryy̆shov zi vkhodu bay̆t danykh;

5. Imituvaty pryy̆om informatsiï peryferiy̆nym prystroyem shlyakhom podachi na vkhid STB MBR1 lohichnoï «1»;

6. Zafiksuvaty spratsʹovuvannya tryhera Tobs (zapalyuyetʹsya svitlodiod INT).

KONTROLʹNI PYTANNYA

1. Yake pryznachennya MBR?

2. Poyasnitʹ osnovni rezhymy roboty MBR.

3. Nazvitʹ osnovni komandy upravlinnya MBR i yake ïkh pryznachennya.

4. Shcho take tretiy̆ stan vykhodiv MBR i yak vono realizuyetʹsya?

5. Dlya choho vykorystovuyetʹsya tryher pereryvannya MBR?

6. Za yakoï umovy formuyetʹsya syhnal INT = 0?

Словарь

Конец формы

Лабораторна робота № 9

ДОСЛІДЖЕННЯ ЦЕНТРАЛЬНОГО ПРОЦЕСОРА

1. Мета роботи.

Ознайомитися з архітектурою типового центрального процесора, структурою його команд, алгоритмом виконання процесором різних команд, роботою центрального процесора в різних режимах.

2. Основні теоретичні відомості.

Центральний процесор (ЦП) обробляє дані і керує цією обробкою відповідно до команд та інструкціями, записаними в програмах, і використовується для автоматичного виконання послідовності операцій (арифметичних, логічних, управління, введення / виводу), що містяться в програмі вирішення завдання. Структурна схема типового ЦП наведена на рис. 9.1.

Рис.9.1. Структурна схема типового центрального процесора

На рис. 9.2 представлена архітектура мікропрцессора КР580ВМ80. Мікросхема КР580ВМ80А являє собою 8-розрядне центральне процесорний пристрій (ЦПУ) паралельної обробки даних. Пристрій не має можливість апаратного нарощування розрядності оброблюваних даних, але дозволяє здійснювати це програмним способом.

Арифметичне-логічний пристрій (Σ) забезпечує виконання арифметичних, логічних операцій і операцій зсуву над двійковими даними, представленими в додатковому коді, або над двійково-десятковими даними. Пристрій містить схему десяткової корекції, що дозволяє робити операції десяткової арифметики. За результатами операцій в Σ формується ряд ознак, які записуються в регістр ознак (РФ). Ознака перенесення З встановлюється в одиницю, якщо в результаті виконання команди з'являється перенесення з старшого розряду. Додатковий ознака перенесення АС встановлюється в одиницю при виникненні переносу з третього розряду і використовується в командах десяткової арифметики. Ознака парності Р встановлюється в одиницю, якщо число одиниць в розрядах результату парне.

Ознака нуля Z встановлюється в одиницю, якщо результат дорівнює нулю. Ознака знака S вказує знак числа і дорівнює одиниці, якщо число негативне, або нулю, якщо число позитивне.

Блок регістрів загального призначення (РОН) проводить прийом, зберігання і видачу різної інформації, що бере участь в процесі виконання програми, і містить лічильник команд (ПС), покажчик стека (УС), регістри загального призначення (B, C, D, E, H, L), регістри тимчасового зберігання (W, Z) і регістр адреси (РА).

Шестнадцатирозрядний лічильник команд зберігає поточний адресу команди. Вміст лічильника команд автоматично збільшується після вибірки кожного байта команди. Шестнадцатирозрядний покажчик стека містить початкову адресу пам'яті, що використовується для зберігання і відновлення вмісту програмно-доступних регістрів ЦПУ, Вміст покажчика стека зменшується, коли дані завантажуються в стек, і збільшується, коли дані вибираються з стека. Восьмирозрядні регістри загального призначення У, С, D, Е, Н, L можуть застосовуватися як накопичувачі (оброблювані дані знаходяться в самому регістрі) та покажчики (16-розрядний адрес операнда визначається вмістом пари регістрів - BC, DE, HL). Регістри тимчасового зберігання W, Z використовуються для прийому та тимчасового запам'ятовування другого і третього байтів команд переходів, переданих з внутрішньої магістралі ЦПУ в лічильник команд. Ці регістри є програмно-недоступними. Шестнадцатирозрядний регістр адреси приймає і зберігає протягом одного машинного циклу адресу команди або операнда і видає його на односпрямовану вихідну магістраль ША.

Пристрій керування та синхронізації формує машинні такти і цикли, які координують виконання всіх команд, і виробляє сигнал SYNC «Синхронізація», який визначає початок кожного машинного циклу. Для виконання команди потрібно від одного до п'яти машинних циклів. Кожен цикл може складатися з 3-5 тактів (Т1-Т5), тривалість кожного з них відповідає періоду проходження тактових імпульсів Ф1, Ф2. Центральний процесор, крім стану роботи, може перебувати в трьох станах (очікування, захоплення і останов), тривалість яких складає ціле число тактів і залежить від зовнішніх керуючих сигналів.

До складу пристрою управління входить регістр команд, дешифратор команд і схеми керування вузлами. Восьмирозрядний регістр команд здійснює прийом і зберігання команди, що надходить по магістралі даних. Дешифратор команд дешифрує код операції команди та формує мікрооперації відповідно до мікропрограмою виконання команди. Схема управління вузлами виробляє для різних вузлів ЦПУ необхідні керуючі сигнали.

Восьмирозрядний буфер даних забезпечує введення команд і даних в ЦПУ, виведення даних та стану ЦПУ через формувачі, що мають на виході стан «Вимкнено».

Набір команд мікропроцесора КР580ВМ80

Команди мікропроцесора можуть бути одно-, двох-і трехбайтнимі. За функціональним призначенням команди діляться на:

- Команди виконання арифметичних операцій;

- Команди виконання логічних операцій;

- Команди переходу до підпрограм і виходу з них;

- Команди управління і введення-виведення інформації;

- Команди умовного та безумовного переходів;

- Команди пересилки інформації.

Перелік команд і їх короткий опис представлений у Додатку 1.

У Додатку 2 представлений принцип формування коду команди мікропроцесора КР580ВМ80 для представлення його в вісімковій системі числення. Для розуміння принципу формування наведемо приклад: восьмеричний код команди MOV HB - 140, тобто в двійковому коді це 01100000. Старші два розряди двійкового коду D7D6 (01) відповідають команді MOV і з них формується старший розряд восьмеричного коду цієї команди (1); в наступних трьох розрядах D5D4D3 (100) представлений код регістра-приймача (Н) і з них формується середній розряд восьмеричного коду (4); в молодших трьох розрядах D2D1D0 (000) представлений код регістра-джерела (В), а молодший розряд восьмеричного коду дорівнює 0.

1. Порядок виконання роботи

При підготовці до проведення лабораторної роботи необхідно визначити вид команд, відповідних варіанту завдання по табл.9.1, (1, 2-х або 3-х адресна) та їх тип (арифметична, логічна і т.д.).

Запустити програму «Дослідження центрального процесора», ознайомитися з органами управління і індикації, що знаходяться на панелі (див. рис 9.3), натиснувши «Інструкції» на ній.

Таблиця 9.1.

| № варианта

№ команды

|

|

|

|

|

|

|

|

|

|

| |

| ACI

| ADI

| SBI

| SUI

| ACI

| ADI

| SBI

| SUI

| ACI

| ADI

| |

| ADC B

| ADD D

| SBB E

| SUB C

| SBB

D

| SUB B

| ADC E

| ADD H

| SBB D

| SUB L

| |

| ANA B

| ORA D

| XRA E

| ANA C

| ORA H

| XRA L

| ANA H

| ORA B

| XRA D

| ORA C

| |

| CC

| CM

| CNC

| CNZ

| CP

| CPE

| CPO

| CZ

| CP

| CZ

| |

| JC

| JM

| JNG

| JNZ

| JP

| JPE

| JPO

| JZ

| JNG

| JM

| |

| MOV A C

| MOV B E

| MOV C H

| MOV D B

| MOV E L

| MOV H D

| MOV L A

| MOV D C

| MOV B A

| MOV L E

| |

| MVI A

| MVI B

| MVI C

| MVI D

| MVI E

| MVI H

| MVI L

| MVI D

| MVI B

| MVI L

|

Рис. 9.3. Панель дослідження центрального процесора

Таблиця 7.2

| №

команды

| Значение

| № варианта

| |

|

|

|

|

|

|

|

|

|

| |

| В2

|

|

| -45

|

| -101

|

| -98

|

|

| -88

| | В3

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| |

| В2

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| | В3

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| |

| В2

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| | В3

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| |

| В2

|

|

|

|

|

|

|

|

|

|

| | В3

|

|

|

|

|

|

|

|

|

|

| |

| В2

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| | В3

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| |

| В2

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| | В3

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

| |

| В2

|

|

| -45

|

| -101

|

| -98

|

|

| -88

| | В3

| -

| -

| -

| -

| -

| -

| -

| -

| -

| -

|

Начало формы

Відповідно до № варіанту, заданим викладачем ввести по черзі команди з табл. 7.1 і дані (при необхідності) з табл. 7.2. Запустити покрокове виконання введеної команди, простежити стану внутрішніх регістрів МПУ і записати попереднє і поточний стан регістрів МПУ, стан яких змінився в поточному такті виконання команди. По завершенню виконання обраної команди переглянути і замалювати тимчасові діаграми станів шин управління. У висновках відобразити послідовність проходження інформації в процесі виконання кожної з команд, вказаних в табл. 7.1 (по № варіанту).

Введіть одну з команд з переліку табл. 7.1, задати стан сигналу «Готовий» = 0 шини управління, запустити виконання введеної команди в автоматичному режимі, по закінченню 4-5 сек ввести стан сигналу «Готовий» шини управління = 1, по завершенню виконання команди переглянути і замалювати тимчасові діаграми станів шин управління, а у висновках відобразити причину відмінності отриманих діаграм від аналогічних, отриманих при дослідженні цієї ж команди в п. 3.2.

Виконати аналогічні дії п. 3.3, тільки замість стану сигналу «Готовий» змінювати стан сигналу «Захоплення» (перед запуском виконання встановити стан «Захоплення» = 1, а по закінченню 4-5 сек - = 0). Замалювати часові діаграми і зробити відповідні висновки.

Виконати аналогічні дії п. 3.4, тільки замість стану сигналу «Захоплення» змінювати стан сигналу «Запит переривання» (перед запуском виконання встановіть стан «ЗП» = 1). Після появи діалогового вікна, що вимагає введення № пристрою, що викликало переривання, вибрати одне із запропонованих. По завершенню виконання команди замалювати тимчасові діаграми і зробити відповідні висновки.

КОНТРОЛЬНІ ПИТАННЯ

1. З чого складається час виконання команд МП?

2. Що таке «стан МП»?

3. Яким чином вирішується протиріччя між бажаною розрядністю подання даних і обмеженою розрядністю МП?

4. У яких випадках непряма адресація економічніше безпосередній?

5. Структура центрального процесора.

6. Програмно-доступні регістри мікропроцесора КР580ВМ80.

7. Система команд мікропроцесора КР580ВМ80.

8. Особливості виконання арифметичних операцій.

9. Призначення блоку десяткової корекції в мікропроцесорі КР580ВМ80.

10. Сенс і призначення ознак, що встановлюються мікропроцесором КР580ВМ80 в регістрі ознак.

11. Реалізація циклу і звернення до підпрограм.

12. Особливості роботи мікропроцесора КР580ВМ80 при відсутності сигналу «Готовий».

13. Особливості роботи мікропроцесора КР580ВМ80 в режимі «Захоплення шини».

14. Особливості роботи мікропроцесора КР580ВМ80 в режимі обслуговування переривання.

15. Варіанти виходу мікропроцесора зі стану останова.

Vidpovidno do № variantu, zadanym vykladachem vvesty po cherzi komandy z tabl. 7.1 i dani (pry neobkhidnosti) z tabl. 7.2. Zapustyty pokrokove vykonannya vvedenoï komandy, prostezhyty stanu vnutrishnikh rehistriv MPU i zapysaty poperednye i potochnyy̆ stan rehistriv MPU, stan yakykh zminyvsya v potochnomu takti vykonannya komandy. Po zavershennyu vykonannya obranoï komandy perehlyanuty i zamalyuvaty tymchasovi diahramy staniv shyn upravlinnya. U vysnovkakh vidobrazyty poslidovnistʹ prokhodzhennya informatsiï v protsesi vykonannya kozhnoï z komand, vkazanykh v tabl. 7.1 (po № variantu).

Vveditʹ odnu z komand z pereliku tabl. 7.1, zadaty stan syhnalu «Hotovyy̆» = 0 shyny upravlinnya, zapustyty vykonannya vvedenoï komandy v avtomatychnomu rezhymi, po zakinchennyu 4-5 sek vvesty stan syhnalu «Hotovyy̆» shyny upravlinnya = 1, po zavershennyu vykonannya komandy perehlyanuty i zamalyuvaty tymchasovi diahramy staniv shyn upravlinnya, a u vysnovkakh vidobrazyty prychynu vidminnosti otrymanykh diahram vid analohichnykh, otrymanykh pry doslidzhenni tsiyeï zh komandy v p. 3.2.

Vykonaty analohichni diï p. 3.3, tilʹky zamistʹ stanu syhnalu «Hotovyy̆» zminyuvaty stan syhnalu «Zakhoplennya» (pered zapuskom vykonannya vstanovyty stan «Zakhoplennya» = 1, a po zakinchennyu 4-5 sek - = 0). Zamalyuvaty chasovi diahramy i zrobyty vidpovidni vysnovky.

Vykonaty analohichni diï p. 3.4, tilʹky zamistʹ stanu syhnalu «Zakhoplennya» zminyuvaty stan syhnalu «Zapyt pereryvannya» (pered zapuskom vykonannya vstanovitʹ stan «ZP» = 1). Pislya poyavy dialohovoho vikna, shcho vymahaye vvedennya № prystroyu, shcho vyklykalo pereryvannya, vybraty odne iz zaproponovanykh. Po zavershennyu vykonannya komandy zamalyuvaty tymchasovi diahramy i zrobyty vidpovidni vysnovky.

KONTROLʹNI PYTANNYA

1. Z choho skladayetʹsya chas vykonannya komand MP?

2. Shcho take «stan MP»?

3. Yakym chynom vyrishuyetʹsya protyrichchya mizh bazhanoyu rozryadnistyu podannya danykh i obmezhenoyu rozryadnistyu MP?

4. U yakykh vypadkakh nepryama adresatsiya ekonomichnishe bezposeredniy̆?

5. Struktura tsentralʹnoho protsesora.

6. Prohramno-dostupni rehistry mikroprotsesora KR580VM80.

7. Systema komand mikroprotsesora KR580VM80.

8. Osoblyvosti vykonannya aryfmetychnykh operatsiy̆.

9. Pryznachennya bloku desyatkovoï korektsiï v mikroprotsesori KR580VM80.

10. Sens i pryznachennya oznak, shcho vstanovlyuyutʹsya mikroprotsesorom KR580VM80 v rehistri oznak.

11. Realizatsiya tsyklu i zvernennya do pidprohram.

12. Osoblyvosti roboty mikroprotsesora KR580VM80 pry vidsutnosti syhnalu «Hotovyy̆».

13. Osoblyvosti roboty mikroprotsesora KR580VM80 v rezhymi «Zakhoplennya shyny».

14. Osoblyvosti roboty mikroprotsesora KR580VM80 v rezhymi obsluhovuvannya pereryvannya.

15. Varianty vykhodu mikroprotsesora zi stanu ostanova.

Словарь

Конец формы

Література

1. Угрюмов Е.П. Цифровая схемотехника. — С.Пб.: БХВ – Петербург, 2002.

2. Основи цифрових систем / За ред. М.П.Благодатного, В.С. Харченка – Підручник. –Харків: Нац. аерокосмічний ун-т “Харківський авіаційний інститут ”, 2002.

3. В.А. Прянишников. Электроника: Курс лекций. — СПб.: КОРОНА принт, 2000.

4. Бойко В.И. и др. Схемотехника электронных систем. Цифровые устройства. — С.Пб.: БХВ – Петербург, 2004.

Додаток 1.

Команди мікропроцесора КР580ВМ80

| Обозначение

| Код

| Содержание

| Число тактов для выполнения команды. Вектор изменения признаков (Z,S,Q,q,P). Пояснения

| |

|

|

|

| | Арифметические операции

| | АСI

ADI

SBI

SUI

| 316 B2

306 B2

336 B2

326 B2

| A+B2+Q→PA

A+B2→ РА

A-B2-Q→PA

A-B2→ РА

| 7. (+++++). К содержимому РА прибавляется (вычитается) второй байт команды с учетом или без учета переноса (заема), образовавшегося при выполнении предыдущей команды,а результат записывается в РА. Признаки (Z, S, Q, q, P) устанавливаются в соответствии с результатом операции.

| | ADC

ADD

SBB

SUB

| 21X

20 X

23 X

22 X

| A+R+Q→PA

A+R→ РА

A-R-Q→PA

A-R→ РА

| 4 (7). (+++++). К содержимому РА прибавляется (вычитается) с учетом или без учета переноса (заема) содержимое R регистра, номер Х которого указан на третьей позиции кода команды (при Х =6 R — содержимое ячейки памяти, адрес которой указан в регистрах РН и PL, а время выполнения команды увеличивается до7 тактов).

| | DAA

|

| (Десятичная

коррекция А)→РА

| 4. (+++++) Команда DAA позволяет организовать обработку двоично-десятичных чисел за счет коррекции суммы этих чисел, полученной на двоичном сумматоре, путем добавления кода б к старшей и младшей тетрадам в зависимости от их величин и наличия сигналов Q и q.

| | DAD В

DAD D

DAD H

DAD SP

|

| BC+HL→PHL

DE+HL→PHL

HL+HL→PHL

Y+HL→PHL

| 10. (——+——). Два 8-разрядных числа, рассматриваемые как одно 16-разрядное число HL, находящееся в регистрах РН и PL (PHL), складываются с аналогично образованным 16 разрядным числом ВС (DE, или HL, или УС), расположенным в регистрах РВС (РВЕ или PHL или УС), а результат заносится в регистр PHL. В соответствии с результатом операции устанавливается только признак Q, остальные признака остаются без изменений.

| | DCR

INR

| 0Х5

0Х4

| R-l→PR

R+1→PR

| 5 (10). (++—++). Содержимое регистра, номер Х которого указан на второй позиции кода команды, уменьшить (увеличить) на 1 (при Х = 6 R является содержимым ячейки памяти, адрес которой указан в регистрах РН и PL, а время выполнения команды увеличивается до 10 тактов). В соответствии с результатом операции устанавливаются все признаки кроме переноса.

| |

|

|

|

| | DCX B

DCX D

DCX H

DCX SP

SNX B

I NX D

INX H

1NX SP

|

| ВС-1→РВС

DE-l→PDE

HL-1→PHL

Y-l→PY

BC+l→PBC

DE+l→PDE

HL+l→PHL

Y+1→PY

| 5. (—————). Два 8-разрядных числа В и С (D и Е, или Н и L, или УС), рассматриваемые как одно 16-разрядное число ВС (DE, HL или УС), находящееся в регистре РВС (PDE, или PHL, или УС), уменьшаются (увеличиваются) на 1, а результат заносится в регистр РВС {PDE, или PHL, или УС). Образованный парой регистров РВ и PC (PD и РЕ, или РН и PL, или УС).

| | RAL

RAR

|

| 2A+Q→PA

½A+128Q→PA

| 4. (——+——) Триггер переноса и РА объе-диняются в 9-разрядный кольцевой ре-гистр, на котором производится цикличе-ский сдвиг на один разряд влево (вправо). В триггер переноса при сдвиге записывается старший (младший) разряд А.

| | RLC

RRC

|

| Левый циклический сдвиг на РА

Правый цикличес-кий сдвиг на РА

| 4. (——+——). На основе РА образуется 8-разрядный кольцевой регистр, на котором производится циклический сдвиг на один разряд влево (вправо). В триггер переноса и младший (старший) разряд РА записывается старший (младший) разряд A.

| | Логические операции

| | ANA

ORA

XRA

| 24 Х

26 Х

25 Х

| A/\R→PA

AVP→PA

АVР→РА АVР→РА

|  4(7). (++00+). Над кодами А и R, где R—содержимое регистра, номер Х которого указан на третьей позиции команды, вы-полняется поразрядная операция И ( /\ ), ИЛИ( V ) или сумма по модулю 2( V ) (при Х = 6 R — содержимое ячейки памяти, адрес которой указан в регистрах РН и PL, а время выполнения команды увеличивается до 7 тактов). Признаки Q и q устанав-ливаются в 0, а остальные — в соответ-ствии с результатом операции. 4(7). (++00+). Над кодами А и R, где R—содержимое регистра, номер Х которого указан на третьей позиции команды, вы-полняется поразрядная операция И ( /\ ), ИЛИ( V ) или сумма по модулю 2( V ) (при Х = 6 R — содержимое ячейки памяти, адрес которой указан в регистрах РН и PL, а время выполнения команды увеличивается до 7 тактов). Признаки Q и q устанав-ливаются в 0, а остальные — в соответ-ствии с результатом операции.

| | ANI

ORI

XRI

| 346 B2

366 B2

356 B2

| A/\B2→PA

AVB2→PA

АVB2→РА АVB2→РА

| 7. (++00+). Команды отличаются от ко-манд ANA, ORA и XRA тем, что в качес-тве второго операнда берется второй байт В2 команды.

| | СМА

|

|  |

| Поделиться:

|

|

) або два лічильники ИЕ6 (вони забезпечують Клч

) або два лічильники ИЕ6 (вони забезпечують Клч  ).

).

АVР→РА

АVР→РА

4(7). (++00+). Над кодами А и R, где R—содержимое регистра, номер Х которого указан на третьей позиции команды, вы-полняется поразрядная операция И ( /\ ), ИЛИ( V ) или сумма по модулю 2( V ) (при Х = 6 R — содержимое ячейки памяти, адрес которой указан в регистрах РН и PL, а время выполнения команды увеличивается до 7 тактов). Признаки Q и q устанав-ливаются в 0, а остальные — в соответ-ствии с результатом операции.

4(7). (++00+). Над кодами А и R, где R—содержимое регистра, номер Х которого указан на третьей позиции команды, вы-полняется поразрядная операция И ( /\ ), ИЛИ( V ) или сумма по модулю 2( V ) (при Х = 6 R — содержимое ячейки памяти, адрес которой указан в регистрах РН и PL, а время выполнения команды увеличивается до 7 тактов). Признаки Q и q устанав-ливаются в 0, а остальные — в соответ-ствии с результатом операции.