Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Cmp ах,bх ; сравнить ах и bхСодержание книги

Поиск на нашем сайте cmovl ax,bx; если ах < bх, скопировать bх в ах Слова «выше» и «ниже» в таблице 1 относятся к сравнению чисел без знака, слова «больше» и «меньше» учитывают знак.

Таблица 4.1. Разновидности команды CMOVcc

Для обращения порядка байт в 32-битном регистре используется команда: BSWAP <регистр 32>

Биты 0 – 15 меняются местами с битами 16–31. Например: Mov eax,12345678h Bswap eax; теперь в еах находится 78563412h

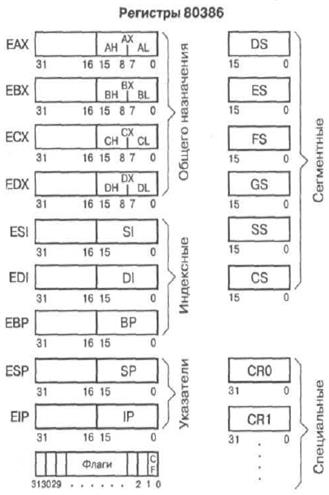

Чтобы обратить порядок байт в 16-битном регистре, следует использовать команду XCHG: xchg al,ah; обратить порядок байт в АХ Регистры архитектуры x86 Регистры архитектуры x86 (Intel 8086, 80186, 80286, 80386, 80486, Pentium'ы и аналоги этих процессоров от других фирм) представлены на рис. 3.1.

Рис. 3.1. Основные регистры процессоров.

Регистры сопроцессора Сопроцессор (FPU) предназначен для выполнения операций над вещественными числами. Восемь регистров данных разрядностью 80 бит организованы в стек. Минимальный размер значения, загружаемого в сопр, - 2 байта/ Регистры данных FPU ( Floating Point Unit - арифметический стек) могут быть представлены в следующем виде:

Расширение MMX (MultiMedia eXtension - мультимединое расширение) MMX было первым расширением, реализующим технологию SIMD (Single Instruction - Multiple Data). Расширение MMX использует новые типы упакованных 64-битные целочисленных данных: - 8 упакованных байт (Packed byte); - 4 упакованных слова (Packed word); - 2 упакованных двойных слова (Packed double word); - 1 учетверенное слово (Quad word);

Каждая инструкция MMX выполняет действие сразу над всем комплектом операндов (8, 4, 2 или 1), размещенных в адресуемых регистрах. Совпадение регистров MMX и FPU накладывает ограничение на чередование кодов FPU и MMX. Можно поместить в MMX-регистр одну 8-байтовую целую переменную и использовать её различными командами, можно поместить две 4-байтные переменные или четыре 2-байтных, или восемь переменных по одному байту и производить над ними операции одновременно. MMX-регистры используются в программах обработки звука и видео, в математических программах, в играх.

Расширение 3DNow! Технология 3DNow!, разработанная AMD, расширяет возможности MMX и разрабатывалась для трёхмерных приложений. Она позволяет оперировать с новым типом данных - парой упакованных вещественных чисел одинарной точности. Технология использует те же регистры, что и MMX, но позволяет помещать в них два 32-битных числа с плавающей точкой. Причём процессор выполнял 2 инструкции 3DNow! за такт, обрабатывая 4 числа с плавающей точкой одновременно

Технология SSE. Блок XMM Начиная с Intel Pentium 3 микропроцессоры снабдили новой технологией SSE (Stream SIMD Extension, потоковое SIMD-расширение) для одновременной обработки чисел с плавающей точкой.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-09-13; просмотров: 690; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.169 (0.006 с.) |