Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Режимы неиспользуемых элементовСодержание книги

Поиск на нашем сайте

Если не все элементы, имеющиеся в корпусе ИС, использованы в схеме, то неиспользованные также подключаются к напряжению питания, которое является общим для всего корпуса. Если же мощности, потребляемые элементами в состояниях нуля и единицы, не равны, то имеет смысл поставить неиспользуемый элемент в состояние минимальной мощности, подав на какой-либо из его входов соответствующую константу. Часть 1. Оптимизация матрицы и построение оптимальной схемы в заданном базисе на базе ЛЭ ТТЛ-серий Задание к части 1. Оптимизировать ЛФ, построить схему в заданном базисе. Использовать логические элементы серий 133, 155, 530, 531, 533, 555, 1533. Справочная информация приведена в Приложении 1. Вариант 1

X(abcd) = ∑ 0,2,4,6,9,10,13,14 Базис “и-не” Вариант 2 X(abcd) = П 1,3,4,6,10,11,12,14,15 Базис “или-не” Вариант 3 X(abcd) = ∑ 0,1,4,5,7,13,15 Базис “и-не” 9,11 – неопределённые условия Вариант 4 X(abcd) = ∑ 0,1,2,3,6,7,8,9 Базис “или-не” 14,15 – неопределённые условия Вариант 5 X(abcd) = П 1,2,3,8,9,10,11 Базис “и-не” 12,13 – неопределённые условия Вариант 6 X(abcd) = П 0,1,4,5,7,9,13,15 Базис “или-не” 11 – неопределённое условие Вариант 7 X(abcd) = ∑ 2,3,8,9,10,11,12 Базис “и-не” 13 – неопределённые условия Вариант 8 X(abcd) = П 1,2,3,5,6,7,9,11,13 Базис “или-не” Вариант 9 X(abcd) = ∑ 0,2,3,6,7,8,9,10,12,13 Базис “и-не” 14 – неопределённые условия Вариант 10 X(abcd) = П 2,3,4,5,6,7,8,10,12,13 Базис “или-не” 0,11 – неопределённые условия Вариант 11 X(abcd) = ∑ 4,5,6,8,10,11,14,15 Базис “и-не” 0,7,9 – неопределённые условия Вариант 12 X(abcd) = П 0,1,2,9,13,14,15 Базис “или-не” 3,5 – неопределённые условия Часть 2. Реализация схемы с тремя выходами в смешанном базисе на ЛЭ ТТЛ-серий Задание к части 2. Построить схему и смоделировать ее работу. Использовать логические элементы ТТЛ - серий 133, 155, 530, 531, 533, 555, 1533. Справочная информация находится в Приложении 1. Вариант 1

Вариант 2

Вариант 3

Вариант 4

Вариант 5

Вариант 6

Вариант 7

Вариант 8

Вариант 9

Вариант 10

Вариант 11

Вариант 12

Часть 3.Реализация ЛФ на базе дешифратора, мультиплексора заданной серии Совершенные формы логических функций можно реализовать с помощью дешифраторов и мультиплексоров. Дешифратор - универсальный преобразователь, при помощи которого выполняется преобразование всех комбинаций n двоичных переменных в один из 2n выходных сигналов, т.е. дешифратор - это операционный узел ЭВМ, выполняющий микрооперацию преобразования двоичного кода в десятичный.

Если V = 1, преобразование не выполняется, выход схемы обнуляется, либо переводится в z-состояние (зависит от серии элемента и его схемотехнической реализации).

Z-состояние характеризуется резким возрастанием сопротивления выходов и, как следствие, логическим отключением выходов схемы от остальных узлов системы.

На приведенной выше схеме функция Х1 является СДНФ наборов 0,4,7, а функция Х2 - СКНФ наборов 2,5,7. Мультиплексор - операционный узел ЭВМ, осуществляющий микрооперацию передачи сигнала с одного из своих информационный входов на один выход.

Для примера рассмотрим реализацию логической функции

На информационные каналы 0, 1, 5 подается постоянная единица, так как функция Х(abc) задана в виде СДНФ. Остальные входы заземляются. При появлении на адресных входах комбинации 000 коммутируется канал d0 с выходом и, следовательно, Х = 1, Задание к части 3. Реализовать заданную функцию на базе одной микросхемы. Справочная информация находится в Приложении 1. Вариант 1 Реализовать ЛФ на базе ИД 3; КП 1

Вариант 2 Реализовать ЛФ на базе ИД 4; КП 12

Вариант 3 Реализовать ЛФ на базе ИД 4; КП 2

Вариант 4 Реализовать ЛФ на базе ИД 4; КП 15

Вариант 5 Реализовать ЛФ на базе ИД 4; КП 12

Вариант 6 Реализовать ЛФ на базе ИД 3; КП 1

Вариант 7 Реализовать ЛФ на базе ИД 4; КП 2

Вариант 8 Реализовать ЛФ на базе ИД 4; КП 15

Вариант 9 Реализовать ЛФ на базе ИД 4; КП 12

Вариант 10 Реализовать ЛФ на базе ИД 4; КП 2

Вариант 11 Реализовать ЛФ на базе ИД 4; КП 15

Вариант 12 Реализовать ЛФ на базе ИД 3; КП 1

Приложение 1 Справочная информация по ИС

Таблица активизированных выходов ИД3

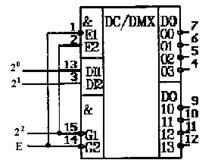

Такая организация входов разрешения позволяет построить на базе этой схемы трёхразрядный дешифратор (демультиплексор 1´8). Для этого объединяют

Таблица истинности КП1

Таблица истинности КП18

Четырехканальный двухразрядный стробируемый мультиплексор с адресным селектором. Серии: 133, 155, 530, 531, 533, 555, 1533 КП2

Таблица истинности для схемы КП2

На базе КП2 можно построить MUX 8:1, объединив входы

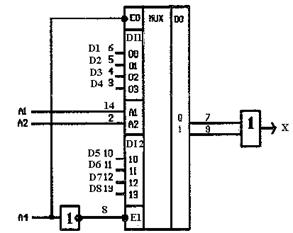

Четырехканальный двухразрядный мультиплексор с адресным селектором и третьим состоянием выхода 531-, 533-, 555-, 1533 КП12 (8—общ., 16—+5 В). Структура ИС за счет раздельного управления выходами DO позволяет преобразовать четырехканальный двухразрядный мультиплексор в одноразрядный восьмиканальный. Для этого разрядные выходы объединяют, а адресный код подают согласно приведенной схеме. Преобразование КП12 в восьмиканальный одноразрядный мультиплексор:

Таблица истинности КП12

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 599; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.133.141.201 (0.01 с.) |

- инверсный вход разрешения. Может обозначаться как

- инверсный вход разрешения. Может обозначаться как  . Если V = 0, схема работает в обычном режиме.

. Если V = 0, схема работает в обычном режиме.

)

Этот вход работает аналогично входу V схемы дешифратора, и может переводить мультиплексор либо в состояние обнуления, либо в z-состояние (зависит от серии элемента и его схемотехнической реализации).

)

Этот вход работает аналогично входу V схемы дешифратора, и может переводить мультиплексор либо в состояние обнуления, либо в z-состояние (зависит от серии элемента и его схемотехнической реализации).

. При поступлении на адресные входы значения 7 (111) коммутируется информационный вход d7 и Х = 0,

. При поступлении на адресные входы значения 7 (111) коммутируется информационный вход d7 и Х = 0,  .

.

=1 выход ИС переводится в состояние высокого импеданса.

=1 выход ИС переводится в состояние высокого импеданса.

вырабатывается при

вырабатывается при  Активным выходным уровнем является низкий. Номер активизируемого выхода определяется в соответствии с таблицей.

Активным выходным уровнем является низкий. Номер активизируемого выхода определяется в соответствии с таблицей.

&

&  =1. Для того чтобы работал дешифратор с выходами 10, 11, 12, 13 должно выполняться условие

=1. Для того чтобы работал дешифратор с выходами 10, 11, 12, 13 должно выполняться условие  &

&  =1.

=1.

для организации входа стробирования.

для организации входа стробирования.  и Е2 используются в качестве старшего разряда 22, DI2-21, и DI1-20 входов дешифратора. DO 00…03, 10…13-восьмиразрядный выход.

и Е2 используются в качестве старшего разряда 22, DI2-21, и DI1-20 входов дешифратора. DO 00…03, 10…13-восьмиразрядный выход.

через инвертор, и используя их в качестве старшего адресного разряда.

через инвертор, и используя их в качестве старшего адресного разряда.