Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Режимы неиспользуемых входовСодержание книги

Поиск на нашем сайте

Теория к выполнению заданий Основными элементами комбинационной логики являются ЛЭ И, ИЛИ, И-НЕ, ИЛИ-НЕ, НЕ. Все эти функции, а также их разновидности сведены в таблицу логических функций двух переменных (a, b):

При построении схемы необходимо учитывать следующие моменты. Разработанная функционально-логическая схема подлежит далее реализации на наборе стандартных ИС той или иной серии или на наборе библиотечных элементов той или иной БИС/СБИС с программируемой структурой. В обоих случаях возможны несовпадения элементов подлежащей изготовлению схемы и имеющихся для ее реализации. Типовыми ситуациями здесь являются наличие у имеющихся элементов "лишних" (неиспользуемых в данном случае) входов, наличие в корпусах ИС лишних элементов или, напротив, нехватка у имеющихся элементов необходимого числа входов или нагрузочной способности. Режимы неиспользуемых входов

Вопрос о режиме "лишних" входов решается с учетом конкретного типа используемой схемотехнологии. Если нужно получить конъюнкцию (или ее инверсию) пяти переменных в стандартной серии, где нет соответствующих элементов с пятью входами, то придется взять элемент с восемью входами, у которого окажется три "лишних" входа. Принципиально возможно поступить следующим образом: не обращать внимания на "лишние" входы (т. е. оставить их разомкнутыми), подсоединить их к задействованным входам или подать на них некоторые константы. С точки зрения логических операций все три возможности правомерны.

На схемах приведены принципиально возможные (а) и рекомендуемые (б) режимы неиспользуемых входов логических элементов, схема формирования сигналов логической единицы (в).

Для КМОП и ТТЛ(Ш) неиспользуемые входы разомкнутыми не оставляют. Для КМОП это строгая рекомендация, т. к. у них очень велики входные сопротивления и, следовательно, на разомкнутые входы легко наводятся паразитные потенциалы, которые могут изменять работу схемы. Для ТТЛ(Ш) строгого запрета на оставление разомкнутых входов нет, однако вследствие этого пострадают параметры быстродействия элемента. Подсоединение "лишних" входов к задействованным для КМОП и ТТЛ(Ш) принципиально возможно, но нежелательно, т. к. оно приводит к увеличению нагрузки на источник сигнала, что также сопровождается уменьшением быстродействия источника сигнала. Таким образом, для КМОП и ТТЛ(Ш) режим неиспользуемых входов — подсоединение их к константам (логическим единицам или нулям), не изменяющим работу схемы для задействованных входов. При этом уровни напряжений U1 и U0 для КМОП совпадают с уровнями Ucc и "земли", к которым и подключают неиспользуемые входы. У элементов ТТЛ(Ш) уровень U1 на 1,5...2 В ниже уровня Ucc, поэтому для предотвращения пробоев неиспользуемые входы подключают к источнику питания Ucc через резисторы R (обычная рекомендация: R = 1 кОм), причем, к одному резистору разрешается подключать до 20 входов. Режимы неиспользуемых элементов

Если не все элементы, имеющиеся в корпусе ИС, использованы в схеме, то неиспользованные также подключаются к напряжению питания, которое является общим для всего корпуса. Если же мощности, потребляемые элементами в состояниях нуля и единицы, не равны, то имеет смысл поставить неиспользуемый элемент в состояние минимальной мощности, подав на какой-либо из его входов соответствующую константу. Часть 1. Оптимизация матрицы и построение оптимальной схемы в заданном базисе на базе ЛЭ ТТЛ-серий Задание к части 1. Оптимизировать ЛФ, построить схему в заданном базисе. Использовать логические элементы серий 133, 155, 530, 531, 533, 555, 1533. Справочная информация приведена в Приложении 1. Вариант 1

X(abcd) = ∑ 0,2,4,6,9,10,13,14 Базис “и-не” Вариант 2 X(abcd) = П 1,3,4,6,10,11,12,14,15 Базис “или-не” Вариант 3 X(abcd) = ∑ 0,1,4,5,7,13,15 Базис “и-не” 9,11 – неопределённые условия Вариант 4 X(abcd) = ∑ 0,1,2,3,6,7,8,9 Базис “или-не” 14,15 – неопределённые условия Вариант 5 X(abcd) = П 1,2,3,8,9,10,11 Базис “и-не” 12,13 – неопределённые условия Вариант 6 X(abcd) = П 0,1,4,5,7,9,13,15 Базис “или-не” 11 – неопределённое условие Вариант 7 X(abcd) = ∑ 2,3,8,9,10,11,12 Базис “и-не” 13 – неопределённые условия Вариант 8 X(abcd) = П 1,2,3,5,6,7,9,11,13 Базис “или-не” Вариант 9 X(abcd) = ∑ 0,2,3,6,7,8,9,10,12,13 Базис “и-не” 14 – неопределённые условия Вариант 10 X(abcd) = П 2,3,4,5,6,7,8,10,12,13 Базис “или-не” 0,11 – неопределённые условия Вариант 11 X(abcd) = ∑ 4,5,6,8,10,11,14,15 Базис “и-не” 0,7,9 – неопределённые условия Вариант 12 X(abcd) = П 0,1,2,9,13,14,15 Базис “или-не” 3,5 – неопределённые условия Вариант 1

Вариант 2

Вариант 3

Вариант 4

Вариант 5

Вариант 6

Вариант 7

Вариант 8

Вариант 9

Вариант 10

Вариант 11

Вариант 12

Вариант 1 Вариант 2 Вариант 3 Вариант 4 Вариант 5 Вариант 6 Вариант 7 Вариант 8 Вариант 9 Вариант 10 Вариант 11 Вариант 12 Приложение 1 Справочная информация по ИС

Таблица активизированных выходов ИД3

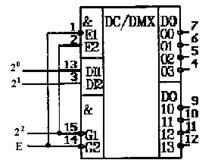

Такая организация входов разрешения позволяет построить на базе этой схемы трёхразрядный дешифратор (демультиплексор 1´8). Для этого объединяют

Таблица истинности КП1

Таблица истинности КП18

Четырехканальный двухразрядный стробируемый мультиплексор с адресным селектором. Серии: 133, 155, 530, 531, 533, 555, 1533 КП2

Таблица истинности для схемы КП2

На базе КП2 можно построить MUX 8:1, объединив входы

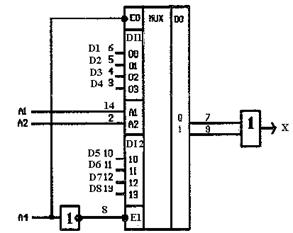

Четырехканальный двухразрядный мультиплексор с адресным селектором и третьим состоянием выхода 531-, 533-, 555-, 1533 КП12 (8—общ., 16—+5 В). Структура ИС за счет раздельного управления выходами DO позволяет преобразовать четырехканальный двухразрядный мультиплексор в одноразрядный восьмиканальный. Для этого разрядные выходы объединяют, а адресный код подают согласно приведенной схеме. Преобразование КП12 в восьмиканальный одноразрядный мультиплексор:

Таблица истинности КП12

Теория к выполнению заданий Основными элементами комбинационной логики являются ЛЭ И, ИЛИ, И-НЕ, ИЛИ-НЕ, НЕ. Все эти функции, а также их разновидности сведены в таблицу логических функций двух переменных (a, b):

При построении схемы необходимо учитывать следующие моменты. Разработанная функционально-логическая схема подлежит далее реализации на наборе стандартных ИС той или иной серии или на наборе библиотечных элементов той или иной БИС/СБИС с программируемой структурой. В обоих случаях возможны несовпадения элементов подлежащей изготовлению схемы и имеющихся для ее реализации. Типовыми ситуациями здесь являются наличие у имеющихся элементов "лишних" (неиспользуемых в данном случае) входов, наличие в корпусах ИС лишних элементов или, напротив, нехватка у имеющихся элементов необходимого числа входов или нагрузочной способности. Режимы неиспользуемых входов

Вопрос о режиме "лишних" входов решается с учетом конкретного типа используемой схемотехнологии. Если нужно получить конъюнкцию (или ее инверсию) пяти переменных в стандартной серии, где нет соответствующих элементов с пятью входами, то придется взять элемент с восемью входами, у которого окажется три "лишних" входа. Принципиально возможно поступить следующим образом: не обращать внимания на "лишние" входы (т. е. оставить их разомкнутыми), подсоединить их к задействованным входам или подать на них некоторые константы. С точки зрения логических операций все три возможности правомерны.

На схемах приведены принципиально возможные (а) и рекомендуемые (б) режимы неиспользуемых входов логических элементов, схема формирования сигналов логической единицы (в).

Для КМОП и ТТЛ(Ш) неиспользуемые входы разомкнутыми не оставляют. Для КМОП это строгая рекомендация, т. к. у них очень велики входные сопротивления и, следовательно, на разомкнутые входы легко наводятся паразитные потенциалы, которые могут изменять работу схемы. Для ТТЛ(Ш) строгого запрета на оставление разомкнутых входов нет, однако вследствие этого пострадают параметры быстродействия элемента. Подсоединение "лишних" входов к задействованным для КМОП и ТТЛ(Ш) принципиально возможно, но нежелательно, т. к. оно приводит к увеличению нагрузки на источник сигнала, что также сопровождается уменьшением быстродействия источника сигнала. Таким образом, для КМОП и ТТЛ(Ш) режим неиспользуемых входов — подсоединение их к константам (логическим единицам или нулям), не изменяющим работу схемы для задействованных входов. При этом уровни напряжений U1 и U0 для КМОП совпадают с уровнями Ucc и "земли", к которым и подключают неиспользуемые входы. У элементов ТТЛ(Ш) уровень U1 на 1,5...2 В ниже уровня Ucc, поэтому для предотвращения пробоев неиспользуемые входы подключают к источнику питания Ucc через резисторы R (обычная рекомендация: R = 1 кОм), причем, к одному резистору разрешается подключать до 20 входов.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 624; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.41 (0.06 с.) |

∙b

∙b

b

b

b

b

)(b

)(b  )

)

=1 выход ИС переводится в состояние высокого импеданса.

=1 выход ИС переводится в состояние высокого импеданса.

вырабатывается при

вырабатывается при  Активным выходным уровнем является низкий. Номер активизируемого выхода определяется в соответствии с таблицей.

Активным выходным уровнем является низкий. Номер активизируемого выхода определяется в соответствии с таблицей.

&

&  =1. Для того чтобы работал дешифратор с выходами 10, 11, 12, 13 должно выполняться условие

=1. Для того чтобы работал дешифратор с выходами 10, 11, 12, 13 должно выполняться условие  &

&  =1.

=1.

для организации входа стробирования.

для организации входа стробирования.  и Е2 используются в качестве старшего разряда 22, DI2-21, и DI1-20 входов дешифратора. DO 00…03, 10…13-восьмиразрядный выход.

и Е2 используются в качестве старшего разряда 22, DI2-21, и DI1-20 входов дешифратора. DO 00…03, 10…13-восьмиразрядный выход.

через инвертор, и используя их в качестве старшего адресного разряда.

через инвертор, и используя их в качестве старшего адресного разряда.