Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Вопрос 20 - программирование и конфигурирование плис. Способы программирования и конфигурирования (конфигурационная микросхема, пассивная последовательная (PS) и JTAG).Содержание книги

Поиск на нашем сайте

1. Configuration Device – Конфигурационная микросхема 2. PS – Пассивная последовательная 3. PPS – Синхронная пассивная параллельная 4. PPA – Асинхронная пассивная параллельная 5. PSA – Асинхронная пассивная последовательная 6. JTAG – Конфигурирование по выводам JTAG Конфигурационная микросхема:

Примечания к рисунку: 1) Подтягивающий нагрузочный резистор подключен к напряжению питания конфигурационной микросхемы. 2) Для микросхем APEX 20KE и APEX 20KC все подтягивающие нагрузочные резисторы имеют номинал 1 кОм (или 10 кОм). Выводы OE и nCS микро- схем EPC16, EPC8, и EPC2 имеют внутренние подтягивающие резисторы, конфигурируемые пользователем. При использовании внутренних подтяги- вающих резисторов, внешние резисторы не используются. 3) Вывод nINIT_CONF есть только у микросхем EPC2, EPC8, и EPC16. Если вывод nINIT_CONF отсутствует (например, у микросхемы EPC1) или не ис- пользуется, то вывод nCONFIG конфигурируемой микросхемы подключает- ся к напряжению питания VCC (непосредственно или через резистор). 4) В микросхемах EPC16, EPC8, и EPC2 вывод nINIT_CONF имеет встроен- ный подтягивающий резистор. При этом внешний резистор на выводе nINIT_CONF не используется. 5) Вывод nCEO не подключается. 6) Для гарантии успешного конфигурирования при возможном разновременном включении питания конфигурируемой (APEX 20KE) и конфигурирующей микросхем, вывод nCONFIG необходимо подтянуть к напряжению VCCINT. 7) В микросхемах EPC16, EPC8, и EPC2 вывод nINIT_CONF имеет встроен- ный подтягивающий резистор номиналом 10 кОм. Вывод nCONFIG конфи- гурируемой микросхемы через резистор 10 кОм необходимо подключить к напряжению питания VCCINT. 8) Для развязки источников напряжения 1,8 В и 3,3 В, при конфигурировании микросхем APEX 20KE, между выводом nCONFIG микросхемы APEX 20KE и выводом nINIT_CONF конфигурирующей микросхемы необходимо включить диод. Пороговое напряжение диода должно быть не более 0,7 В. При этом вывод открытого стока nINIT_CONF может находится либо в со- стоянии "0", либо в третьем состоянии. 9) Микросхемы EPC16, EPC8, и EPC2 не используются для конфигурирования микросхем FLEX 6000.

PS – Пассивная последовательная: В пассивном последовательном режиме конфигурирования (Passive Serial) (PS-конфигурировании) с помощью загрузочного кабеля главный контроллер за- гружает данные из внешнего запоминающего устройства в микросхемы APEX II, APEX 20K, Mercury, ACEX 1K, FLEX 10K, FLEX 6000 через кабель MasterBlaster или ByteBlasterMV. Для начала конфигурирования в этом режи- ме загрузочное устройство обеспечивает изменение уровня сигнала от "0" в "1" на выводе nCONFIG. Программирующая аппаратура затем побитно передает конфигурационные данные на вывод DATA микросхемы (в микросхемах APEX II, APEX 20K, Mercury, ACEX 1K, FLEX 10K используется вывод DATA0, а в микросхемах FLEX 6000 - вывод DATA). Данные синхронно принимаются конфигурируемой микросхемой до момента перехода вывода CONF_DONE в состояние "1". При использовании программирующей аппаратуры для микро- схем APEX II, APEX 20K, Mercury, ACEX 1K, FLEX 10K, FLEX 6000 опция "Auto-Restart Configuration on Frame Error" не влияет на цикл конфигурации, поскольку САПР MAX+PLUS II или QUARTUS II перезапускает конфигуриро- вание при обнаружении ошибки. Схема PS-конфигурирования микросхем ACEX 1K, FLEX 10K с использованием загрузочных устройств MasterBlaster или ByteBlasterMV приведена на рис.:

Примечания к рисунку: 1) Подтягивающий резистор должен быть подключен к тому же напря- жению питания, что и загрузочное устройство MasterBlaster или ByteBlasterMV (вывод VIO), за исключением микросхем APEX 20KE и APEX 20KC. Для микросхем APEX 20KE и APEX 20KC для подтягивания напряжения на выводе nCONFIG до напряжения VCCINT используется резистор 10 кОм. 2) Для микросхем APEX 20KE и APEX 20KC используется подтяги- вающий резистор 10 кОм. 3) Вывод nCEO последней микросхемы в цепочке конфигурирования оставляется неподключенным. 4) Напряжение питания составляет: Для загрузочного устройства MasterBlaster - VCC =3,3 В или 5 В. Для загрузочного устройства MasterBlasterMV VCC = 3,3 В или 5 В. 5) На вывод 6 разъема подается опорное напряжение VIO выходного бу- фера MasterBlaster. Напряжение VIO должно быть согласовано с на- пряжением VCCIO Схема PS-конфигурирования с помощью микропроцессора:

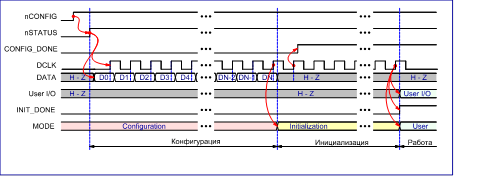

Временные диаграммы при конфигурировании с помощью микропроцессора:

JTAG-программирование: Для загрузки конфигурационных данных в микросхемы может использо- ваться схема JTAG. Объединенная группа по вопросам тестирования (JTAG - Joint Test Action Group) разработала спецификации для периферийного скани- рования (BST – Boundary Scan Test). BST-технология позволяет выполнить эф- фективное тестирование компонентов на прецизионных печатных платах (PCB – Printed Circuit Board). BST-технология может тестировать выводы без исполь- зования щупов и пробников (обычный мультиметр) и выполняет сбор необхо- димых функциональных данных в нормальном режиме функционирования мик- росхемы. Для работы в JTAG -режиме используются четыре выделенных вывода: TDI, TDO, TMS, и TCK, и вспомогательный вывод TRST. Все остальные выво- ды во время JTAG- конфигурирования находятся в третьем состоянии. JTAG- конфигурирование нельзя начинать до завершения других режимов конфигури- рования.

BSC – Ячейки граничного сканирования (Boundary Scan Cells) TDI - Вход тестовых данных (Test data intput) TDO - Выход тестовых данных (Test data output) TMS - Выбор режима тестирования (Test mode select) TCK - Тактовый вход контроллера BST (Test clock input) TRST - Вход прекращения тестирования (Test reset input)

Вопрос 21 -Языки описания аппаратуры. Язык AHDL. Структура проекта текстового описания модуля. Алфавит языка. Строчные и блочные комментарии (назначение, синтаксис, применение). HDL (Hardware Description Language) – язык описания аппаратуры: VHDL (VHSIC HDL, США) (VHD’87; VHD’93. Обновляется через 5 лет) VHSIC (Very High Speed Integrated Circuits) высокоскоростные интегральные схемы Verilog HDL (1989 г. Фирма Gateway > фирма Cadence) AHDL (Altera HDL, фирма Altera, 1983 г.) ABEL (Advanced Boolean Expression Language – Расшир. язык логических выражений, фирмы Xilinx, 1983 г.)

AHDL (язык описания аппаратуры фирмы Altera) является высокоуровневым, модульным языком, полностью интегрированным в систему MAX+PLUS II. Он особенно хорошо подходит для проектирования сложной комбинационной логики, шин, конечных автоматов, таблиц истинности и параметрической логики. Вы можете использовать текстовой редактор системы MAX+PLUS II или любой другой для создания текстовых файлов проектов (AHDL Text Design Files (. tdf)). Затем Вы можете откомпилировать TDF файлы для получения выходных файлов, пригодных для последующего моделирования, временного анализа и программирования устройства. Кроме того компилятор системы MAX+PLUS II может создавать текстовые файлы экспортирования (AHDL Text Design Export Files (. tdx)) и текстовые выходные файлы (Text Design Output Files (. tdo)), которые можно сохранить как TDF файлы и повторно использовать в качестве файлов проекта.

Структура текстового описания модуля: 1. Предварительная секция (Title Statement, Include Statement, Constant Statement, Define Statement, Parameters Statement, Function Prototype Statement, Options Statement, Assert Statement) 2. Интерфейсная (Subdesign Section) 3. Секция переменных (Variable Section) 4. Логическая (Logic Section – Begin/End) Алфавит: 1. Латинские строчные и прописные буквы: A,B,..,Z, a,b,..,z 2. Цифры: 0,1,..,9; 3. Символ подчеркивания «_»; 4. Прямой слеш «/»; 5. Символы «пробел», «табуляция» и «перевод строки»; 6. Ключевые слова; и идентификаторы; 7. Специальные и составные символы; • Из символов пп.1..4 могут создаваться символические имена переменных в программах. • Символы п.5 игнорируются компилятором. • Строчные и прописные буквы не различаются: END, end, End, eNd;

Вопрос 22 - Имена (символические, модуля, вывода) в языке AHDL. Назначение, синтаксис, применение. 1. Символическое имя (<symbolic name>); – внутренние и внешние узлы и группы; – константы; – конечные автоматы, их состояния и биты состояний; – экземпляры примитив и модулей (функций); – параметры; – сегменты памяти; – вычисляемые функции; – именованные операторы. 2. Имя модуля (< subdesign name >, - это имена, которые пользователь определил для файлов проекта более низкого уровня. Имя подпроекта должно совпадать с именем TDF файла); 3. Имя вывода (<port name>, Имена портов - это символьные имена, идентифицирующие входы или выходы логической функции).

Имя может быть задано строкой, содержащей до 32 символов алфавита (пп.1..4) в одной из двух форм: • без кавычек – Unquoted name; (clock, _data, /OE, -clock, node, 74191); • c кавычками – Quoted name; (‘clock’, ‘_data’, ‘/OE’, ‘-clock’, ‘node’, ‘74191’); Замечание: – При создании имен модулей в кавычках и без кавычек нельзя использовать знак "/". В других именах применение этого символа допустимо. – Символ "-", а также ключевые слова нельзя использовать во всех именах без кавычек. В именах с кавычками они допустимы. – Все имена, за исключением символических имен без кавычек могут состоять только из цифр. – Компилятор создает вспомогательные файлы, начинающиеся с символа тильда «~».

|

||||

|

Последнее изменение этой страницы: 2016-08-16; просмотров: 1079; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.12.100 (0.01 с.) |