Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Разработка структурной схемыСодержание книги

Поиск на нашем сайте

ВВЕДЕНИЕ Одним из наиболее актуальных направлений технического прогресса является автоматизация технологических процессов, которая является одним из решающих факторов улучшения качества продукции, повышения производительности и улучшения условий труда. Все существующие и строящиеся промышленные объекты в той или иной степени оснащаются средствами автоматизации. Современные системы программного управления технологическим оборудованием проектируются на основе модульного принципа построения, предусматривающего выполнение всех модулей системы как функционально законченных элементов. При этом необходимо обеспечить функциональную, электрическую и механическую совместимость модулей в системе. Целью курсового проекта является проектирование Модуля ввода/вывода аналоговых, дискретных и импульсных сигналов для интерфейса ISA. В процессе выполнения проекта производится разработка ввода/вывода аналоговых, дискретных и импульсных сигналов. Модули ввода-вывода предназначены для преобразования различных сигналов в цифровую форму и взаимодействия с контроллером через шину данных. Каждый модуль представляет собой съемное интерфейсное устройство. Задачи: · Разработка структурной схемы модуля · Разработка принципиальной схемы модуля на дискретных компонентах · Разработка принципиальной схемы модуля на ПЛИС Данный модуль управляет технологическим оборудованием с характеристиками: 2 аналоговых входа, 1 аналоговый выход, 14 дискретных входов, 14 дискретных выходов

РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ Структурная схема модуля представлена на чертеже КП.2068.998-26-09-00.00.000.Э1. В состав проектируемого модуля входят следующие электронные компоненты: 1. Дешифратор адреса 2. Регистры входные 3. Регистры выходные 4. ЦАП 5. АЦП 6. Счетчики 7. Схема управления 8. Оптогальваническая развязка Назначение структурных блоков Для выбора адресуемых элементов используется дешифратор адреса, выполненный на микросхемах: · "Исключающее ИЛИ" - DD2-DD4, DD7; · "8И-НЕ" -DD5; · "4И-НЕ" -DD6; · дешифратора 3*8 - DD8. В интерфейсе используется 16 разрядная шина адреса. Задание адреса для выбора адресуемых элементов представлено в таблице 1. Таблица 1. Таблица адресов

Где х - задается на этапе разработки программного обеспечения В интерфейсе используется 8 разрядная шина данных. Для ввода 14 дискретных сигналов используются 2 регистра разрядностью 8 бит - микросхемы DD23, DD24. Ввод сигналов осуществляется за 2 цикла. На входы данных регистра RG1 подаются 7 бит данных, оставшиеся 7 бит подаются на входы данных регистра RG2. Обращение к регистрам осуществляется через логический элемент на входы которого подается сигнал с дешифратора адреса (таблица 1) и сигнал IOR с шины управления. С этого же элемента сигнал через схему задержки поступает на линию ответа I/O CH RDY, т. к используется асинхронный обмен. Для вывода 14 дискретных сигналов используются 2 регистра разрядностью 8 бит - микросхемы DD10, DD11. Вывод сигналов осуществляется за 2 цикла. На входы данных регистра RG3 подаются 7 бит данных, оставшиеся 7 бит подаются на входы данных регистра RG4. Обращение к регистрам осуществляется через логический элемент на входы которого подается сигнал с дешифратора адреса (таблица 1) и сигнал IOW с шины управления. С этого же элемента сигнал поступает на линию ответа I/O CH RDY, т. к используется асинхронный обмен. Для коммутации сигналов по уровню используется оптогальваническая развязка. Для ввода импульсных сигналов используется реверсивные асинхронные 4х разрядные счетчики. Т.к. необходимо передавать 16 бит данных, а реализация осуществляется на 4х разрядных счетчиках, используется 4 счетчика - микросхемы DD15-DD18. Данные со счетчиков поступают в два буфера разрядностью 8 бит - DD19-DD20. С буферов данные передаются на шину данных. Обращение к буферам осуществляется через логический элемент на входы которого подается сигнал с дешифратора адреса (таблица 1) и сигнал IOR с шины управления. С этого же элемента сигнал через схему задержки поступает на линию ответа I/O CH RDY, т. к используется асинхронный обмен. Для вывода аналоговых сигналов используются 14 разрядный ЦАП с 1 аналоговым выходом - DD22. Т.к. разрядность шины данных не позволяет одновременно передать все данные на ЦАП, для передачи 8 бит данных используется 8 разрядный регистр - DD12, обращение к которому осуществляется через логический элемент на входы которого подается сигнал с дешифратора адреса (таблица 1) и сигнал IOW с шины управления. С этого же элемента сигнал через схему задержки поступает на линию ответа I/O CH RDY, т. к используется асинхронный обмен. Оставшиеся 6 бит данных подаются непосредственно на входы ЦАП. Обращение к ЦАП осуществляется через логический элемент на входы которого подается сигнал с дешифратора адреса (таблица 1) и сигнал IOW с шины управления. Для ввода аналоговых сигналов используются параллельно-последовательный 12 разрядный АЦП с 2 аналоговым входами - DD21. Обращение к АЦП осуществляется через логический элемент на входы которого подается сигнал с дешифратора адреса (таблица 1) и сигнал IOR с шины управления. Запрос прерывания осуществляется через триггер запроса прерывания - DD40 сигнал с выхода которого поступает на линию запроса прерывания IRQ. Так как в схеме линии шины данных и линии сигналов IOR, IOW, Reset используются несколькими микросхемами необходимо их усилить. Для усиления используются повторитель - микросхемы DD1, DD44. Обозначение микросхем взято чертежа КП.2068.998-26-09-00.00.000.Э3. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ НА ДИСКРЕТНЫХ КОМПОНЕНТАХ Основные особенности Модуль ввода/вывода аналоговых, дискретных и импульсных сигналов разработан на базе микросхем серии КР1533. Маломощные быстродействующие цифровые интегральные микросхемы серии КР1533 предназначены для организации высокоскоростного обмена и обработки цифровой информации, временного и электрического согласования сигналов в вычислительных системах. Микросхемы серии КР1533 обладают минимальным значением произведения быстродействия на рассеиваемую мощность. Описание принципиальной схемы Принципиальная схема модуля представлена на чертеже КП.2068.998-26-09-00.00.000.Э3.

Обозначения элементов представленных на принципиальной схеме приведены в спецификации КП-2068.998-26-09-00.00.000ПЭ. Управление модулем осуществляется на основе стандартных протоколов интерфейса ISA. Используемые сигналы управления: · Сигнал I/OR(I/O Read – чтение устройства ввода/вывода ) активный уровень низкий · Сигнал I/OW(I/O Write – запись в устройство ввода/вывода ) активный уровень низкий · Сигнал RESET DRV (Reset Driver – Сброс Устройства) активный уровень высокий · Сигнал прерывания IRQ. Запрос на прерывание вырабатывается при переходе сигнала с низкого уровня на высокий. Реализуемые процедуры: 1. Чтение данных с регистра 2. Запись данных в регистр 3. Чтение данных с АЦП 4. Запись данных в ЦАП 5. Чтение данных с буфера РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ НА ПЛИС РАСЧЕТ ЭЛЕМЕНТОВ Нагрузочные резисторы R1-R14 предназначены для ограничения тока, протекающего через светодиоды оптопар D25-D31 от источника VCC=+5B. В соответствии с документацией на оптопару К293ЛП6Р [2] ток протекающий через светодиод оптопары IVD= 10 мА, при этом падение напряжения на нем, определяемое по вольтамперной характеристике [4], составляет UVD=1,4 B. Для микросхемы КР1533ИР23 U0=0,4 В [1]. Индикация включенного состояния оптопар выполняется светодиодами VD1-VD14 АЛ307А. При токе IVD= 10 мА напряжение UVD1=2 B Значение нагрузочного резистора определяется по формуле [5]:

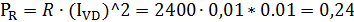

Определим мощность, рассеиваемую на резисторе:

По результатам расчетов выбираем резисторы R1-R14 из ряда E24 [6]: МЛТ 0,063 – 120 Ом ± 5 % Нагрузочные резисторы R15-R28 предназначены для ограничения тока, протекающего через светодиоды оптопар D32-D38 от источника VDD=+24B. В соответствии с документацией на оптопару К293ЛП6Р [2] ток протекающий через светодиод оптопары IVD= 10 мА, при этом падение напряжения на нем, определяемое по вольтамперной характеристике [4], составляет UVD=1,4 B. Значение нагрузочного резистора определяется по формуле [5]:

Определим мощность, рассеиваемую на резисторе:

По результатам расчетов выбираем резисторы R15-R28 из ряда E24 [6]: МЛТ – 0,25Вт – 2,4 кОм ± 5 % Нагрузочный резистор R29 предназначен для ограничения тока, протекающего через светодиод оптопары D39 от источника VDD=+24B. В соответствии с документацией на оптопару К293ЛП1 [2] ток протекающий через светодиод оптопары IVD= 10 мА, при этом падение напряжения на нем, определяемое по вольтамперной характеристике [4], составляет UVD=1,4 B. Значение нагрузочного резистора определяется по формуле [5]:

Определим мощность, рассеиваемую на резисторе:

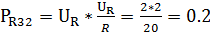

По результатам расчетов выбираем резистор R29 из ряда E24 [6]: МЛТ – 0,25Вт – 2,4 кОм ± 5 % Резисторы R31 – R34, входящие в состав схемы подключения ЦАП D22, заданы производителем в документации на ЦАП [7]: R31=20 Ом, R32=20 Ом, R33=1000 Ом, R34=47000 Ом; Определим мощность, рассеиваемую на резисторах:

По результатам расчетов выбираем резисторы R31- R34 из ряда E24 [6]: МЛТ – 0,25Вт – 20 Ом ± 5 % МЛТ – 0,25Вт – 20 Ом ± 5 % МЛТ – 0,25Вт – 1000 Ом ± 5 % МЛТ – 0,063Вт – 47000 Ом ± 5 % Резистор R37 ограничивают входной ток от источника питания VCC=5B, подключенного к входу управления микросхем DD40. Значение нагрузочного резистора определяется по формуле [1]:

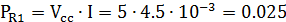

Определим мощность, рассеиваемую на резисторе:

По результатам расчетов выбираем резистор R37 из ряда E24 [6]: МЛТ – 0,063Вт – 1.1 кОм ± 5 % Резисторы R40-R43 ограничивают входной ток от источника питания VCC=5B, подключенного к входу управления микросхем DD15-DD18. Значение нагрузочного резистора определяется по формуле [1]:

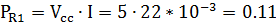

Определим мощность, рассеиваемую на резисторе:

По результатам расчетов выбираем резисторы R40-R43 из ряда E24 [6]: МЛТ – 0,125Вт – 240 Ом ± 5 % Емкость керамических конденсаторов C2, C8, C9, входящих в состав схемы подключения ЦАП D22, задана производителем в документации на ЦАП [7]: С2=33 пФ; С8, С9=0,1 мкФ, Выбираем керамический конденсатор С2 из ряда Е24 [6]: К10 – 17Б – 5B – 33 пФ ± 5 % Выбираем керамические конденсаторы С8, С9 из ряда Е24 [6]: К10 – 17Б – 5B – 0,1 мкФ ± 5 % Емкость электролитического конденсатора C1, входящего в состав схемы подключения ЦАП D22, задана производителем в документации на ЦАП [7]: С1=4,7 мкФ Выбираем электролитический конденсатор С1 из ряда Е24 [6]: К53 – 4 – 6.3В – 4,7 мкФ ± 5 % Резисторы R35, R36, входящие в состав схемы подключения АЦП D21, заданы производителем в документации на АЦП [8]: R35=3000 Ом, R36=5.1 Ом; Определим мощность, рассеиваемую на резисторах:

По результатам расчетов выбираем резисторы R35- R36 из ряда E24 [6]: МЛТ – 0,063Вт – 3000 Ом ± 5 % МЛТ – 0,063Вт – 5.1 Ом ± 5 % Емкость конденсаторов С3, С5– С7 входящих в состав схемы подключения АЦП D21 задана производителем в документации на АЦП [8]: С3, С5, С7 =0.1 мкФ, С6=4.7 мкФ Выбираем керамические конденсаторы С3, С5, C7 из ряда Е24 [6] К10 – 17Б – 5B – 0.1 мкФ ± 5 % Выбираем керамический конденсатор С6 из ряда Е24 [6] К10 – 17Б – 5B – 4,7 мкФ ± 5 % Емкость электролитического конденсатора C4, входящего в состав схемы подключения АЦП D22, задана производителем в документации на АЦП [8]: С4=4,7 мкФ Выбираем электролитический конденсатор С2 из ряда Е24[6]: К53 – 4 – 6,3В – 4,7 мкФ ± 5 % ЗАКЛЮЧЕНИЕ

Тема курсового проекта - «ISA модуль ввода/вывода информации». Модуль построен на базе современных элементов. Основной серией микросхем является КР1533. Разработана принципиальная электрическая схема на базе дискретных компонентов, принципиальная электрическая схема на базе ПЛИС семейства MAX3000A ЕРМ3128АТС144-10. Разработанный модуль имеет следующие характеристики: - 2 аналоговых входа; - 1 аналоговый выхода; - разрядность АЦП 12 бит; - разрядность ЦАП 14 бит; - разрядность шины процессора 8 бит; - 14 дискретных входов; - 14 дискретных выходов; - коммутируемое выходное напряжение 84 В; - коммутируемый ток выходов 4500 мА; - род тока выходов DC - постоянный; - тип входной шины АЦП - ПрПц; - тип выходной шины ЦАП - Пр; - разрядность реверсивного, асинхронного счетчика импульсов - 16; - ДА реализован на микросхемах "Исключающее ИЛИ".

СПИСОК ЛИТЕРАТУРЫ 1. Логические ИС: КР1533б КР1554: справочник в 2 ч. / И.И. Петровский и др.-М.: ТОО "Бином": Фирма "Микаш", 1993 г. - 456 с. 2. Компанейц А. Н. Схемотехника систем управления. Методические указания для выполнения курсового проекта и СРС. Омск: Изд-во ОмГТУ, 2007.- 52 с. 3. Иванов, В.И. и др. Полупроводниковые оптоэлектронные приборы: справочник / В. И. Иванов, А. И. Аксенов, А. М. Юшин. – 2-е изд., перераб. и доп. – М.: Энергоатомиздат, 1988. - 448 с. 4. Компанейц, А. Н. Схемотехника средств автоматизации: конспект лекций / А. Н. Компанейц – Омск: Изд-во ОмГТУ, 2007. – 104 с. 5. Резисторы: справочник / В. В. Дубровский [и др.]; под ред. И. И. Четверткова и В. М. Терехова. – 2-е изд., перераб. и доп. – М.: Радио и связь, 1991. – 528 с. 6. Барнс, Д. Электронное конструирование: Методы борьбы с помехами.:- Перевод с английского. Д. Барнс – Москва: Мир, 1990г, 238стр. 7. http://www.platan.ru 8. http://catalog.gaw. 9. http://www.altera.ru 10. http://www.excode.ru

ВВЕДЕНИЕ Одним из наиболее актуальных направлений технического прогресса является автоматизация технологических процессов, которая является одним из решающих факторов улучшения качества продукции, повышения производительности и улучшения условий труда. Все существующие и строящиеся промышленные объекты в той или иной степени оснащаются средствами автоматизации. Современные системы программного управления технологическим оборудованием проектируются на основе модульного принципа построения, предусматривающего выполнение всех модулей системы как функционально законченных элементов. При этом необходимо обеспечить функциональную, электрическую и механическую совместимость модулей в системе. Целью курсового проекта является проектирование Модуля ввода/вывода аналоговых, дискретных и импульсных сигналов для интерфейса ISA. В процессе выполнения проекта производится разработка ввода/вывода аналоговых, дискретных и импульсных сигналов. Модули ввода-вывода предназначены для преобразования различных сигналов в цифровую форму и взаимодействия с контроллером через шину данных. Каждый модуль представляет собой съемное интерфейсное устройство. Задачи: · Разработка структурной схемы модуля · Разработка принципиальной схемы модуля на дискретных компонентах · Разработка принципиальной схемы модуля на ПЛИС Данный модуль управляет технологическим оборудованием с характеристиками: 2 аналоговых входа, 1 аналоговый выход, 14 дискретных входов, 14 дискретных выходов

РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ Структурная схема модуля представлена на чертеже КП.2068.998-26-09-00.00.000.Э1. В состав проектируемого модуля входят следующие электронные компоненты: 1. Дешифратор адреса 2. Регистры входные 3. Регистры выходные 4. ЦАП 5. АЦП 6. Счетчики 7. Схема управления 8. Оптогальваническая развязка

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-16; просмотров: 324; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.142.198.108 (0.007 с.) |

Ом (1)

Ом (1) Вт (2)

Вт (2) Ом (3)

Ом (3) Вт (4)

Вт (4) Вт (9)

Вт (9) Вт (10)

Вт (10) Вт (11)

Вт (11) Вт (12)

Вт (12) 1625000 Ом = 1.1 кОм

1625000 Ом = 1.1 кОм Вт

Вт 1625000 Ом = 227 Ом

1625000 Ом = 227 Ом Вт

Вт Вт (13)

Вт (13) Вт (14)

Вт (14)