Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Out SPL, TEMP ; завершение инициализации памяти стекаСодержание книги

Поиск на нашем сайте Ldi TEMP, 0x0A; For INT0, INT1 Out MCUCR, TEMP; select falling edge ldi TEMP, 0xC0; Out GICR, TEMP; Enable INT0, INT1 Ldi TEMP, 0x17; 00010111, setting bits for OC1, PB2 and PB4, PB0 Out DDRB, TEMP; set Port B direction as above Ldi TEMP, 0x28; 00101000, PB5 pullup, PB4 lo, PB3 pullup, PB2 lo, OC1 low, Out PORTB, TEMP; set Port B Ldi TEMP, 0xFF; All outputs except bits 0,1 (UART) out DDRA, TEMP; Ldi STATUS, 0x00 Ldi CNTR1, 0x00 Ldi CNTR2, 0x00 rcall LCD_SETUP;; Initialize LCD and send rcall LCD_TXT_READY;; a welcome message Sei FOREVER: Rjmp FOREVER LCD_PRINT_CNTRS: rcall RETURN_CURSOR_4 Mov PARAM, CNTR1 rcall BIN_TO_TEXT Mov PARAM, CNTR2 rcall BIN_TO_TEXT Ret BIN_TO_TEXT: Push PARAM Ldi XL, 0 Ldi XH, 0 DEC_1000: Inc XH Subi PARAM, 10 brpl DEC_1000 Dec XH Tst PARAM brmi BIN_TO_TEXT_NOT_10 Inc XH Ldi XL, 0 rjmp BIN_TO_TEXT_DONE BIN_TO_TEXT_NOT_10: Ldi TEMP, 10 Add PARAM, TEMP Mov XL, PARAM BIN_TO_TEXT_DONE: Ldi TEMP, 0x30 Mov PARAM, XH Add PARAM, TEMP rcall LCD_DATA Mov PARAM, XL Add PARAM, TEMP rcall LCD_DATA Pop PARAM Ret ; ******************************************** ; LCD Driving Library example ; Display setup for 4 bits interface ; LCD_SETUP: Ldi TEMP, 10; Wait about 20msec after powerup SET1:; LCD is a quite slow, rcall WAIT_2M; mind delays! dec TEMP; brne SET1; Ldi TEMP, 0b00101000; Set 4 bit interface (but we are out PORTA, TEMP; still in 8 bits!) Nop nop; Data write cycle must be > 1 ms Cbi PORTA, 3; OE low to clock in data rcall WAIT_2M; ; *******!! From now on, interface is 4 bits!! *** Ldi PARAM, 0b00101000; Send again to catch the bit N rcall LCD_CMD; Display is 2 lines, so N = 1 Ldi PARAM, 0b00001000; Display off, cursor off, and blink off rcall LCD_CMD Ldi PARAM, 0b00000001; Display clear rcall LCD_CMD rcall WAIT_2M; Wait 2 sec after clear Ldi PARAM, 0b00000110; Increment RAM, dont shift display rcall LCD_CMD Ldi PARAM, 0b00001100; Display on, cursor off / blink off rcall LCD_CMD Ret ; ************************** ; ; 2.3 ms delay with 1 MHz clock. ; WAIT_1SEC: Clr DEL2 Dec DEL2; Start at 0xFF W1_2: Dec DELAY2 brne W1_2 Pop TEMP Ret WAIT_2M: Push TEMP Ldi TEMP, 3 Mov DELAY1, TEMP W2_1: Clr DELAY2 Dec DELAY2; Start at 0xFF W2_2: Dec DELAY2 brne W2_2 Dec DELAY1 brne W2_1 Pop TEMP Ret RETURN_CURSOR_4: Push PARAM Ldi PARAM, 0x40 rcall LCD_CURSOR Pop PARAM Ret CURSOR_TO_FIRST_STRING: Push PARAM Ldi PARAM, 0x00 rcall LCD_CURSOR Pop PARAM Ret LCD_TXT_READY: rcall CURSOR_TO_FIRST_STRING ldi ZH, HIGH(2*TXT_READY) ldi ZL, LOW(2*TXT_READY) Rcall L3A Ret LCD_TXT_STARTED: rcall CURSOR_TO_FIRST_STRING ldi ZH, HIGH(2*TXT_STARTED) ldi ZL, LOW(2*TXT_STARTED) Rcall L3A Ret LCD_TXT_PAUSED: rcall CURSOR_TO_FIRST_STRING ldi ZH, HIGH(2*TXT_PAUSED) ldi ZL, LOW(2*TXT_PAUSED) Rcall L3A Ret LCD_TXT_STOPPED: rcall CURSOR_TO_FIRST_STRING ldi ZH, HIGH(2*TXT_STOPPED) ldi ZL, LOW(2*TXT_STOPPED) Rcall L3A Ret L3A: Ldi PARAM, 0x00 rcall LCD_CURSOR L3B: Lpm; From prog mem into R0 Mov PARAM, R0 Tst PARAM Brne L3C Rjmp L4 L3C: rcall LCD_DATA L3D: Adiw ZL, 1; Increment pointer. This neat instruction does Rjmp L3B; w16 bit addition to pointer ZHI:ZLO. L4: Ret; Done TXT_READY: .DB "Press a key to start",0x00 TXT_STARTED: .DB "Stopwatch started ",0x00 TXT_PAUSED: .DB "Stopwatch paused ",0x00 TXT_STOPPED: .DB "Stopwatch stopped ",0x00 ;******************************************************** ; Sends a control function to the display (comes in PARAM) LCD_CMD: Push PARAM Mov TEMP, PARAM Andi PARAM, 0xF0; Mask off lower 4 bits Sbr PARAM, 8; OE bit high (bit 3) Out PORTA, PARAM; Send upper 4 bits to display Nop; Brief delay to give reasonable OE Nop; pulse width Cbi PORTA,3; OE goes low to clock in data Mov PARAM, TEMP; Data back Swap PARAM; Lower 4 bits Andi PARAM, 0xF0 Sbr PARAM, 8; OE high (bit 3, port D) Out PORTA, PARAM; Write lower 4 bits to LCD Nop Nop Cbi PORTA,3; OE clock low Ldi PARAM, 100; 50 usec approx DEL0: Dec PARAM Brne DEL0 Pop PARAM Ret ;******************************************************* ; Sends an ASCII character to the display (comes in PARAM) LCD_DATA: Push PARAM Push TEMP Mov TEMP, PARAM Andi PARAM, 0xF0; Mask off lower 4 bits Sbr PARAM, OE; OE bit high Sbr PARAM, RS; Data/command bit high Out PORTA, PARAM; Write upper 4 bits to display Nop; Brief delay Nop Cbi PORTA, 3; OE low to clock data Swap TEMP; Lower 4 bits Andi TEMP, 0xF0; Masked off Sbr TEMP, OE; OE high Sbr TEMP, RS Out PORTA, TEMP; Lower 4 bits to LCD Nop Nop Cbi PORTA, 3; OE low to clock data Ldi TEMP, 100 Mov DELAY, TEMP; 50 usec DEL1: Dec DELAY Brne DEL1 Pop TEMP Pop PARAM Ret ;********************************************************** ; Moves the LCD display cursor to address specified in PARAM LCD_CURSOR: Ori PARAM, 0x80; MSB specifies address command rcall LCD_CMD Ret Порядок выполнения лабораторной работы

Необходимо выполнить все необходимые операции с проектом Lab_4.prj и программой Lab4.asm в среде VMLab как и в лабораторной работе №1, 2, 3.

Содержание отчета

Отчет по проделанной лабораторной работе должен содержать: - структурную схему алгоритма программы на лабораторную работу; - схему электрическую принципиальную разработанного устройства; - текст программы на языке AVR Ассемблере (распечатка файла *asm); - распечатка файла проекта (*.prj); - результаты моделирования (окно VMLab с запущенной программой и результатами вычислений).

Контрольные вопросы

1. Директивы языка ассемблера AVR. 2. Схемы тактовых генераторов микроконтроллера ATmega16 и их программирование. 3. Источники сброса микроконтроллера ATmega16. 4. Сторожевой таймер микроконтроллера ATmega16. 5. Алгоритм обработки прерываний микроконтроллера ATmega16. 6. Вектора прерываний микроконтроллера ATmega16. 7. Энергонезависимая память данных микроконтроллера ATmega16. 8. Асинхронный обмен данными с микроконтроллером ATmega16.

Лабораторная работа № 5

ПРОГРАММирование в среде Visual Micro Lab в мультипроцессорном режим

Цель работы: Изучение и освоение программирования в мультипроцессорном режиме, а также дальнейшее изучение системы команд и системы прерываний.

Задание к лабораторной работе

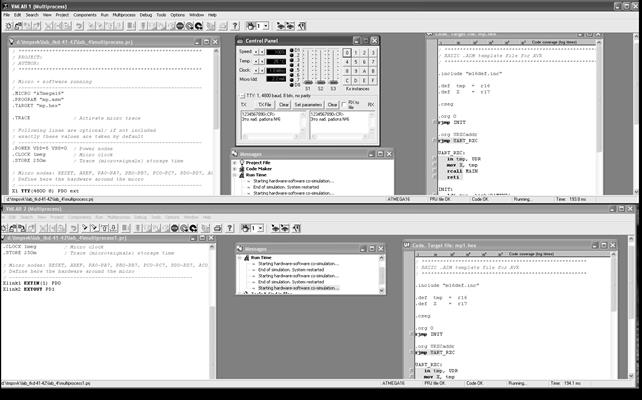

Изучить программы mp.asm, mp1.asm и файлы проекта mp.prj. mp1.prj. Отладить программы в среде VMLab, подключив необходимую периферию к микроконтроллерам AVR – к первому интерфейс ввода, ко второму интерфейс вывода UART. Обмен между микроконтроллерами также через интерфейс UART. Результаты моделирования в мультипроцессорном режиме представлены на рис.23.

Рис.23. Результаты моделирования микроконтроллеров в мультипроцессорном режиме Файл mp. prj ; ************************************************************ ; Micro + software running .MICRO "ATmega16" .PROGRAM "mp.asm" .TARGET "mp.hex" .TRACE; Activate micro trace ; Following lines are optional; if not included ; exactly these values are taken by default .POWER VDD=5 VSS=0; Power nodes .CLOCK 1meg; Micro clock .STORE 250m; Trace (micro+signals) storage time

;nodes: RESET,AREF,PA0–PA7, PB0–PB7, PC0–PC7, PD0–PD7, ACO, TIM1OVF ; –––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– X1 TTY(4800 8) PD0 ext Xlink1 EXTOUT PD1 Xlink2 EXTIN(1) ext Файл mp1.prj ; ************************************************************ .MICRO "ATmega16" .PROGRAM "mp1.asm" .TARGET "mp1.hex" .TRACE; Activate micro trace ; Following lines are optional; if not included ; exactly these values are taken by default .POWER VDD=5 VSS=0; Power nodes .CLOCK 1meg; Micro clock .STORE 250m; Trace (micro+signals) storage time ;nodes:RESET,AREF, PA0–PA7, PB0–PB7, PC0–PC7, PD0–PD7, ACO, TIM1OVF ; –––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– Xlink1 EXTIN(1) PD0 Xlink2 EXTOUT PD1

Файл mp.asm ; ****************************************************** .include "m16def.inc" .def tmp = r16 .def X = r17 Cseg Org 0 Rjmp INIT Org URXCaddr rjmp UART_RXC UART_RXC: In tmp, UDR Mov X, tmp Rcall MAIN Reti INIT: Ldi tmp, high(RAMEND); инициализация памяти стека Out SPH, tmp Ldi tmp, low(RAMEND)

|

||

|

Последнее изменение этой страницы: 2016-08-12; просмотров: 233; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.216 (0.009 с.) |