Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Будовамікроконтролера AT90S2313Содержание книги Поиск на нашем сайте

До складу мікроконтролера входять: 1) генератор тактового сигналу (GCK); 2)процесор (CPU); 3) постійний запам'ятовуючий пристрій для збереження програми виконаний за технологією Flash (FlashROM); 4) оперативний запам'ятовуючий пристрій статичного типу для збереження даних (SRAM); 5) постійний запам'ятовуючий пристрій для збереження даних, виконаний за технологією EEPROM (EEPROM); 6) набір периферійних пристроїв для вводу/виводу даних і керуючих сигналів, і виконання інших функцій. До складу процесора (CPU) входять: 1) лічильник команд (PC); 2) арифметико-логічний пристрій (ALU); 3) блок регістрів загального призначення (GPR, General Purpose Regіsters) і інші елементи. Крім регістрів загального призначення в мікроконтролері є регістри спеціальних функцій, що у сімействі AVR називаються регістрами введення/виведення (І/O Regіsters,IOR). За участю цих регістрів здійснюється: 1)керування роботою мікроконтролера і окремих його пристроїв; 2)визначення стану мікроконтролера і окремих його пристроїв; 3)ввід даних у мікроконтролер й окремі його пристрої, виведення даних і виконуються інші функції. Для нумерації регістрів введення/виведення використовуються номери від 0 до 63 (від $00 до $3F, де $ - показник шістнадцятирічного коду). Кожному регістру присвоєне ім'я, пов'язане з функцією, яку виконує цей регістр. Мікроконтролери різних типів мають різний склад регістрів введення/виведення, при цьому регістри з однаковими номерами можуть мати різні імена. Мікроконтролери сімейства AVR є пристроями синхронного типу. Дії, що виконуються у мікроконтролері, прив'язані до імпульсів тактового сигналу. Генератор тактового сигналу (GCK) використовується, як: 1) внутрішній генератор із зовнішнім кварцовим чи керамічним резонатором (XTAL); 2) внутрішній RC-генератор (ІRC); 3) внутрішній генератор із зовнішнім RC-колом (ERC); 4) зовнішній генератор (ЕХТ). У мікроконтролерів, які мають внутрішній генератор із зовнішнім резонатором (XTAL), резонатор підключається до виводів XTAL1 н XTAL2, що через конденсатори малої ємності (20-30 пФ) з'єднуються із шиною GND. Тактова частота визначається робочою частотою резонатора. XTAL1 і XTAL2 є входом і виходом, відповідно, який інвертує підсилювач, що з використанням кварцового чи керамічного резонатора працює як вбудований генератор, як показано на рис.2. При використанні зовнішнього джерела тактової частоти вивід XTAL2 повинний залишитися вільним, сигнал подається на вивід XTAL1.

Рисунок 1.2 – Внутрішній вигляд мікроконтролера AT90S2313

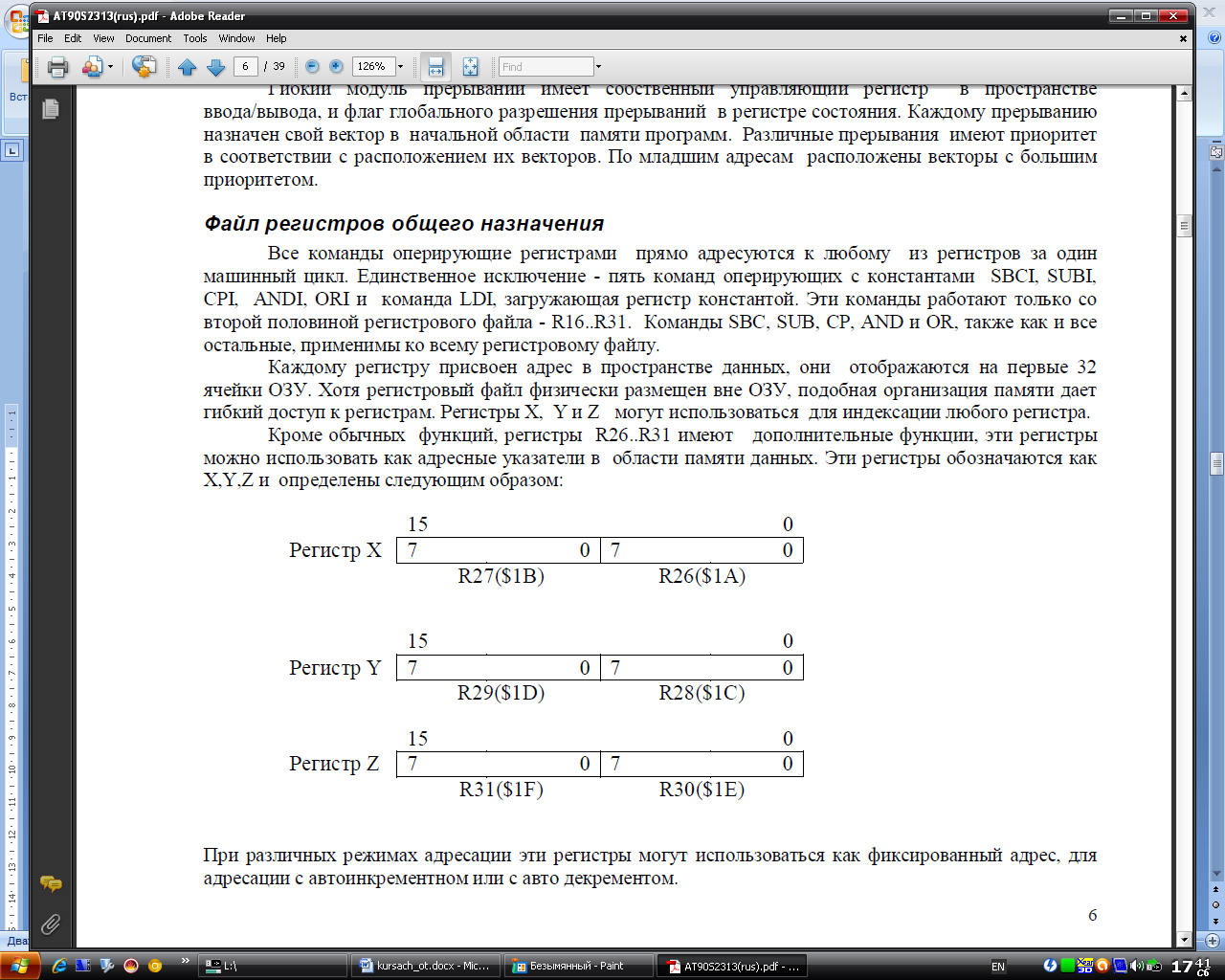

Процесор (CPU) формує адресу наступної команди, вибирає команду з пам'яті й організовує її виконання. Код команди має формат "слово" (16 біт) або "два слова". До складу процесора крім лічильника команд (PC), арифметико-логічного пристрою (ALU) і блоку регістрів загального призначення (GPR) входять: 1) регістр стану мікроконтролера SREG; 2) регістр-показник стека SP або SPL і SPH. ALU з'єднано безпосередньо з усіма 32 швидкодіючими регістрами загального призначення. Операції ALU підрозділяються на три основні категорії: 1) арифметичні 2) логічні 3) операції над бітами Файл регістрів загального призначення Всі команди, оперуючі регістрами, прямо адресуються до будь-якого з регістрів за один машинний цикл. Єдине виключення - п'ять команд оперують з константами SBCI, SUBI, CPI, ANDI, ORI та команда LDI, завантажує регістр константою. Ці команди працюють лише з другою половиною реєстрового файлу - R16.. R31. Команди SBC, SUB, CP, AND і OR, також як і всі інші, застосовані до всього регістрового файлу. Кожному регістру присвоєно адресу в просторі даних, вони відображаються на перші 32 комірки ОЗУ. Хоча регістровий файл фізично розміщений поза ОЗУ, подібна організація пам'яті дає гнучкий доступ до регістрів. Регістри X, Y і Z можуть використовуватися для індексації будь-якого регістра. Крім звичайних функцій, регістри R26.. R31 мають додаткові функції, ці регістри можна використовувати як адресні покажчики в області пам'яті даних. Ці регістри позначаються як X, Y, Z і визначені наступним чином:

Рисунок 1.3 - Додаткові регістри

При різних режимах адресації ці регістри можуть використовуватися як фіксований адрес, для адресації з автоінкрементом або з автодекрементом. Арифметико-логічний пристрій – АЛП АЛП процесора безпосередньо підключено до 32 регістрів загального призначення. За один машинний цикл АЛП виробляє операції між регістрами реєстрового файлу. Команди АЛП розділені на три основні категорії - арифметичні, логічні і бітові.

Статичне ОЗУ даних На рисунку 1.4 показана організація пам'яті даних в AT90S2313:

Рисунок 1.4 - Організація пам'яті даних в AT90S2313

224 комірки пам'яті включають в себе регістровий файл, пам'ять вводу / виводу і статичне ОЗУ даних. Перші 96 адрес використовуються для реєстрового файлу і пам'яті вводу / виводу, наступні 128 - для ОЗУ даних. При зверненні до пам'яті використовуються п'ять різних режимів адресації: прямий, безпосередній зі зміщенням, безпосередній, безпосередній з попередніми декрементом і безпосередній з постінкрементом. Регістри R26.. R31 реєстрового файлу використовуються як покажчики для безпосередньої адресації. Пряма адресація має доступ до всієї пам'яті даних. Безпосередня адресація зі зміщенням використовується для доступудо 63 комірок, базовий адрес яких задається вмістом регістрів Y або Z. Для безпосередньої адресації з інкрементом або декрементом адреси використовуються адресні регістри X, Y і Z. За допомогою будь-якого з цих режимів виробляється доступ до всіх 32 регістрів загального призначення, 64 регістрів введення / виводу і 128 комірок ОЗУ. Покажчик стека SP Цей 8-розрядний регістр з адресою $3D ($5D) зберігає покажчик стека процесора AT90S2313. 8-ми розрядів достатньо, для адресації ОЗУ в межах $60 - $DF.

Таблиця 1.1 - Біти стека

Покажчик стека вказує на область пам'яті в якій розташований стік виклику підпрограм і переривань. Область стека в ОЗУ повинна бути задана до того, як відбудеться будь-який виклик підпрограми, чи будуть дозволені переривання. Покажчик стека зменшується на 1 при запису даних у стек командою PUSH і зменшується на 2 при виклику підпрограми командою CALL, чи обробці переривання. Покажчик стека збільшується на 1 при виборі даних з стека командою POP і збільшується на 2 при виконанні команд повернення з підпрограми або обробника переривання (RET або RETI).

Сторожовий таймер Сторожовий таймер працює від окремого вбудованого генератора працюючого на частоті 1 МГц (це типове значення частоти для живлення 5В). Керуючи попередніми дільником сторожового таймера можна задавати інтервал скидання таймера від 16 до 2048 періодів. Частота вбудованого RC генератора залежить від напруги живлення процесора. Команда WDR скидає сторожовий таймер. Для роботи сторожового таймера можна вибрати одне з 8-ми значень частоти, що дозволяє в широких межах змінювати час між виконанням команди WDR і скиданням процесора. При відпрацюванні періоду роботи сторожового таймера, якщо не надійшла команда WDR, AT90S2313 скидається, виконання програми триває з вектора скидання. Для запобігання небажаного відключення сторожового таймера, для його заборони повинна виконуватися певна послідовність, яка описана при розгляді регістра WDTCR.

Рисунок 1.5 - Регістри керування сторожовим таймером

Біти 7.. 5 - зарезервовані. У AT90S2313 ці біти зарезервовані і завжди читаються як 0. Біт 4 - WDTOE - дозвіл вимикання сторожового таймера. При очищенні біта WDE цей біт повинен бути встановлений (1). Інакше, робота сторожового таймера не припиняється. Через чотири такту після установки цього біта, він апаратно скидається. Біт 3 - WDE-дозвіл сторожового таймера. Якщо біт встановлено (1), робота сторожового таймера дозволена, якщо біт скинуто - заборонена. Скидання біта здійснюється тільки в тому випадку, якщо біт WDTOE встановлений в 1. Для заборони включеного сторожового таймера повинна виконуватися наступна процедура:

1. Однією командою записати 1 в WDTOE і WDE. Одиниця в WDE повинна записуватися навіть у тому випадку якщо цей біт був встановлений перед початком процедури зупинки таймера. 2. Протягом наступних чотирьох тактів процесора необхідно записати в WDE логічний 0, при цьому робота сторожового таймера забороняється. Біти 2.. 0 - WDP2.. 0 - Біти попереднього дільника сторожового таймера. Якщо робота сторожового таймера дозволена, ці біти визначають попередній коефіцієнт розподілу для сторожового таймера. У таблиці наведені різні значення установок попереднього дільника і відповідні їм тимчасові інтервали для напруги живлення Vcc = 5V.

Таблиця1.2 - Установок дільника сторожового таймера

Аналоговий компаратор Аналоговий компаратор порівнює вхідну напругу на позитивному вході PB0 (AIN0) і негативному вході PB1 (AIN1). Коли напруга на позитивному вході більше напруги на негативному, встановлюється біт ACO (Analog Comparator Output). Вихід аналогового компаратора можна встановити на роботу з функцією захоплення Таймера0/Таймера1. Крім того, компаратор може викликати своє переривання. Користувач може встановити спрацьовування переривання по наростаючому або знижувальному фронту, або з переключення.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-01; просмотров: 236; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.191.144.73 (0.008 с.) |