Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Разработка подключения индикатораСодержание книги

Поиск на нашем сайте

Існує безліч різних LCD дисплеїв, але майже всі вони мають один і той же вбудований мікроконтролер HD44780, що дозволяє писати один і той же код для управління різними дисплеями, ми будемо працювати з LCD wh1602b-ygk-ctk.

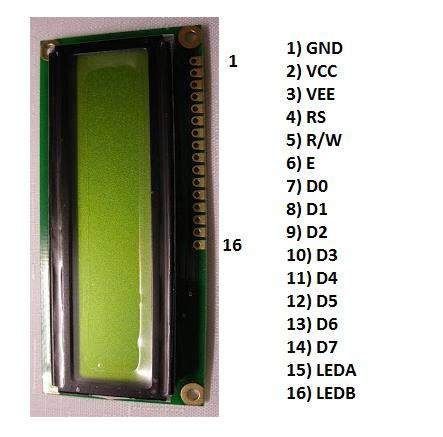

Наш LCD має 4 строки по 16 символів. Для управління РКІ використовується 16 виводів. Призначення виводів: 1) GND - загальний провід. 0 - запис даних в контролер LCD; 1 - читання даних з контролера LCD. 16) LEDB - відповідно Катод. Садимо на загальний провід через 100 Ом.

CGRAM - Це пам'ять де знаходяться символи які наш РКІ може малювати. Привласнюючи значення лічильника АС в області CGRAM ми вибираємо який символ намалювати. А місце де він буде намальований визначається присвоєнням лічильнику АС значення в області DDRAM. Відеопам'ять, що має загальний обсяг 80 байтів, призначена для зберігання кодів символів, що відображаються на РКІ. Відеопам'ять організована в два рядки по 40 символів в кожній. Ця прив'язка є жорсткою і не підлягає зміні. Іншими словами, незалежно від того, скільки реальних рядків

матиме кожен конкретний РКІ-модуль, скажімо, 80х1 або 20х4, адресація відеопам'яті завжди проводиться як до двох рядках по 40 символів.

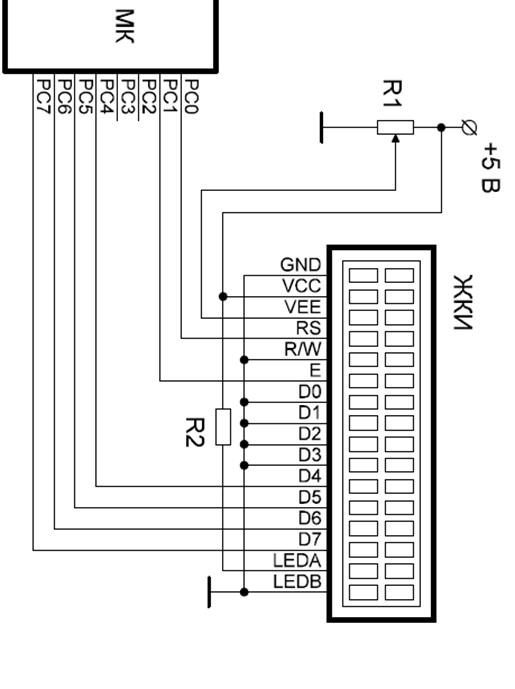

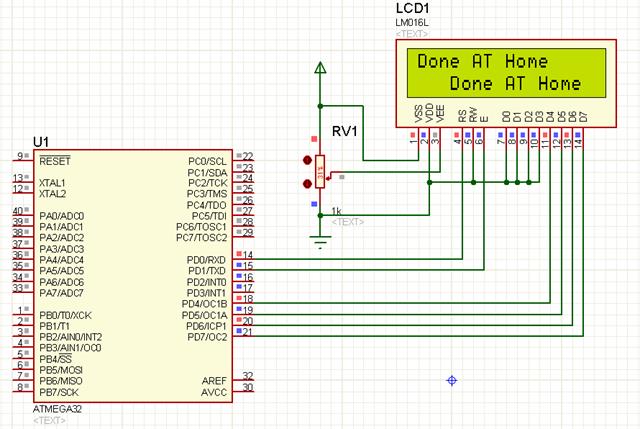

Схема підключення ки до МК

LCD можна підключити декількома способами. З малюнка видно що використовується 4 лінії даних а не 8 що зручно (економія ніжок МК) + ніжка R / W притягнута до загального проводу. Це означає ми будемо записувати команди в LCD без можливості читання від туди. (R1-10ком R2-100ом). Порт може бути будь-яким, в LCD ми передаємо або команду, або символ. Вибір адресується регістра проводиться лінією RS, якщо RS = 0 - адресується регістр команд (IR), якщо RS = 1 - регістр даних (DR).

Блок гальванической развязки

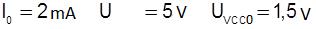

Оптрон вибираємо виходячи з швидкості зміни сигналу. Беремо PC817, так як висока швидкість не потрібна; його швидкість зміни 80 кГц. Діод D1 (ДД4148) потрібен для захисту оптрона від зворотного напруги. Ємність С1 беремо на 10 МF, для того що б транзистор швидше спрацьовував. Вибираємо оптимальний струм рівний 0.01А Блок дискретного вивода

Вихідний блок складемо на основі схеми Дарвінгктона, Як транзистора в ній використовуємо транзистор Т1 - BCX53 (виробництва Philips). Оптрон вибираємо аналогічний, тому, який вибрали у вхідному блоці - PC817.

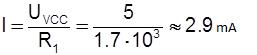

Берем номинальный резистор на 1.7 к Ом. Значит ток будет Рассчитываем мощность резистора

Берем рядовую мощность в 0.25W

Разработка подключения АЦП ATMega16 містить в собі 10-бітовий АЦП, вхід якого може бути з'єднаний з одним з восьми висновків Port A. АЦП Mega16, як і будь-якого іншого АЦП, потрібно опорна напруга для цілей порівняння з вхідним (якщо вимірюється одно опорного, то отримуємо максимальний код в двійковому вигляді). Опорна напруга подається на висновок ADRef або може використовуватися внутрішній генератор з фіксованою напругою 2,65 В. Отриманий результат можна уявити в такому вигляді:

АЦП включається установкою біта ADEN в регістрі ADCSRA. Після перетворення, 10-бітний результат виявляється в 8-бітних регістрах ADCL і ADCH. За замовчуванням, молодший біт результату знаходиться праворуч (тобто в bit 0 регістра ADCL, так зване праве орієнтування). Але порядок проходження бітів на ліве орієнтування можна змінити встановивши біт ADLAR в регістрі ADMUX. Це зручно, якщо потрібно отримати 8-бітовий результат. У такому випадку потрібно прочитати тільки регістр ADCH. В іншому випадку, Ви повинні спочатку прочитати регістр ADCL першим, а ADCH другим, щоб бути впевненим в тому, що читання цих двох регістрів відноситься до результату одного перетворення. Одиночне перетворення може бути викликано записом біта ADSC в регістр ADCSRA. Цей біт залишається встановленим весь час, займане перетворенням. Коли перетворення закінчено, біт автоматично встановлюється в 0. Можна також починати перетворення щодо подій з різних джерел. Модуль АЦП також може працювати в режимі "вільного польоту". В такому випадку АЦП постійно виробляє перетворення і оновлює регістри ADCH і ADCL новими значеннями. Ви зможете конвертувати модулю АЦП необхідна тактова частота. Чим вище ця частота, тим швидше буде відбуватися перетворення (воно, звичайно, займає 13 тактів, перше перетворення займає 25 тактів). Але чим вище частота (і вище швидкість перетворення), тим менш точним виходить результат. Для отримання максимально точного результату, модуль АЦП повинен тактуватися частотою в межах від 50 до 200 КГц. Якщо необхідний результат з точністю менше 10 біт, то можна використовувати частоту більше 200 КГц. Модуль АЦП містить дільник частоти, щоб отримувати потрібну тактову частоту для перетворення з частоти процесора.

Регістр ADMUX задає вхідний контакт порту A для підключення АЦП, орієнтування результату і вибір опорної частоти. Якщо встановлений біт ADLAR, то результат ліво-орієнтований. Опорна частота від внутрішнього генератора задається виставленими в 1 битами REFS1 і REFS0. Якщо обидва біта скинуті, то опорна частота береться від контакту AREF. У разі, якщо REFS1 = 0 а REFS0 = 1, опорна частота береться від AVCC із зовнішнім конденсатором, підключеним до AREF. Вибір контакту введення виконується наступним чином:

Регістр контролю та статусу АЦП ADCSRA:

Біт ADEN = 1 включає модуль АЦП. Запис одиниці в ADSC запускає цикл перетворення. У режимі "вільного польоту" запис одиниці запускає перше перетворення, наступні запускаються автоматично. ADIF - прапор переривання АЦП. Цей біт встановлюється в 1 коли АЦП завершено перетворення і в регістрах ADCL і ADCH знаходяться актуальні дані. Цей прапор встановлюється навіть в тому випадку, якщо переривання заборонені. Це необхідно для випадку програмного опитування АЦП. Якщо використовуються переривання, то прапор скидається автоматично. Якщо використовується програмний опитування, то прапор може бути скинутий записом лог.1 в цей біт. ADIE - Якщо в цьому біті встановлена одиниця, і переривання дозволені глобально, то при закінченні перетворення буде виконано перехід по вектору переривання від АЦП. Біти ADPS2..0 задають коефіцієнти приділитиля частоти:

|

|||||||||||||

|

Последнее изменение этой страницы: 2016-08-01; просмотров: 213; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.147.51.72 (0.01 с.) |