Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

VHDL code for “addersubtractor” unit

VHDL code for “addersubtractor” unit

LIBRARY ieee; USE ieee.std_logic_1164.all; -- Top-level entity ENTITY addersubtractor IS GENERIC (n: INTEGER:= 16); PORT (A, B: IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); Clock, Reset, Sel, AddSub: IN STD_LOGIC; Z: BUFFER STD_LOGIC_VECTOR(n-1 DOWNTO 0); Overflow: OUT STD_LOGIC); END addersubtractor; ARCHITECTURE Behavior OF addersubtractor IS SIGNAL G, H, M, Areg, Breg, Zreg, AddSubR_n: STD_LOGIC_VECTOR(n-1 DOWNTO 0); SIGNAL SelR, AddSubR, carryout, over_flow: STD_LOGIC; COMPONENT mux2to1 GENERIC (k: INTEGER:= 8); PORT (V, W: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); Sel: IN STD_LOGIC; F: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0)); END COMPONENT; COMPONENT adderk GENERIC (k: INTEGER:= 8); PORT (carryin: IN STD_LOGIC; X, Y: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); S: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0); carryout: OUT STD_LOGIC); END COMPONENT; BEGIN PROCESS (Reset, Clock) BEGIN IF Reset = '1' THEN Areg <= (OTHERS => '0'); Breg <= (OTHERS => '0'); Zreg <= (OTHERS => '0'); SelR <= '0'; AddSubR <='0'; Overflow <= '0'; ELSIF Clock'EVENT AND Clock = '1' THEN Areg <= A; Breg <= B; Zreg <= M; SelR <= Sel; AddSubR <= AddSub; Overflow <= over_flow; END IF; END PROCESS; nbit_adder: adderk GENERIC MAP (k => n) PORT MAP (AddSubR, G, H, M, carryout); multiplexer: mux2to1 GENERIC MAP (k => n) PORT MAP (Areg, Z, SelR, G); AddSubR_n <= (OTHERS => AddSubR); H <= Breg XOR AddSubR_n; Z <= Zreg; over_flow <= carryout XOR G(n-1) XOR H(n-1) XOR M(n-1); END Behavior; -- k-bit 2-to-1 multiplexer LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY mux2to1 IS GENERIC (k: INTEGER:= 8); PORT (V, W: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); Sel: IN STD_LOGIC; F: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0)); END mux2to1; ARCHITECTURE Behavior OF mux2to1 IS BEGIN PROCESS (V, W, Sel) BEGIN IF Sel = '0' THEN F <= V; ELSE F <= W; END IF; END PROCESS; END Behavior; -- k-bit adder LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_signed.all; ENTITY adderk IS GENERIC (k: INTEGER:= 8); PORT (carryin: IN STD_LOGIC; X, Y: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); S: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0); carryout: OUT STD_LOGIC); END adderk; ARCHITECTURE Behavior OF adderk IS SIGNAL Sum: STD_LOGIC_VECTOR(k DOWNTO 0); BEGIN Sum <= ('0' & X) + ('0' & Y) + carryin; S <= Sum(k-1 DOWNTO 0); carryout <= Sum(k); END Behavior;

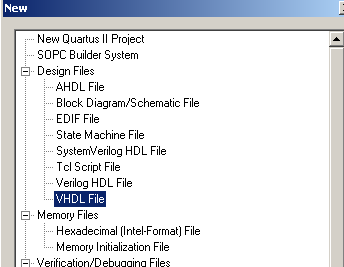

File-> New (ввод текста программы на языке VHDL)

è OK Insert VHDL code (вставить указанную программу)

File-> Save (сохранение введенного текста программы)

Tools -> Options -> Text Editor (выбрать программу редактирования текста)

->OK Assignments -> Settings -> Files (выбор файлов задания и установок),

è OK Processing -> Start Compilation (начать процесс компиляции)

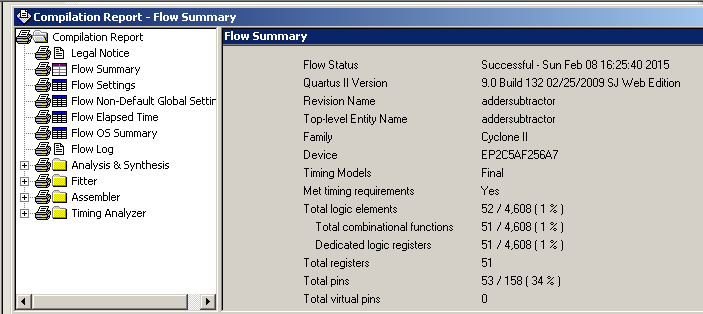

Compilation report (отчет процесса компиляции)

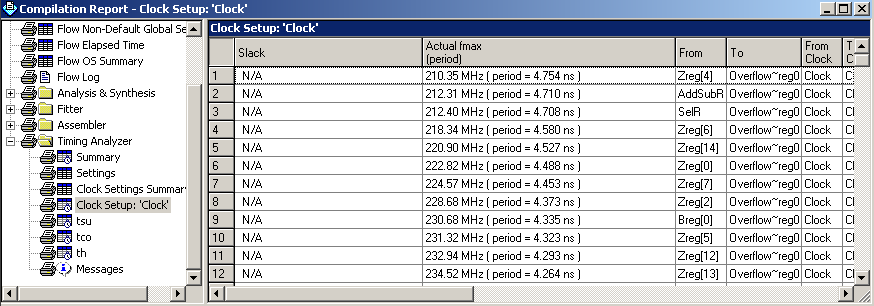

Timing analyzer summary (краткое резюме программы анализа временных диаграмм)

Отчет процесса компиляции – установки тактового генератора

Выбор краткого отчета по Fmax

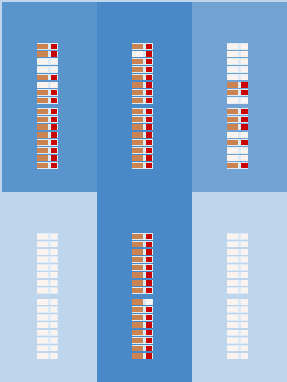

Tools > Chip Planner (Floor Plan and Chip Editor) - выбор программы планирования сединений для выбранного проекта

View of the floor-plan. è

The chip planner tool has several icons that can be used to view aspects such as fan-in and fan-out of nodes, connecting paths between nodes, and so on. For more information on using this tool, refer to Help by selecting Help > Contents > Achieving Timing Closure > Working With Assignments in the Chip Planner from the main Quartus ® II display.

A portion of the expanded view (расширенное поле обзора соединений элементов).

Errors (ввод и устранение ошибок) The user can obtain more information about a specific error or warning message by selecting the message and pressing the F1 function key. 1. To see the effect of an error, open the file “addersubtractor.vhd”.

ARCHITECTURE Behavior OF mux2to1 IS BEGIN PROCESS (V, W, Sel) BEGIN IF Sel = '0' THEN F <= V; ELSE F <= W; END IF; END PROCESS; END Behavior;

Replace F with X in this block. Compile the erroneous design file. Quartus® II software will display a pop-up box indicating that the compilation was not successful. Acknowledge it by clicking OK. The compilation report summary, given in Figure, now confirms the failed result. Correct the error and recompile the design. Предлагается заменить F на X и отправить на компиляцию – ППП Quartus II должен выдать отчет об ошибке. Устраните ошибку и снова запустите на компиляцию.

Using the RTL Viewer Tools > Netlist Viewers > RTL Viewer (программа просмотра Проекта на уровне резисторно-транзисторной логике)

An enlarged view of the circuit (расширенный просмотр схемы Проекта). Details of sub-circuits can be seen by clicking on the box that represents a sub-circuit. Select the Selection Tool

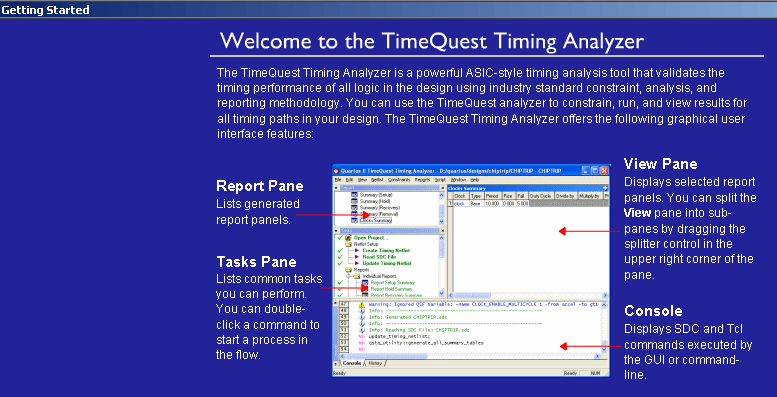

The multiplexer sub-circuit Для расширенного просмотра выбранного элемента схемы выбрать специальную пиктограмму - Tools > TimeQuest Timing Analyzer (выбор программы для анализа временных диаграмм)

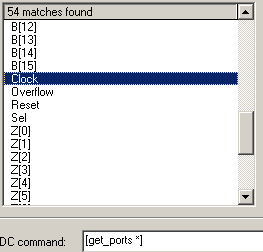

è Netlist -> Create Timing Netlist (выбор таблицы соединений)

Выбрать поле Clock

VHDL code for “addersubtractor” unit

LIBRARY ieee; USE ieee.std_logic_1164.all; -- Top-level entity ENTITY addersubtractor IS GENERIC (n: INTEGER:= 16); PORT (A, B: IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); Clock, Reset, Sel, AddSub: IN STD_LOGIC; Z: BUFFER STD_LOGIC_VECTOR(n-1 DOWNTO 0); Overflow: OUT STD_LOGIC); END addersubtractor; ARCHITECTURE Behavior OF addersubtractor IS SIGNAL G, H, M, Areg, Breg, Zreg, AddSubR_n: STD_LOGIC_VECTOR(n-1 DOWNTO 0); SIGNAL SelR, AddSubR, carryout, over_flow: STD_LOGIC; COMPONENT mux2to1 GENERIC (k: INTEGER:= 8); PORT (V, W: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); Sel: IN STD_LOGIC; F: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0)); END COMPONENT; COMPONENT adderk GENERIC (k: INTEGER:= 8); PORT (carryin: IN STD_LOGIC; X, Y: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); S: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0); carryout: OUT STD_LOGIC); END COMPONENT; BEGIN PROCESS (Reset, Clock) BEGIN IF Reset = '1' THEN Areg <= (OTHERS => '0'); Breg <= (OTHERS => '0'); Zreg <= (OTHERS => '0'); SelR <= '0'; AddSubR <='0'; Overflow <= '0'; ELSIF Clock'EVENT AND Clock = '1' THEN Areg <= A; Breg <= B; Zreg <= M; SelR <= Sel; AddSubR <= AddSub; Overflow <= over_flow; END IF; END PROCESS; nbit_adder: adderk GENERIC MAP (k => n) PORT MAP (AddSubR, G, H, M, carryout);

multiplexer: mux2to1 GENERIC MAP (k => n) PORT MAP (Areg, Z, SelR, G); AddSubR_n <= (OTHERS => AddSubR); H <= Breg XOR AddSubR_n; Z <= Zreg; over_flow <= carryout XOR G(n-1) XOR H(n-1) XOR M(n-1); END Behavior; -- k-bit 2-to-1 multiplexer LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY mux2to1 IS GENERIC (k: INTEGER:= 8); PORT (V, W: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); Sel: IN STD_LOGIC; F: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0)); END mux2to1; ARCHITECTURE Behavior OF mux2to1 IS BEGIN PROCESS (V, W, Sel) BEGIN IF Sel = '0' THEN F <= V; ELSE F <= W; END IF; END PROCESS; END Behavior; -- k-bit adder LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_signed.all; ENTITY adderk IS GENERIC (k: INTEGER:= 8); PORT (carryin: IN STD_LOGIC; X, Y: IN STD_LOGIC_VECTOR(k-1 DOWNTO 0); S: OUT STD_LOGIC_VECTOR(k-1 DOWNTO 0); carryout: OUT STD_LOGIC); END adderk; ARCHITECTURE Behavior OF adderk IS SIGNAL Sum: STD_LOGIC_VECTOR(k DOWNTO 0); BEGIN Sum <= ('0' & X) + ('0' & Y) + carryin; S <= Sum(k-1 DOWNTO 0); carryout <= Sum(k); END Behavior;

File-> New (ввод текста программы на языке VHDL)

è OK Insert VHDL code (вставить указанную программу)

File-> Save (сохранение введенного текста программы)

Tools -> Options -> Text Editor (выбрать программу редактирования текста)

->OK Assignments -> Settings -> Files (выбор файлов задания и установок),

è OK Processing -> Start Compilation (начать процесс компиляции)

Compilation report (отчет процесса компиляции)

Timing analyzer summary (краткое резюме программы анализа временных диаграмм)

|

||||||

|

Последнее изменение этой страницы: 2016-04-26; просмотров: 273; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.219.119.163 (0.01 с.) |

from the left hand toolbar (above the Zoom Tool), and double-click on the mux2to1 box to obtain the image in Figure 30.

from the left hand toolbar (above the Zoom Tool), and double-click on the mux2to1 box to obtain the image in Figure 30.