Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Система команд 8-разрядного МПСодержание книги

Поиск на нашем сайте

Микропроцессор

Микропроцессор – это программно-управляемое электронное цифровое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, выполненное на одной или нескольких интегральных схемах с высокой степенью интеграции электронных элементов. В 1970 году Маршиан Эдвард Хофф из фирмы Intel сконструировал интегральную схему, аналогичную по своим функциям центральному процессору большой ЭВМ – первый микропроцессор Intel-4004, который уже был выпущен в продажу в 1971 году. 15 ноября 1971 года можно считать началом новой эры в электронике. В этот день компания приступила к поставкам первого в мире микропроцессора Intel 4004. МП Intel-4004 размером менее 3 см был производительнее гигантской машины ENIAC. Правда работал он гораздо медленнее и мог обрабатывать одновременно только 4 бита информации (процессоры больших ЭВМ обрабатывают 16 или 32 бита одновременно), но и стоит первый МП в десятки тысяч раз дешевле. Кристалл представлял собой 4-разрядный процессор с классической архитектурой ЭВМ гарвардского типа и изготавливался и изготавливался по передовой p-канальной МОП технологии с проекными нормами по мкм. Электрическая схема прибора насчитывала 2300 транзисторов. МП работал на тактовой частоте 750 кГц при длительности !! Чип i4004 имел адресный стек (счетчик команд и три регистра стека типа LiFO), блок POHов (регистры сверхоперативной памяти или регистровый файл – РФ) , 4-разрядное параллельное АЛУ, аккумулятор, регистр команды с дешифратором команд схемой управления, а также схему связи с внешними устройствами. Все эти функциональные узлы объединялись между собой 4-разрядной ШД. Память команд достигала 4 Кбайт (для сравнения: объем ЗУ миниЭВМ в начале 70-х годов редко превышала 16 Кбайт), а РФ ЦП насчитывала 16 4-разрядных регистров, которые можно было использовать и как 8 8-разрядных. Такая организация POHов сохранена и в последующих МП фирмы Intel. МП 4004 монтировался а пластмассовый или металлокерамический корпус типа !!! всего с 16 выводами.

Классификация микропроцессоров: · По числу больших интегральных схем (БИС) в микропроцессорном комплекте различают микропроцессоры однокристальные, многокристальные и многокристальные секционные. 1974 г. – первый секционный Мп на основе ТДЛДШ. · По виду обрабатываемых входных сигналов различают цифровые и аналоговые микропроцессоры · По характеру временной организации работы микропроцессоры делят на синхронные и асинхронные. · По назначению различают универсальные и специализированные микропроцессоры · По исполнению выделяют автономные и встроенные МП. · По организации структуры микропроцессорных систем различают микро-ЭВМ одно- и многомагистральные · По количеству выполняемых программ различают одно- и многопрограммные микропроцессоры.

Основные характеристики МП · Тактовая частота · Разрядность Разрядность МП обозначается m/n/k и включает: m – разрядность внутренних регистров; n – разрядность шины данных; k – разрядность шины адреса. Например, МП i8o88 характеризуется значениями m/n/k=16/8/20 · Архитектура

Архитектура типового микропроцессора · Арифметика-логическое устройство · Устройство управления · Регистр команд · Счетчик команд · Дешифратор команд

Основные функции МП · Считывание (по адресу) · Дешифрация · Выполнение

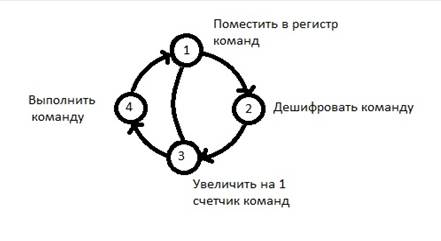

Цикл управления фон Неймана

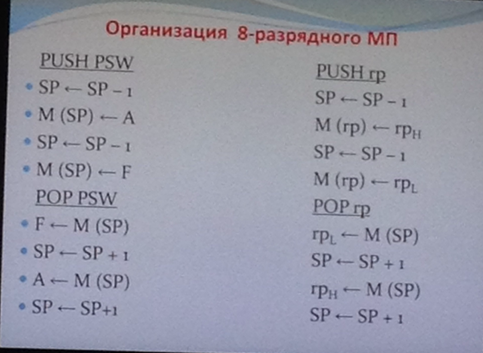

Устройство управления В строгой последовательности в рамках тактовых и цикловых временных интервалов работы микропроцессора (такт – минимальный рабочий интервал, в течении которого совершается одно элементарное действие; цикл – интервал времени, в течении которого выполняется одна машинная операция) осуществляет: · Выборку команды · Интерпретацию ее с целью анализа формата, служебных признаков и вычисление адреса операнда (операндов), установление номенклатуры и временной последовательности всех функциональных управляющих сигналов · Генерацию управляющих импульсов и передачу их на управляющие шины функциональных частей микро-ЭВМ · Анализ результата операции и изменение своего состояния так, чтобы определить месторасположение (адрес) следующей команды Организация 8-разрядного МП

Имеет следующие особенности: · Шинную структуру: ШД, ША, ШУ · Магистральный принцип связи, реализованный в виде связывающего основные устройства МП, двунаправленная восьми разрядная ШД · Наличие регистровой памяти, образованной программно доступными общими и специализированными регистрами (счетчик команд, указатель стека, указатели данных, регистр временного хранения) · Наличие средств в организации в стековой памяти (регистр указателя стека, схема выполнения операций инкрементирования, декрементирования) · Наличие 16 разрядной ША, обеспечивающей возможность прямой адресации любого байта в памяти емкостью 64 Кбайта · Наличие операций над двухбайтными словами (шестнадцати разрядными числами и адресами) · Использование трех форматов команд (1,2,3 байтных и разнообразных способов адресации – прямая, косвенная, непосредственная, стековая или неявная), которые позволяли при коротком восьми разрядном слове иметь достаточно гибкую систему команд · Возможность реализации векторного многоуровнего приоритетного прерывания с использованием БИС контроллера прерывания · Возможность реализации в МП режиме прямого доступа к памяти с использованием БИС контроллера ПДП · Наличие эффективных средств работы с подпрограммами обработки запросов прерывания МП состоит из основных блоков: · Секция регистров и логических устройств их выбора · Арифметико-логический блок (АЛБ) · Регистров команд и устройства управления · Буферы ШД и ША

Секция регистров включает в себя 8 восьми разрядных регистров W, Z, D, C, H, L, E, B, а также шестнадцати разрядный программный счетчик (PC) указатель стека (SP).

Регистры B, C, D, E, H, L – регистры общего назначения – программно доступные, то есть могут быть использованы в программах: 1. Для хранения данных как отдельные восьми разрядные регистры 2. Для хранения адресов как 3 - 16 разрядные регистры BC(B), DE(D), HL(H). Буферные регистры W, Z используются для кратковременного подключения при кратковременном хранении операндов (при выполнении команд условных и безусловных переходов). Они являются программно недоступными (пример: дешифрующее устройство, количество входов и выходов связаны соотношением

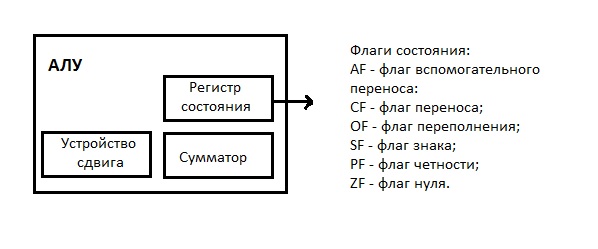

Микропроцессор, регистры, числа с которыми работаем – 8 разрядные Адрес (регистр адреса) – 16 разрядный Счетчик команд PC формирует адреса ячеек памяти, к которым обращается программа или подпрограмма. При выполнении линейных программ содержимое PC автоматически увеличивается на длину команды. Команды условных и безусловных переходов, вызовов программ обслуживания прерывания и различных подпрограмм фактически обеспечивают загрузку адреса точки перехода или начала вызываемой программы (подпрограммы) в PC. Указатель стека SP –используется для организации работы со стековой памятью, организуемой в ОЗУ. Стек представляет собой группу последовательно ячеек памяти, снабженных указателем стека, в котором автоматически при записи и считывании устанавливается адрес последней занятой ячейки стека (вершины стека). При операции занесения в стек слово помещается в следующую по порядку свободную ячейку стека, а при считывании из стека – извлекается последнее поступившее в него слово. Таким образом, в стеке реализуется дисциплина обслуживания «последний пришел – первый ушел». В МП используется «перевернутый» стек, то есть при передаче в стек слово значение указателя стека (адрес вершины стека) уменьшается, а при извлечении слова из стека – увеличивается. Непосредственно в МП из оборудования стековой памяти держится только указатель стека и соответствующие цепи управления. Арифметико-логический блокпредназначен для выполнения арифметических и логических операций. Он включает в себя аккумулятор (А), буфер аккумулятора (БФА), 8-разрядное АЛУ, блок десятичной коррекции, 8-разрядны регистр признаков (РгП) и буферны регистр (БРг). Аккумуляториспользуется в качестве источника одного из операндов и места, где фиксируется результат операции. В командах аккумулятор в явном виде не адресуется – на его использование в операции неявно указывает на операцию. АЛУ предназначено для выполнения арифметических операций сложения и вычитания, а также основных логических операций (И, ИЛИ, НЕ, исключающее ИЛИ) и сдвига. По результату выполнения операций в АЛУ, в пяти разрядах (флажках) C, AC, S, Z и P регистра признаков устанавливается «1» или «0».

S Z AC P C

· Признак переноса C=1, если при выполнении команд появляется «1» переноса из старшего разряда; · Дополнительный признак переноса AC=1, если при выполнении команд возникает «1» переноса из третьего разряда в четвертый числа при обработке двоично-десятичных чисел. При этом состояние разряда может быть проанализировано лишь командой десятичной коррекции числа. · Признак знака S=1, если число отрицательное · Признак нулевого результата Z=1, если при выполнении команды количество единиц в разрядах результата будет четным · Содержимое разрядов признаков не изменяется при выполнении команд пересылки и команд ввода/вывода.

Регистр РгК и дешифратор ДшК командиспользуются в МП для получения и дешифрации кода команды. При извлечении команды первый байт, всегда содержащий код предписанной к выполнению операции, помещается в РгК и поступает на дешифрацию в ДшК. После дешифрации определяется число байт в команде, время выполнения команды и тип выполняемой операции. Перечисленные данные необходимы МП для своевременного формирования синхронизирующих и управляющих сигналов, обеспечивающих взаимодействие всех устройств МП и МПС для выполнения данной команды. Дешифратор совместно с УУ формирует синхронизированные с Ф1 и Ф2 управляющие сигналы для всех внутренних блоков МП, а также выходные сигналы управления и состояния, выдаваемые а ШУ. Двунаправленный буфер ШД предназначен для логического и электрического разделения внутрипроцессорной магистрали и внешней, системной, ШД. Буферная схема ША – однонаправленная, обеспечивает передачу адресов команд и данных, а также номеров внешних устройств от МП в систему. Обмен информацией между МП и ВУ (внешнее устройство) организуется с помощью ША, ШД и ШУ. ША представляет собой совокупность 16 однонаправленных выходов А15 – А0. Информация о текущем адресе выполняемой команды выставляется и сохраняется на ША в начале каждого машинного цикла. ШД содержит восемь выводов D0 – D7 и является двунаправленной. В зависимости от типа выполняемых операций информация может считываться с ШД в процессор или поступать из процессора на входы ОП или УВВ б ШУ предназначена для передачи управляющих сигналов, признаков состояния процессора и периферийного оборудования.

Команды сравнения 8-разрядных операндов выполняются с помощью команд вычитания без фиксирования результата в аккумуляторе, то есть сами операнды при выполнении этих команд не изменяются. Это позволяет производить многократное сравнение содержимого акумулятора с различными операндами. Изменеение флагов Sy и Cy этими командами в регистре используются командами условной передачи управления для изменения порядка выполнения программы.

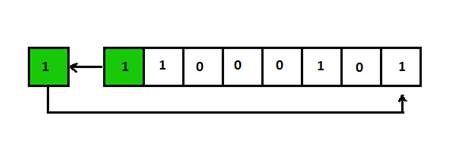

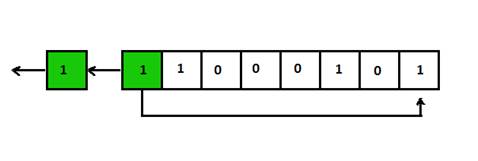

· Команды сдвига на один разряд влево RLC и RAL или вправо RRC и RAR производдятся над содержимым аккумулятора, с участием флага Cy. Эти команды позволяют реализовать программное выполнение операции деления или умножения. Пример: команда циклический сдвиг влево

Пример: команда простого сдвига влево

Пропущенная лекция

· Группа команд передачи управления Выборка команд программы производится из последовательных ячеек памяти в порядке возрастания их адресов при выполнении всех команд, кроме оманд передачи управления JMP, JCond, CALL, CCond, PCHL, R T, RCond, RST n. Данные команды используются для изменения последовательности выборки команд из памяти. Некоторые из них используют флаги регистра признака F, для условных передач управления. При выполнении условия зафиксированного во флаге регистра признаков F, производится передача управления по адресу, указанному в команде, а при невыполнении условия происходит переход к выполнению следующей команды.

Cond · NZ · Z · NC · C · PO · PE · P · M

Результат операции при передаче управления Не нуль (Z=0) Нуль (Z=1) Нет переноса (C=0) Перенос (C=1) Нечетность (P=0) Четность (P=1) Плюс (S=0) Минус (S=01

Команды JNZ, CNZ,RNZ JZ, CZ, RZ JNC, CNC, RNC JC, CC, RC JPO, CPO, RPO JPE, CPE, RPE JP, RP, CP JM, CC,RM

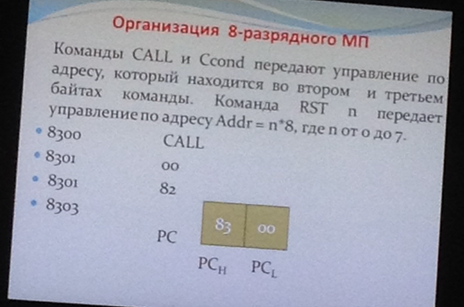

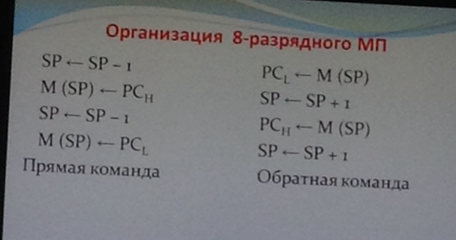

В таблице приведены команды условной передачи управления. Они содержат мнемонку cond, которая заменяется в командах на языке Assembler на мнемонику в соответствии с таблицей. JMP Addr, JCond Addr – это команды безусловных и условных переходов, которые задают переход на выполнение команды, расположенной по адресу Addr, которая находится во втором и третьем байтах команды. Эти команды обеспечивают ветвление программ, способ адресации при этом прямой. Команды безусловного перехода PCHL позволяют загрузить содержимое HL в счетчик команд PC, что приводит к выборке следующей команды, находящейся по адресу загрузить содержимое HO в счетчик команд PC, что приводит к выборке следующей команды, находящейся по адресу задаваемого содержимым регистров H и L. Команды вызова подпрограмм CALL, Ccond, RST n используются для вызова программ.

SP-stec pointer указатель стека (формируется адрес последнего занесенного в стековую память) Вершина стека – само число, которое занесли.

Команды возврата из подпрограммы Ret и Rcond заканчивают выполнение подпрограммы и передают управление на команду, непосредственно следующую за командой вызвавшей переход к этой подпрограмме. Подпрограммы могут содержать и команды условного возврата Rcond, досрочно прекращающих и выполнение при реализации данного условия. Подпрограммы могут иметь любое число уровней вложенности. Ограничивающим фактором является размер стека. Группа команд управления стеком, вводом/выводом и состояния МП Команды PUSH PSW, PUSH rp, POP PSW, POP rp, включает в стек два байта содержащихся в PSW=A+F или регистровых пар ro=BC, DE, HE, HL, адрес памяти содержатся в указателе стека (SP), который автоматически дважды декрементируется при выполнении команды PUSH и инкрементируется дважды при выполнении команды POP.

Ошибка где push rp M(sp)-SPh M(SP)-SPl

Команды ввода in port и вывода out port обеспечивают связь МП с внешними устройствами. Команда HLT устанавливает режим остановок П, выйти из которого он может только призапросе прерывания от внешнего устроства.

|

||||

|

Последнее изменение этой страницы: 2024-06-17; просмотров: 5; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 13.59.35.116 (0.007 с.) |

)

)