Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Тема 5.4. Современные последовательные интерфейсы. USB. Интерфейс Fire Ware .

План · Шина USB. · Организация. · Модель передачи данных. · Протокол. · Типы передачи данных. · Электрический интерфейс. · Применение шины. · Шина Fire Ware. · Физический уровень сети. · Протокол IEEE 1394.

Шина USB USB (Universal Serial Bus – универсальная последовательная шина) является промышленным стандартом расширения архитектуры РС, ориентированным на интеграцию с телефонией и устройствами бытовой электроники. Впервые опубликована шина USB версии 1.0. в 1996г. Весной 2000г. опубликована спецификация USB 2.0., к которой предусмотрено 40-кратное повышение пропускной способности шины. Первоначально (в версии 1.0. и1.1.) шина обеспечивала две скорости передачи информации: полную – 12 Мбит/с и низкую – 1,5 Мбит/с. В версии 2.0. определена еще и высокая скорость – 480 Мбит/с, которая позволяет существенно расширить круг устройств, подключаемых к шине. В одной и той же системе могут присутствовать и одновременно работать устройства со всеми тремя скоростями. Шина позволяет соединять устройства, удаленные от компьютера на расстояние до 25 метров (с использованием промежуточных хабов). USB обеспечивает обмен данными между хост-компьютером и множеством периферийных устройств. Согласно спецификации USB, устройства могут являться хабами, функциями или их комбинацией. Хаб только обеспечивает дополнительные точки подключения устройств к шине. Устройство – функция USB предоставляет системе дополнительные функциональные возможности, например: подключение к ISDN, цифровой джойстик, акустические колонки с цифровым интерфейсом и др. Комбинированное устройство, реализующее несколько функций, представляется как хаб с подключенными к нему несколькими устройствами. Работой всей системы USB управляет хост-контроллер, являющийся программно-аппаратной подсистемой хост-компьютера. Шина USB является хост-центрической: единственным ведущим устройством, которое управляет обменом, является хост-компьютер, а все присоединенные к ней периферийные устройства – исключительно ведомые. Физическая топология шины USB – многоярусная звезда. Ее вершиной является хост-контроллер. Хаб является устройством разветвлителем. Кроме того, он может являться источником питания для подключенных к нему устройств.

Литература Основная 1. Калабеков Б.А. Цифровые устройства и Интерфейсы переферийных устройств. – М.: Горячая линия-Телеком, 2005. – 336 с.: ил. 2. Интерфейсы переферийных устройств / Под ред. Д.В. Пузанкова. – СПб.: Политехника, 2003. – 935 с.: ил. Дополнительная 1. Бройдо В.Л. Вычислительные системы, сети телекоммуникации. - СПб.: Питер, 2005. – 568 с. 2. Хамахер К. Организация ЭВМ. – СПб.: Питер, 2003. – 848 с.: ил.

Лекция 1 2 Тема 5.5. Шина ISA. Шина PCI. План · Шины ISA и EISA. · Принципы построения. · Скорость обмена информацией. · Электрические интерфейсы. · Назначение контактов разъема. · Шина PCI. · Протокол шины. · Таймеры, задержки и буферы. · Команды шины и адресация. · Прерывания. · Электрический интерфейс.

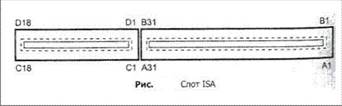

Шина ISA ISABus (Industry Standard Architecture) - шина расширения, применяется с первых моделей РС и ставшая промышленным стандартом. В компьютере ХТ использовалась шина с разрядностью данных 8 бит и адреса - 20 бит. В компьютерах АТ ее расширили до 16 бит данных и 24 бит адреса. В таком виде она существует и поныне. Конструктивно, как показано на рисунке, шина выполнена в виде двух щелевых разъемов с шагом выводов 2,54 мм (0,1 дюйма). Подмножество ISA-8 использует только 62-контактный слот (ряды А. В), в ISA-16 применяется дополнительный 36-контактный слот (ряды С, В). С появлением 32-битных процессоров делались попытки расширения разрядности шины, но все 32-битные шины ISA не являются стандартизованными, кроме ЕISA. Шина РС/104, разработанная для встраиваемых контроллеров на базе РС, отличается от обычной ISA только конструктивно.

Для шины ISA выпущено (и продолжает выпускаться) огромное количество разнообразных карт расширения. Ряд фирм выпускает карты-прототипы, представляющие собой печатные платы полного или уменьшенного формата с крепежной скобой. На платах установлены обязательные интерфейсные цепи - буфер данных, дешифратор адреса и некоторые другие. Остальная часть платы свободна, и здесь разработчик может разместить макетный вариант своего устройства. Эти платы удобны для проверки нового изделия, а также для монтажа единичных экземпляров устройства, когда разработка и изготовление печатной платы нерентабельно.

Шина ISA обеспечивает возможность обращения к 8- или 16-битным регистрам устройств, отображенным на пространства ввода-вывода и памяти, непосредственно доступные по командам центрального процессора. Диапазон адресов памяти для устройств ограничен областью верхней памяти UМА (А0000-FFFFFh), поскольку ниже и выше находится ОЗУ расположенное на системной плате. Для шины ISA-16 настройками СМОS Setap может быть разрешено пространство между 15-м и 16-м мегабайтом памяти (при этом компьютер не сможет использовать более 15 Мбайт ОЗУ). Процессоры х86 при адресации портов ввода-вывода используют только 16 разрядов адреса, так что максимально возможный диапазон адресов ввода-вывода - 0000-FFFFh. Для шины ISA диапазон адресов ввода-вывода сверху ограничен количеством задействованных для дешифрации бит адреса, нижняя область адресов 0-FFh недоступна (зарезервирована под устройства системной платы). В РС была принята 10-битная адресация ввода-вывода, при которой линии адреса А[15:10] устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100h—3FFh, то есть всего 758 адресов 8-битных регистров. На некоторые из адресов претендуют стандартные устройства (см. п. 3.3). Впоследствии стали применять 12-битную адресацию (диапазон 100h—FFFh). При ее использовании приходится учитывать возможность присутствия на шине старых 10-битных адаптеров, которые “отзовутся” на адрес с подходящими ему битами А[9:0] во всей допустимой области 12-битного адреса четыре раза (у каждого 10-битного адреса будет еще по три 12-битных псевдонима). Полный 16-битный адрес используется только в шинах Е ISA и РСI. Шина ISA -8 может предоставить до 6 линий запросов прерываний, ISA-16 - 11. Часть из них могут -«отобрать» устройства системной платы или шина РС1. Шина 18А-8 позволяет использовать до трех 8-битных каналов ВМА. На 16-битной шине доступны еще три 16-битных и один 8-битный канал. В каждый момент времени шиной может управлять только одно устройство-задатчик, обращающееся к ресурсам (портам или ячейкам памяти) устройств-исполнителей. Основным задатчиком является контроллер шины, расположенный на системной плате. Он формирует запросы к исполнителям по командам обращения к памяти или вводу-выводу, выполняемым центральным процессором по сигналам контроллера DМА и контроллера регенерации памяти. Задатчиком на некоторое время может стать устройство, захватившее управление шиной через запрос по 16-битному каналу DМА. Такой режим работы устройства называют прямым управлением шиной. При этом канал DМА применяется для арбитража шины, а адаптер bus-master формирует все адресные и управляющие сигналы шины, не забывая передать управление шиной процессору не позднее, чем через 15 мкс (чтобы не нарушить регенерацию памяти). Вес перечисленные ресурсы шины должны быть бесконфликтно распределены. Бесконфликтность подразумевает выполнение следующих условий.

• Каждое устройство-исполнитель должно управлять шпион данных только при чтении по его адресам или но используемому им каналу DМА. Области адресов, по которым выполняется чтение регистров различных устройств, не должны пересекаться. Поскольку при записи тиной данных управляет лишь текущий задатчик, возможность конфликтов, приводящих к искажениям данных, исключена. «Подсматривать» операции записи, адресованные не данному устройству, не возбраняется. • Назначенную линию IRQx или DRQx устройство должно держать на низком уровне в пассивном состоянии и переводить в высокий уровень для активации запроса. Неиспользуемыми линиями запросов устройство управлять не имеет права, они должны быть электрически откоммутированы или подключаться к буферу, находящемуся в третьем состоянии. Одной линией запроса может пользоваться только одно устройство. Такая нелепость (с точки зрения схемотехники ТТЛ) была допущена в первых РС и из требований совместимости тиражируется до сих пор. Задача распределения ресурсов для старых адаптеров решалась с помощью джамперов, затем подвились программно конфигурируемые устройства, которые вытесняются автоматически конфигурируемыми платами РnР. Прямой доступ к памяти позволяет абоненту шины организовывать обмен данными между своим регистром и памятью под управлением контроллера DМА, минуя центральный процессор. До выполнения обмена канал DМА должен быть инициализирован - задан начальный адрес и размер пересылаемого блока памяти, направление и режим обмена. После инициализации канала обмен выполняется по инициативе ПУ. Для интерфейса ПУ каждый канал DМА представляется парой сигналив: запрос обмена - DRQx и подтверждение обмена - DАСКх#, где х - номер используемого канала. На рисунке приведена диаграмма стандартного цикла передачи байта (для 8-битного канала) или слова (для 16-битного) от ПУ в память по каналу DМА. Шина PCI РСI 1оса1 bus — шина соединения периферийных компонентов является основной шиной расширения соименных компьютеров. Шина разрабатывалась в расчете на Pentium, но хорошо сочеталась и с процессорами 486. Сейчас РСI является четко стандартизованной высокопроизводительной и надежной шиной расширения. Первая версия РСI 1.0 появилась в 1992 году. В РСI 2.0 (1993г.) введена спецификация коннекторов и карт расширения. В версии 2.1 (1995г.) введена частота 66 МГц. В настоящее время действует спецификация РСI 2.2 (декабрь 1998г.), которая уточняет и разъясняет некоторые положения предшествующей версии 2.1. Данное описание основано на тексте стандарта «РСI Local Bus Specification. Revision 2.2» от 18.12.1998, опубликованном организацией РСI SIG.

Поначалу шина РС1 вводилась как пристройка к системам c основной шиной ISA, став позже центральной шиной: она соединяется с системной шиной процессора высокопроизводительным мостом («северным»), входящим и состав чипсета. Остальные шины расширения ввода-вывода (ISA /Е ISA или МСА). а также локальная ISA - подобная шина Х-ВUS и интерфейс LРС, к которым подключаются микросхемы системной платы (контроллеры прерываний, клавиатуры, НГМД и прочие «мелочи»), подключаются к шине РСI через «южный» мост. В современных системных платах с хабовой архитектурой (см. п. 4.1) шину РСI отодвинули на периферию, не ущемляя ее в мощности канала связи с процессором и памятью, но не нагружая транзитным трафиком устройств других шин. Шина является синхронной - фиксации всех сигналов выполняется по положительному перепаду (фронту) сигнала СLК. Номинальной частотой синхронизации считается 33 МГц, при необходимости частота может быть понижена (на машинах с процессором 486 использовали частоты 20-33 МГц). Во многих случаях частоту успешно разгоняют и до 41,5 МГц (половина типовой частоты системной шины 83 МГц). Начиная с версии 2.1, допускается повышение частоты до 66 МГц при согласии всех устройств на шине. Номинальная разрядность шины данных — 32 бита, спецификация определяет и расширение разрядности до 64 бит. При частоте шины 33 МГц теоретическая пропускная способность достигает 132 Мбайт/с для 32-битной шины и 264 Мбайт/с для 64-битной; при частоте синхронизации 66 МГц — 26-1 и 528 Мбайт/с соответственно. Однако эти пиковые значения достигаются лишь во время передачи пакета, а из-за протокольных накладных расходов реальная средняя суммарная (для всех задатчиков) пропускная способность шины будет ниже. Слот РСI достаточен для подключения адаптера (в отличие от VIВ), на системной плате он может сосуществовать с любой из шин ввода - вывода (и даже с VIВ). С устройствами РСI процессор может взаимодействовать командами обращения к памяти и портам ввода - вывода, адресованным к областям, выделенным данному устройству при конфигурировании. Устройства могут вырабатывать запросы маскируемых и немаскируемых прерываний. Понятия каналов DMA для шины РСI нет, но агент шины может сам выступать в роли задатчика. поддерживая высокопроизводительный обмен с памятью (и не только), не занимая ресурсов центрального процессора. Таким образом, к примеру, может быть реализован обмен и режиме DМА с устройствами IDЕ, подключенными к контролеру РСI IDE. Спецификация РСI требует перемещаемости всех занимаемых ресурсов в пределах доступного пространства адресации. Это позволяет обеспечивать бесконфликтное распределение ресурсов для многих устройств (функций). Для управления устройствами рекомендуется вместо портов ввода - вывода по возможности использовать ячейки памяти. Одно и то же функциональное устройство может быть сконфигурировано по-разному, отображай свои регистры либо на пространство памяти, либо па пространство ввода – вывода. Драйвер может определить текущую настройку, прочитав содержимое регистра базового адреса устройства, - признаком пространства ввода - вывода будет единичное значение бита 0. Драйвер также может определить и номер запроса прерывания, который используется устройством.

Шины, логические устройства и функции РСI Для шины РСI принята иерархия понятий, идентифицирующих конкретное устройство. Эта иерархия требуется на этапе конфигурирования, когда производится опрос присутствующих устройств и их потребностях в ресурсах (пространствах памяти и ввода -вывода, а также запросах прерывания). В дальнейшей ргулярной работе устройства будут отзываться на обращения по назначенным иж'1 адресам, доведенным до сведения связанных с ними модулей ПО. Устройствам РСI называется микросхема или карта расширения, использующая для идентификации выделенную ей линию IDSEL. Устройство может быть многофункциональным, то есть состоять из множества так называемых функций. Каждой функции отводится конфигурационное пространство в 256 байт. Номер функции, к которой производится обращение в конфигурационных транзакциях, передастся по линиям АD[10:8] (.младшие линии требуются для адресации регистров внутри конфигурационного пространства). Таким образом, устройство может содержать до 8 функций. Простые (однофункциональные) устройства, в зависимости от реализации, могут отзываться либо на любой номер функции (игнорировать значение DO[10:8] в конфигурационном цикле), либо только на номер функции 0. Многофункциональные устройства должны отзываться только на конфигурационные циклы с номерами функций, для которых имеется конфигурационное пространство. При этом функция с номером 0 должна быть обязательно, номера остальных функций назначаются произвольно. Литература Основная 1. Калабеков Б.А. Цифровые устройства и Интерфейсы переферийных устройств. – М.: Горячая линия-Телеком, 2005. – 336 с.: ил. 2. Интерфейсы переферийных устройств / Под ред. Д.В. Пузанкова. – СПб.: Политехника, 2003. – 935 с.: ил. Дополнительная 1. Бройдо В.Л. Вычислительные системы, сети телекоммуникации. - СПб.: Питер, 2005. – 568 с. 2. Хамахер К. Организация ЭВМ. – СПб.: Питер, 2003. – 848 с.: ил.

Лекция 1 3

|

|||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2020-12-17; просмотров: 81; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.137.164.241 (0.021 с.) |