Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Исследование модуля Менеджера СобытийСодержание книги

Поиск на нашем сайте Лабораторная работа № 4 Исследование модуля Менеджера Событий Цель работы: изучить аппаратные и программные возможности Менеджера Событий (Event Manager) DSP TMS320F2812.

Теоретические сведения Структура Менеджера Событий

Менеджер Событий (EV) включает в себя таймеры общего назначения (GP), устройства сравнения/ШИМ, устройства захвата, схему квадратурного анализа (QEP). В сигнальном процессоре TMS320F2812 имеется два Менеджера Событий (EVA и EVB), которые выполняют аналогичные функции. EVA и EVB имеют идентичные регистры, расположенные по разным адресам.

Рис. 4.1. Менеджер Событий

Каждый Менеджер Событий управляется своей собственной логикой. Она может запрашивать прерывания. Менеджер Событий позволяет запускать встроенный либо внешний аналого-цифровой преобразователь. Для запуска внешнего АЦП на выводах EVASOC или EVBSOC (которые мультиплексируются с сигналами На рис. 4.1 представлена функциональная схема модуля Менеджера Событий (EVA). Рассмотрим блоки EVM подробнее. Таймеры общего назначения В каждом модуле EVM имеется по два GP (General Purpose) таймера общего назначения. В отличие от таймеров CPU, которые имеют разрядность 32-бита, таймеры Менеджера Событий являются независимыми 16-разрядными устройствами, c расширенной системой ввода/вывода. Они могут работать независимо друг от друга или быть синхронизированными.

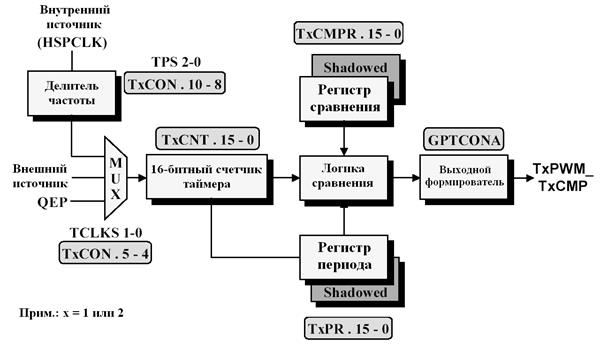

Рис. 4.2. Таймер общего назначения модуля EVM

Центральным блоком GP таймера является блок сравнения. Здесь происходит сравнение значения 16-битного счетчика (TxCNT) с двумя другими регистрами: регистром сравнения (TxCMPR) и регистром периода (TxPR). Если значения счетчика и регистра сравнения равны, то выходной формирователь устанавливает в «1» выходной сигнал (TxPWM). При достижении счетчиком значения регистра периода TxPWM сбрасывается. Особенностью DSP TMS320F2812 является наличие буферов регистров TxCMPR и TxPR которые позволяют обновлять значения по заранее заданным событиям: а) достижение GP таймером-счетчиком нуля; б) достижение GP таймером-счетчиком значения, равного значению в регистре периода; в) немедленная загрузка после записи в буфер.

Наличие буферов позволяет записывать новые значения в регистры в любой момент времени, не дожидаясь окончания цикла. Загрузка значения из буфера в регистр периода происходит только при достижении GP таймером-счетчиком нуля. Источником тактирования счетчика может являться: внешний сигнал (TCLKIN), тактовые импульсы от схемы квадратурного анализа (QEP) или тактовый сигнал от высокоскоростного предделителя (HSPCLK). В регистрах EVAIFRA, EVAIFRB, EVBIFRA, EVBIFRB имеются биты, отражающие флаги прерывания GP таймеров. Каждый из 4-х GP таймеров может вырабатывать прерывание на следующие события: а) достижение GP таймером-счетчиком нуля 0000h (TxUFINT); б) достижение максимального значения FFFFh (TxOFINT); в) достижение заданного значения сравнения (TxCINT); г) достижение значения, равного значению в регистре периода (TxPINT).

Каждый GP таймер может работать в одном из 4-х режимов.

1) СТОП/Хранение. В этом режиме GP таймер останавливается и удерживает текущее значение, при этом таймер-счетчик, выходы сравнения и значение предделителя остаются без изменения. Если же остановить таймер, просто запретив его работу, то счетчик будет сброшен и значение предделителя установится в х/1. 2) Непрерывный режим счета вверх. В этом режиме значение счетчика увеличивается до тех пор, пока не достигнет значения, равного значению в регистре периода (рис. 4.3). После этого счетчик сбрасывается в ноль и начинает считать сначала. При этом вырабатывается флаг прерывания, который остается установленным в течение одного такта. Если флаг не был маскирован, то вырабатывается запрос прерывания от периферийного устройства.

Рис. 4.3. Режим непрерывного счета вверх GP таймера

Продолжительность периода равна (TxPR)+1, за исключением первого периода, который может быть произвольным, так как начальное значение в счетчике может быть любым от 0000h до FFFFh. Если исходное значение больше, чем значение в регистре периода, то таймер досчитает до FFFFh, сбросится в ноль и продолжит работать так, как если бы исходное значение было равно нулю. При достижении счетчиком значения, равного значению в регистре периода, устанавливается флаг прерывания по периоду, происходит сброс в ноль и устанавливается флаг прерывания по нулю. Если исходное значение в счетчике находится между нулем и значением в регистре периода, то таймер сначала досчитает до значения в регистре периода, а затем будет работать так, как был запрограммирован. 3) Управляемый режим счета вверх/вниз. В этом режиме направление счета зависит от состояния входа TDIRA/B: вверх, если сигнал на TDIRA/B высокого уровня; вниз – низкого.

Рис. 4.4. Режим управляемого счета вверх/вниз GP таймера

4) Непрерывный режим счета вверх/вниз. В отличие от предыдущего режима, направление счета изменяется при достижении нуля или значения в регистре периода. Продолжительность периода в этом режиме равна 2∙(TxPR).

Рис. 4.5. Непрерывный режим счета вверх/вниз

Устройство захвата (Capture Unit) предназначено для определения временных параметров внешних сигналов. Значение выбранного GP таймера захватывается и запоминается в 2-уровневом стеке FIFO, когда на соответствующих выводах фиксируется заданный перепад уровней. Устройство захвата состоит из 3-х цепей CAPx (x=1, 2 или 3 для EVA; x=4, 5 или 6 для EVB). Устройство захвата обладает следующими особенностями: 1) имеется один 16-разрядный регистр управления захватом (CAPCONx); 2) имеется один 16-разрядный регистр статуса FIFO (CAPFIFOx); 3) в качестве тактирования можно использовать любой GP таймер; 4) все входы синхронизируются таймерами CPU; 5) пользователь сам устанавливает, по какому уровню осуществлять захват; 6) имеется 3 маскируемых флага прерывания. Входы CAP 1/2 и CAP 4/5 также могут быть использованы как входы схемы квадратурного анализа. Устройство сравнения. В каждом EVM предусмотрено по 3 устройства сравнения (Compare Unit). Эти устройства используют GP таймер 1 в качестве синхронизатора, и могут вырабатывать до 6 выходных сигналов сравнения (ШИМ-сигналов). Все 6 выходов работают независимо друг от друга. Регистры сравнения дублируются, позволяя фиксировать изменения ширины импульсов. Они позволяют снизить до минимума программную загрузку ядра при операциях измерений длительности, периодических выборок и генерации сигналов ШИМ.

Схема квадратурного анализа используется для подключения энкодера – оптического преобразователя направления и скорости вращения. Выходными сигналами энкодера являются два сигнала типа меандр, по частоте и фазовым сдвигам которых можно определить направление и скорость вращения. Схема QEP по этим сигналам формирует два сигнала: логический сигнал направления вращения (DIR) и частотный сигнал скорости вращения (CLK)

Примеры использования менеджера событий.

Менеджер событий предназначен для формирования управляющих сигналов и для определения временных характеристик внешних информационных сигналов. Наличие специализированного аппаратного модуля позволяет разгрузить ЦПУ для других задач. Одно из применений TMS320F2812 - системы электропривода. Для формирования ШИМ – сигналов специальной формы (например, синусоидального) используют один из двух методов. Первый метод предполагает вычисление функции синуса, которая входит в библиотеку «math.lib». Для этого в проект включается заголовочный файл «math.h», который позволяет обратиться к библиотеке математических функций. Но функция синуса в библиотеке «math.lib» – это функция с плавающей запятой и для её реализации на процессоре F2812, работающего с фиксированной запятой, потребуется много времени. Второй метод основан на работе с таблицей, в которую предварительно занесены рассчитанные значения функции. Этот метод еще называют «доступ к поисковой таблице» («Lookup Table Access»). Электронные устройства контроля используют такие таблицы не только для вычисления тригонометрических функций, но и для определения параметров управления. Доступ ячейкам таблицы осуществляется быстро, всего за несколько тактов можно определить требуемое значение функции. Увеличить точность вычисления функций можно, применив аппроксимацию. Таблица может быть как одномерной (выходная величина зависит от одного параметра), так и многомерной (выходная величина - функция двух и более переменных). Чем больше число ячеек таблицы, тем точнее аппроксимация исходной функции. В ПЗУ процессора TMS320F2812 уже “зашита” таблица синуса. Таблица использует дробно-целочисленный формат с фиксированной запятой IQ, или Q. Таблица представлена в формате Q30. Это означает, что 30 младших бит представляют дробную часть числа, один – целую и старший – знак числа.

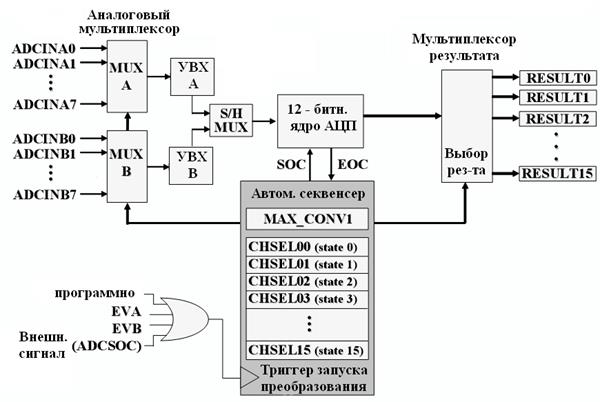

Лабораторная работа № 5 Исследование модуля АЦП Цель работы: изучить структуру встроенного АЦП, режимы его работы. Научится создавать простейшие программы с использованием АЦП. Теоретические сведения Структура модуля АЦП Модуль АЦП содержит ядро АЦП, два устройства выборки – хранения, аналоговый мультиплексор, мультиплексор УВХ, мультиплексор результата и автоматический секвенсер (устройство управления работой АЦП и мультиплексоров). 12- битный АЦП имеет 16 мультиплексированных входов. АЦП может работать либо в каскадном, либо в двухканальном режимах.

Рис. 5.1. Блок-схема модуля АЦП в каскадном режиме

Структура АЦП в каскадном режиме представлена на рис. 5.1. Как видно из рисунка, в этом режиме работой модуля управляет один автоматический секвенсер. Перед запуском необходимо задать число преобразований (“MAX_CONV1”) и номер канала, который будет преобразован на каждом шаге (“CHSELxx”). Результат преобразования на каждом шаге сохраняется в соответствующий регистр (“RESULT0” to “RESULT15”).

Можно задать два режима захвата сигналов – одновременный и последовательный. В первом случае два УВХ работают в параллель, т.е. выборка и захват происходят одновременно. При этом за один шаг осуществляется преобразование двух каналов различных групп с одинаковым кодом (например, ADCINA3 и ADCINB3). В последовательном режиме сигнал с любого входа может быть преобразован на любом шаге. Запуск преобразования может осуществляется программно, от внешнего источника или от менеджеров событий А или В. Запуск от Менеджера Событий осуществляется аппаратно, без использования прерываний, что позволяет очень точно задавать интервал преобразования. Прерывания от АЦП для обработки результатов могут быть сконфигурированы либо после каждого преобразования, либо по окончании преобразования последовательности.

Рис. 5.2. Блок-схема модуля АЦП в двухканальном режиме В двухканальном режиме автоматический секвенсер разделяется на две независимые части (“SEQ1” и “SEQ2”) со своими настройками и сигналами запуска. Входные каналы задается в регистрах CHSEL00.. CHSEL07 для последовательности SEQ1 и CHSEL08.. CHSEL15 для последовательности SEQ2, результаты преобразования сохраняется в регистрах RESULT0.. RESULT7 и RESULT8.. RESULT15 соответственно. Для любой из двух последовательностей может быть задан любой из 16 входных каналов. Данный режим позволяет получить фактически два независимых АЦП, со своими регистрами управления и сигналами запуска. Арбитр последовательности используется в случае одновременного появления сигналов запуска от двух последовательностей. В таком случае приоритет имеет SEQ1, преобразование SEQ2 будет задержано до окончания SEQ1. Время преобразования и система тактирования АЦП.

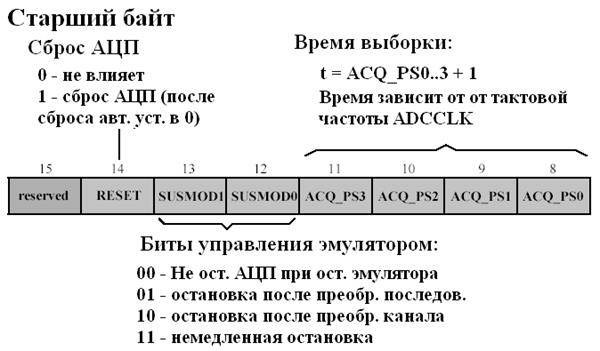

Рассмотрим настройку тактирования АЦП на примере. Тактирование АЦП осуществляется от высокоскоростного прескалера периферии HSPCLK (см. рис. 5.3).

Рис. 5.3. Пример конфигурации модуля тактирования АЦП.

Максимальная частота на выходе HSPCLK составляет 150 МГц. Максимальная частота тактирования АЦП FCLK согласно документации составляет 25 МГц. ADCCLKPS служит для формирования требуемой частоты FCLK из HSPCLK. Бит CPS позволяет при необходимости понизить частоту в два раза. Полученная ADCCLK подается на ядро АЦП и на устройство выборки-хранения. Битами ACQ_PC можно задать необходимое время захвата сигнала. За это время сигнал на УВХ должен установиться с заданной точностью. Время захвата зависит от сопротивления источника сигнала, характеристик сигнала, требуемой точности и рассчитывается для каждого случая отдельно. В лабораторных работах сигнал подается с потенциометра, высокая точность не требуется, поэтому время выборки может быть задано любое. Минимальное время преобразования для первого канала в последовательности составляет 200 мкс, для последующих - 80 мкс. Формат регистров модуля АЦП

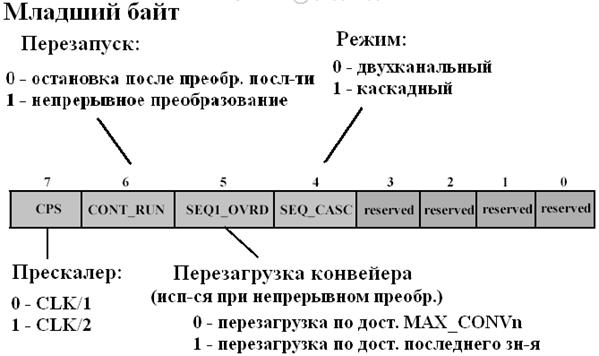

Рис. 5.4. Регистр 1 управления АЦП (ADCTRL1)

Рис. 5.5 Регистр 2 управления АЦП (ADCTRL2)

Рис. 5.6 Регистр 3 управления АЦП (ADCTRL3)

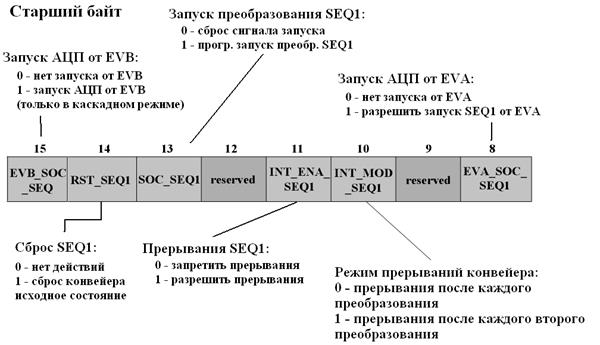

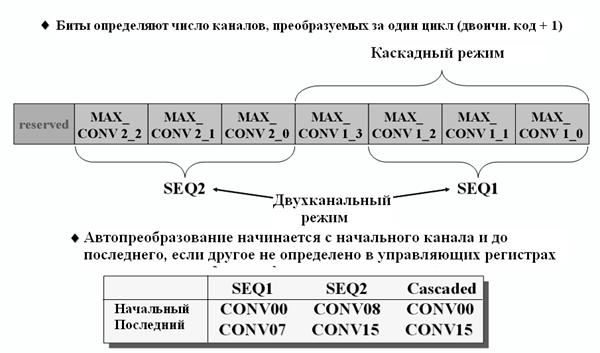

Регистр числа каналов для преобразования (ADCMAXCONV)

Рис.5.7. Формат регистра ADCMAXCONV

Рис. 5.8 Регистр статуса автопоследовательности (ADCASEQASR)

Каждый набор из 4-х бит CONVnn, выбирает один из 16 аналоговых входов АЦП для последовательного автоматического преобразования.

Часть I Создание проекта. 1.1 В Code Composer Studio создаем новый проект Lab6.pjt. Копируем из папки c:\tidcs файл lab6.c в папку с созданным проектом. Добавляем lab6.c в проект. 1.2 Добавляем в проект следующие файлы: C:\tidcs\c28\dsp281x\v100\DSP281x_headers\source\DSP281x_GlobalVariableDefs.c C:\tidcs\c28\dsp281x\v100\DSP281x_common\cmd\F2812_EzDSP_RAM_lnk.cmd C:\tidcs\c28\dsp281x\v100\DSP281x_headers\cmd\F2812_Headers_nonBIOS.cmd C:\ti\c2000\cgtools\lib\rts2800_ml.lib C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_PieCtrl.c C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_PieVect.c C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_DefaultIsr.c C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_Adc.c C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_usDelay.asm 1.3 Включаем в проект заголовочные файлы: Project → Build Options, в закладке Compiler выбираем Preprocessor и в поле Include Search Path (-i) вводим: C:\tidcs\C28\dsp281x\v100\DSP281x_headers\include;..\include. 1.4 Задаем глубину стека: Project → Build Options → Linker → Stack Size: 0x400.

Инициализация модуля АЦП. 5.1 Задаем: двух последовательный режим, запрещаем непрерывный режим, коэффициент деления 1 (регистр ADCTRL1). 5.2 Записываем количество преобразований 2 (регистр ADCMAXCONV). 5.3 Выбираем каналы ADCIN_A0 и ADCIN_B0 (регистр ADCCHSELSEQ1). 5.4 Разрешаем преобразования от Менеджера Событий А, разрешаем прерывания АЦП в конце каждой последовательности (регистр ADCTRL2) 5.3 Задаем делитель частоты высокоскоростного таймера равный 4.

Настройка прерываний. 6.1 Указываем адрес вектора прерываний (регистр ADCINT). 6.2 Разрешаем прерывание 6 группы 1 (регистр PIEIER1). 6.3 Вызываем подпрограммы инициализации: модуля прерывания периферийных устройств “InitPieCtrl()”, вектора прерывания периферийных устройств “InitPieVectTable()”, модуля АЦП “InitAdc()”.

7. Получение результатов преобразования АЦП (подпрограмма “adc_isr()”). 7.1 Считываем результаты преобразования из регистров ADCRESULT0 и ADCRESULT1 и сохраняем их соответственно в переменные Voltage_A0 и Voltage_B0. Так как данные в регистрах ADCRESULTn выровнены к левому краю, необходимо произвести сдвиг данных на четыре разряда вправо. 7.2 Подготавливаем АЦП к следующему преобразованию: сбрасываем последовательность SEQ1 (регистр ADCTRL2), сбрасываем бит прерывания SEQ1 (регистр ADCST), подтверждаем прерывания (регистр PIEACK).

Лабораторная работа № 4 Исследование модуля Менеджера Событий Цель работы: изучить аппаратные и программные возможности Менеджера Событий (Event Manager) DSP TMS320F2812.

Теоретические сведения Структура Менеджера Событий

Менеджер Событий (EV) включает в себя таймеры общего назначения (GP), устройства сравнения/ШИМ, устройства захвата, схему квадратурного анализа (QEP). В сигнальном процессоре TMS320F2812 имеется два Менеджера Событий (EVA и EVB), которые выполняют аналогичные функции. EVA и EVB имеют идентичные регистры, расположенные по разным адресам.

Рис. 4.1. Менеджер Событий

Каждый Менеджер Событий управляется своей собственной логикой. Она может запрашивать прерывания. Менеджер Событий позволяет запускать встроенный либо внешний аналого-цифровой преобразователь. Для запуска внешнего АЦП на выводах EVASOC или EVBSOC (которые мультиплексируются с сигналами На рис. 4.1 представлена функциональная схема модуля Менеджера Событий (EVA). Рассмотрим блоки EVM подробнее. Таймеры общего назначения В каждом модуле EVM имеется по два GP (General Purpose) таймера общего назначения. В отличие от таймеров CPU, которые имеют разрядность 32-бита, таймеры Менеджера Событий являются независимыми 16-разрядными устройствами, c расширенной системой ввода/вывода. Они могут работать независимо друг от друга или быть синхронизированными.

Рис. 4.2. Таймер общего назначения модуля EVM

Центральным блоком GP таймера является блок сравнения. Здесь происходит сравнение значения 16-битного счетчика (TxCNT) с двумя другими регистрами: регистром сравнения (TxCMPR) и регистром периода (TxPR). Если значения счетчика и регистра сравнения равны, то выходной формирователь устанавливает в «1» выходной сигнал (TxPWM). При достижении счетчиком значения регистра периода TxPWM сбрасывается. Особенностью DSP TMS320F2812 является наличие буферов регистров TxCMPR и TxPR которые позволяют обновлять значения по заранее заданным событиям: а) достижение GP таймером-счетчиком нуля; б) достижение GP таймером-счетчиком значения, равного значению в регистре периода; в) немедленная загрузка после записи в буфер.

Наличие буферов позволяет записывать новые значения в регистры в любой момент времени, не дожидаясь окончания цикла. Загрузка значения из буфера в регистр периода происходит только при достижении GP таймером-счетчиком нуля. Источником тактирования счетчика может являться: внешний сигнал (TCLKIN), тактовые импульсы от схемы квадратурного анализа (QEP) или тактовый сигнал от высокоскоростного предделителя (HSPCLK). В регистрах EVAIFRA, EVAIFRB, EVBIFRA, EVBIFRB имеются биты, отражающие флаги прерывания GP таймеров. Каждый из 4-х GP таймеров может вырабатывать прерывание на следующие события: а) достижение GP таймером-счетчиком нуля 0000h (TxUFINT); б) достижение максимального значения FFFFh (TxOFINT); в) достижение заданного значения сравнения (TxCINT); г) достижение значения, равного значению в регистре периода (TxPINT).

Каждый GP таймер может работать в одном из 4-х режимов.

1) СТОП/Хранение. В этом режиме GP таймер останавливается и удерживает текущее значение, при этом таймер-счетчик, выходы сравнения и значение предделителя остаются без изменения. Если же остановить таймер, просто запретив его работу, то счетчик будет сброшен и значение предделителя установится в х/1. 2) Непрерывный режим счета вверх. В этом режиме значение счетчика увеличивается до тех пор, пока не достигнет значения, равного значению в регистре периода (рис. 4.3). После этого счетчик сбрасывается в ноль и начинает считать сначала. При этом вырабатывается флаг прерывания, который остается установленным в течение одного такта. Если флаг не был маскирован, то вырабатывается запрос прерывания от периферийного устройства.

Рис. 4.3. Режим непрерывного счета вверх GP таймера

Продолжительность периода равна (TxPR)+1, за исключением первого периода, который может быть произвольным, так как начальное значение в счетчике может быть любым от 0000h до FFFFh. Если исходное значение больше, чем значение в регистре периода, то таймер досчитает до FFFFh, сбросится в ноль и продолжит работать так, как если бы исходное значение было равно нулю. При достижении счетчиком значения, равного значению в регистре периода, устанавливается флаг прерывания по периоду, происходит сброс в ноль и устанавливается флаг прерывания по нулю. Если исходное значение в счетчике находится между нулем и значением в регистре периода, то таймер сначала досчитает до значения в регистре периода, а затем будет работать так, как был запрограммирован. 3) Управляемый режим счета вверх/вниз. В этом режиме направление счета зависит от состояния входа TDIRA/B: вверх, если сигнал на TDIRA/B высокого уровня; вниз – низкого.

Рис. 4.4. Режим управляемого счета вверх/вниз GP таймера

4) Непрерывный режим счета вверх/вниз. В отличие от предыдущего режима, направление счета изменяется при достижении нуля или значения в регистре периода. Продолжительность периода в этом режиме равна 2∙(TxPR).

Рис. 4.5. Непрерывный режим счета вверх/вниз

Устройство захвата (Capture Unit) предназначено для определения временных параметров внешних сигналов. Значение выбранного GP таймера захватывается и запоминается в 2-уровневом стеке FIFO, когда на соответствующих выводах фиксируется заданный перепад уровней. Устройство захвата состоит из 3-х цепей CAPx (x=1, 2 или 3 для EVA; x=4, 5 или 6 для EVB). Устройство захвата обладает следующими особенностями: 1) имеется один 16-разрядный регистр управления захватом (CAPCONx); 2) имеется один 16-разрядный регистр статуса FIFO (CAPFIFOx); 3) в качестве тактирования можно использовать любой GP таймер; 4) все входы синхронизируются таймерами CPU; 5) пользователь сам устанавливает, по какому уровню осуществлять захват; 6) имеется 3 маскируемых флага прерывания. Входы CAP 1/2 и CAP 4/5 также могут быть использованы как входы схемы квадратурного анализа. Устройство сравнения. В каждом EVM предусмотрено по 3 устройства сравнения (Compare Unit). Эти устройства используют GP таймер 1 в качестве синхронизатора, и могут вырабатывать до 6 выходных сигналов сравнения (ШИМ-сигналов). Все 6 выходов работают независимо друг от друга. Регистры сравнения дублируются, позволяя фиксировать изменения ширины импульсов. Они позволяют снизить до минимума программную загрузку ядра при операциях измерений длительности, периодических выборок и генерации сигналов ШИМ.

Схема квадратурного анализа используется для подключения энкодера – оптического преобразователя направления и скорости вращения. Выходными сигналами энкодера являются два сигнала типа меандр, по частоте и фазовым сдвигам которых можно определить направление и скорость вращения. Схема QEP по этим сигналам формирует два сигнала: логический сигнал направления вращения (DIR) и частотный сигнал скорости вращения (CLK)

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-19; просмотров: 290; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.119 (0.01 с.) |

и

и  ), вырабатывается строб начала преобразования (SOC).

), вырабатывается строб начала преобразования (SOC).