Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Микропроцессоры. История появления и развития.Содержание книги

Поиск на нашем сайте

Микропроцессоры. История появления и развития. 1. Микропроцессор, объявленный как «компьютер-на-чипе», был 4-битный Intel 4004 (ноябрь 1971). 2. Появление универсальных многопрограммных 8-битных Intel 8080 (апрель 1974) и MOS Technology 6502 (сентябрь 1975). Они использовались в производстве настольных компьютеров и игровых консолей. В отличие от 4004, они использовали раздельные шины адреса и данных, а инструкции и данные хранились в одних и тех же областях памяти. Таким образом, это были первые CPU, работающие на основе архитектуры фон Неймана и выполняющие функции АЛУ и устройства управления. 3. выпуск 16-битных Intel 8086/88 (июнь 1978), которые положили начало архитектуре x86 и массовому распространению ПК. В 1980 был представлен первый процессор с RISC-архитектурой — IBM 801. По сравнению с CISC-процессорами того времени он имел меньшие размеры и число инструкций, был проще и дешевле в изготовлении. 4. Переход на 32-разрядные модели, позволявшие эффективнее работать с большими числами и адресовать ранее недоступные объемы памяти. В октябре 1985 вышел первый 32-битный x86-процессор, Intel 80386, а в 1986 появились три новые 32-битные RISC-архитектуры — MIPS, SPARC и PA-RISC, представленные компаниями MIPS Technologies, Sun и HP соответственно. 5. появление 64-битных процессоров MIPS R4000 (февраль 1991) и DEC Alpha 21064 (ноябрь 1992). Alpha был также первым CPU, поддерживающим суперскалярность, то есть возможность исполнять более одной инструкции за такт. Первыми суперскалярными процессорами других архитектур стали IntelPentium (март 1993), MIPS R8000 (июнь 1994) и др. 6. динамическое исполнение команд - процессор исполняет команды не в том порядке, в котором он их считывает из памяти, а в том, который был более эффективен по времени выполнения, и при этом, конечно же, не нарушал семантики программы. Эта технология была реализована во всех процессорах соответствующих архитектур, начиная с MIPS R10000 (октябрь 1994), PA-RISC 8000 (март 1995), IntelPentiumPro (ноябрь 1995). 7. С 2000-х годов развитие центральных процессоров пошло в сторону увеличения количества ядер в одном процессорном корпусе.

Архитектуры процессоров по набору команд (RISC, CISC). Уровень архитектуры команд включает набор машинных команд, которые выполняются микропрограммой-интерпретатором или аппаратным обеспечением. CISC-архитектура, компьютер на микропроцессоре с полным набором команд

RISC-архитектура, компьютер с сокращенным набором команд

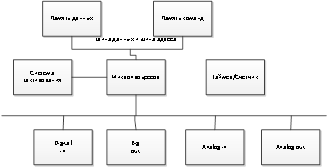

Микропроцессор, микрокомпьютер, микроконтроллер. Определения и отличительные особенности. Микропроцессор – это процессор, который реализован на 1 микросхеме. Процессор – это устройство, предназначенное для выполнения арифметических, логических операций и управления. Характеристики микропроцессора: · Центральное устройство – микро ЭВМ · Возможны 2 базовые архитектуры (Фон Неймана и гарвардская) · Для работы необходимы дополнительные устройства. Работа микропроцессора (цикл, выработка, выполнение): · Считывает сл. Машинное слово из памяти команд · Декодирует · В случае необходимости считывает операнды · Выполняет команду · Записывает результат в память Для функционирования микропроцессора необходимо добавить память и периферийные устройства. У микропроцессора имеется дешифратор команд, арифметико-логическое устройство (АЛУ). Микро ЭВМ = микропроцессор + память + периферия (рис.)

Периферия микро ЭВМ: · Цифровые входы и выходы · АЦП · ЦАП · Таймеры/счетчики · Сетевые интерфейс и связи · Устройства графического вывода Микроконтроллер – это микросхема для управления электронными устройствами (микро ЭВМ реализованная на 1 кристалле). Особенности микроконтроллера: · Микро ЭВМ на 1 микросхеме или кристалле · Все вычислительные мощности и каналы вв/выв необходимы для разработки систем управления реального времени · Основа большинства современной продукции Схема сброса При включении напряжения питания МК должен начать выполнять записанную в памяти программу работы. На этапе нарастания напряжения питания МК принудительно переводится в начальное состояние, которое называют состоянием сброса. При этом устанавливаются в исходное состояние внутренние магистрали МК, сигналы управления и регистры специальных функций. Последние определяют начальное состояние периферийных модулей МК, которое чаще всего по умолчанию неактивно.

Для перевода МК в состояние сброса при установившемся напряжении питания достаточно подать сигнал высокого или низкого уровня (в соответствии со спецификацией МК) на вход сброса (RESET). При нажатии кнопки "сброс" или включении питания буфер линии устанавливается в режим ввода и реализует так называемый внешний сброс. МК может перейти в состояние сброса также по сигналам устройств контроля состояния, которые имеются в составе контроллера.

Порты ввода/вывода Каждый МК имеет некоторое количество линий ввода/вывода, которые объединены в многоразрядные (чаще 8-разрядные) параллельные порты ввода/вывода. В памяти МК каждому порту ввода/вывода соответствует свой адрес регистра данных. В зависимости от реализуемых функций различают следующие типы параллельных портов: однонаправленные порты; двунаправленные порты; порты с альтернативной функцией; порты с программно управляемой схемотехникой входного/выходного буфера. Порты выполняют роль устройств временного согласования функционирования МК и объекта управления, которые в общем случае работают асинхронно. Различают три типа алгоритмов обмена информацией между МК и внешним устройством через параллельные порты ввода/вывода:режим простого программного ввода/вывода;режим ввода/вывода со стробированием;режим ввода/вывода с полным набором сигналов подтверждения обмена. Сторожевой таймер Сторожевой таймер используется для предотвращения зависания МК. Основу сторожевого таймера составляет многоразрядный счетчик. При сбросе МК счетчик обнуляется. После перехода МК в активный режим работы значение счетчика начинает увеличиваться независимо от выполняемой программы. При достижении счетчиком максимального кода генерируется сигнал внутреннего сброса, и МК начинает выполнять рабочую программу сначала. Для исключения сброса по переполнению сторожевого таймера рабочая программа МК должна периодически сбрасывать счетчик, если исполнение рабочей программы было нарушено, например, вследствие "зависания", то произойдет сброс по переполнению сторожевого таймера, и нормальный ход выполнения рабочей программы будет восстановлен. Использование сторожевого таймера существенно повышает способность к самовосстановлению системы на основе МК. Резидентная память РП данных является наиболее гибким адресным пространством, которое позволяет реализовать режимы прямой, регистровой, косвенной и битовой адресации. РПД состоит из таких областей: 1) ОЗУ объемом 128 байтов 2) блок РСФ - содержит 20 однобайтовых регистров Внутреннее ОЗУ предполагает прямую и косвенную адресацию, а банки рабочих регистров, которые входят в него, - также и регистровую адресацию. Состоит из: 1. Четыре банка рабочих регистров по восемь байтов в каждом для косвенной адресации любой из 128 ячеек внутреннего ОЗУ. 2. Блок ячеек ОЗУ с побитовой адресацией 3. Блок ячеек ОЗУ без особенностей. Все три области предполагают прямую и косвенную адресацию байтов Блок регистров специальных функций (РСФ):

- арифметические - указательные - регистры-фиксаторы портов ввода-вывода - регистры управления системой прерываний - регистры управления и настройки таймеров-счетчиков - счетные регистры таймеров - регистры управления последовательным портом - регистр управления мощностью.

АЦП. Определение. Основные понятия: разрешение, разрядность, частота дискретизации. АЦП — электронное устройство, преобразующее напряжение в двоичный цифровой код. Тем не менее, некоторые неэлектронные устройства с цифровым выходом, следует также относить к АЦП, например, некоторые типы преобразователей угол-код. Простейшим одноразрядным двоичным АЦП является компаратор. Разрешение АЦП — минимальное изменение величины аналогового сигнала, которое может быть преобразовано данным АЦП — связано с его разрядностью. В случае единичного измерения без учёта шумов разрешение напрямую определяется разрядностью АЦП. Разрядность АЦП характеризует количество дискретных значений, которые преобразователь может выдать на выходе. В двоичных АЦП измеряется в битах, в троичных АЦП измеряется в тритах. Например, двоичный 8-ми разрядный АЦП, способен выдать 256 дискретных значений (0…255), поскольку Частота дискретизации — частота взятия отсчетов непрерывного во времени сигнала при его дискретизации (в частности, АЦП). Измеряется в Герцах. Чем выше частота дискретизации, тем более широкий спектр сигнала может быть представлен в дискретном сигнале. 28.Микроконтроллер MSP430.16битный АЦП SD16_A Модуль АЦП SD16 содержит до трёх независимых сигма-дельта аналогово-цифровых преобразователей и встроенный источник опорного напряжения. Каждый из АЦП имеет до восьми полностью дифференциальных переключаемых каналов, в том числе встроенный датчик температуры. АЦП созданы на базе дельта-сигма модуляторов второго порядка с передискретизацией и цифровых децимирующих фильтров. Для прореживания (децимации) используются фильтры comb-типа с программируемым коэффициентом прореживания до 256. Дополнительная фильтрация может быть осуществлена программно. Модуль АЦП SD16 обладает следующими свойствами: -16-битная сигма-дельта архитектура -До 3-х независимо функционирующих каналов АЦП -До 8 переключаемых дифференциальных аналоговых входов на канал -Программно включаемый встроенный источник опорного напряжения (1,2В) -Программный выбор встроенного или внешнего источника опорного напряжения

-Встроенный датчик температуры, доступный для всех каналов -Входная частота модулятора до 1,048576 МГц (частота выборки fSAMPLE до 4096 Гц при передискретизации 256х) -Программно выбираемый режим преобразования с пониженным энергопотреблением Модуль АЦП SD16 конфигурируется при помощи пользовательского программного обеспечения. Ядро аналогово-цифрового преобразователя. Аналогово-цифровое преобразование осуществляется однобитным сигма-дельта модулятором второго порядка. Однобитный компаратор в составе модулятора осуществляет квантование сигнала с частотой модулятора fM. Получающийся в результате однобитовый поток усредняется цифровым фильтром, формируя результат преобразования. Цифровой фильтр обрабатывает 1-битный поток данных, поступающий с модулятора при помощи SINC3 фильтра comb-типа. Модуль АЦП SD16 содержит встроенный источник опорного напряжения величиной 1.2В, который может быть использован для всех каналов модуля SD16 и включается битом SD16REFON. Для снижения помех при использовании встроенного источника опорного напряжения рекомендуется использование внешнего конденсатора ёмкостью в 100 нФ, подключенного между выводов VREF и AVSS. Опорное напряжение также может использоваться вне микроконтроллера, если это разрешено битом SD16VMIDON. Выход ИОН буферизован, нагрузочный ток буфера до 1мА. При использовании опорного напряжения вне микроконтроллера, требуется внешний конденсатор ёмкостью в 470 нФ, подключенный между выводов VREF и AVSS. Уточнённые параметры см. в документации на конкретный тип МК. Каждому каналу модуля SD16 сопоставлен регистр памяти SD16MEMx. На каждом шаге децимации цифрового фильтра результат преобразования записываются в соответствующий регистр SD16MEMx. При перезаписи нового значения в регистр SD16MEMx устанавливается бит SD16IFG. Бит SD16IFG обнуляется автоматически при чтении из регистра SD16MEMx либо может быть обнулён программно.

Непрерывный режим

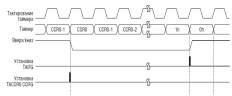

Непрерывный режим может использоваться для генерации независимых временных интервалов и выходных частот. Каждый раз по завершении интервала генерируется прерывание. Следующий временной интервал добавляется к регистру TACCRx в процедуре обработки прерывания. На рис. Показаны два раздельных временных интервала t0 и t1, добавляемые к регистрам захвата/сравнения. При таком использовании временные интервалы управляются аппаратно, без программного обеспечения, без влияния времени задержки прерывания. При использовании всех трех регистров захвата/сравнения можно сгенерировать до трех независимых временных интервалов или выходных частот. Временные интервалы можно реализовать также в других режимах, где TACCR0 используется как регистр периода. Их обработка более комплексна, поскольку сумма старого значения TACCRx и нового периода может быть выше значения TACCR0. Когда предыдущее значение TACCRx плюс tx больше величины TACCR0, значение TACCR0 должно быть вычтено для получения правильного временного интервала.

Режим «вверх/вниз»

Использование режима вверх/вниз Режим «вверх/вниз» поддерживает приложения, требующие наличия «мертвого» времени между выходными сигналами (см. раздел «Модуль вывода Таймера А»). К примеру, чтобы избежать перегрузки, два выхода, управляющие H-мостом никогда не должны одновременно иметь высокий уровень. В примере, показанном на рис. величина времени простоя tdead составляет: tdead = ttimer (TACCR1 – TACCR2), где: tdead – интервал времени, в течение которого оба выхода должны быть неактивны ttimer – время цикла тактирования таймера

Прерывания Таймера А С 16-разрядным модулем таймера А связаны два вектора прерываний: -Вектор прерывания TACCR0 для TACCR0 CCIFG -Вектор прерывания TAIV для всех других флагов CCIFG и TAIFG В режиме захвата любой флаг CCIFG устанавливается, когда значение таймера зафиксировано в соответствующем регистре TACCRx. В режиме сравнения устанавливается любой флаг CCIFG, если TAR досчитал до соответствующего значения TACCRx. Программное обеспечение может также устанавливать или очищать любой флаг CCIFG. Все флаги CCIFG запрашивают прерывание, когда установлены их соответствующие биты CCIE и бит GIE. Прерывание TACCR0 Флаг TACCR0 CCIFG обладает наивысшим приоритетом прерывания Тай- мера А и имеет специализированный вектор прерывания, как показано на рис. 11-15. Флаг TACCR0 CCIFG автоматически сбрасывается, когда обслуживается запрос на прерывание TACCR0.

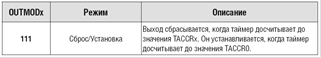

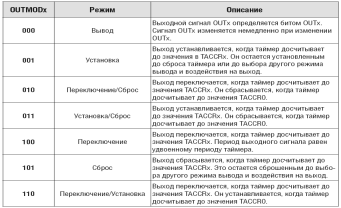

Модуль вывода Каждый блок захвата/сравнения содержит модуль вывода. Модуль вывода используется для генерации выходных сигналов, в т.ч. таких, как ШИМ-сигналы. Каждый модуль вывода имеет восемь рабочих режимов, которые генерируют сигналы, основываясь на сигналах EQU0 и EQUx. Режимы вывода устанавливаются битами OUTMODx, их описание приведено в таблице 11-2. Сигнал OUTx изменяется с нарастающим фронтом тактового сигнала таймера во всех режимах, кроме режима 0. Режимы вывода 2, 3, 6 и 7 не используются для модуля вывода 0, потому что EQUx=EQU0.

Примечание: Переключение между режимами выводаПри переключении между режимами вывода один из битов OUTMODx должен оставаться установленным во время перехода, кроме переключения в режим 0. В противном случае может произойти сбой, поскольку режим вывода 0 декодирует элемент NOR (НЕ-ИЛИ). Безопасный метод переключения между режимами вывода заключается в использовании режима вывода 7 как переходного состояния: BIS #OUTMOD_7,&TACCTLx;Установка режима вывода 7 BIC #OUTMODx,&TACCTLx;Очистка лишних битов

38АЦП. Типы АЦП. Параллельного преобразования.

Рис. 3 Параллельный АЦП Такая архитектура предполагает использование большого числа резисторов и компараторов, имеет ограничение по максимальной разрешающей способности. Обычно параллельные АЦП имеют разрешающую способность, соответствующую 8-разрядам. Их максимальная частота дискретизации может достигать 1 ГГц.

АЦП. Погрешности, причины. Характеристики реальных АЦП по ряду параметров могут отличаться от идеальных характеристик. Различают: а - погрешность смещения; б - погрешность усиления; в - интегральную нелинейность; г - дифференциальную нелинейность. Передаточная характеристика преобразователя может быть сдвинута относительно идеальной характеристики. Эта погрешность “смещения” или “установки нуля” определяется как значение аналоговой величины, при которой характеристика пересекает ось входных напряжений. Наклон передаточной характеристики может отличаться от своего идеального значения, что приводит к погрешности “наклона” или “усиления”. Для большинства имеющихся АЦП погрешности смещения и усиления или очень малы, или могут быть полностью устранены с помощью предварительных регулировок. Погрешности, связанные с нелинейностью передаточной характеристики АЦП, невозможно уменьшить с помощью регулировки. Интегральная нелинейность - это максимальное отклонение передаточной характеристики от идеальной прямолинейной характеристики при нулевых значениях погрешностей смещения и усиления. Дифференциальная нелинейность – это отклонение величины одного из квантов от его идеального аналогового значения. TMS C281x. Конвейер В ПЦОС широко используется конвейерный режим работы в целях повышения производительности. В четырехкаскадном конвейере могут обрабатываться одновременно четыре команды, причем все команды находятся на разных стадиях выполнения. Наличие четырехкаскадного конвейера позволяет выполнять большинство команд за один такт. В четырехкаскадном конвейере предварительную выборку команды, дешифрирование, выборку операнда и исполнение команд можно осуществлять независимым образом. Пока производится предварительная выборка команды N, предыдущая команда N─1 дешифрируется, команда N─2 выбирает операнд, а N─3 исполняется. Конвейр реализован автоматически таким образом, что специалист, программирующий ПЦОС никак не замечает его наличие. Преимущества - Предельная простота протокола передачи на физическом уровне обуславливает высокую надежность и быстродействие передачи. Предельное быстродействие шины SPI измеряется десятками мегагерц и, поэтому, она идеальна для потоковой передачи больших объемов данных и широко используется в высокоскоростных ЦАП/АЦП, драйверах светодиодных дисплеев и микросхемах памяти - Все линии шины SPI являются однонаправленными, что существенно упрощает решение задачи преобразования уровней и гальванической изоляции микросхем - Простота программной реализации протокола SPI.

Достоинства -Требуется только две линии - линия данных (SDA) и линия синхронизации (SCL) Каждое устройство, подключённое к шине, может быть программно адресовано по уникальному адресу. В каждый момент времени существует простое отношение ведущий/ведомый: ведущие могут работать как ведущий-передатчик и ведущий-приёмник. -Шина позволяет иметь несколько ведущих, предоставляя средства для определения коллизий и арбитраж для предотвращения повреждения данных в ситуации, когда два или более ведущих одновременно начинают передачу данных В стандартном режиме обеспечивается передача последовательных 8-битных данных со скоростью до 100 кбит/с, и до 400 кбит/с в “быстром” режиме. - Встроенный в микросхемы фильтр подавляет всплески, обеспечивая целостность данных. - Максимальное допустимое количество микросхем, подсоединённых к одной шине, ограничивается максимальной емкостью шины 400 пФ.

В отличие от - микроконтроллера (однокристального компьютера), микросхемы предназначенной для управления электронными устройствами, областью применения ПЛК обычно являются автоматизированные процессы промышленного производства, в контексте производственного предприятия; - компьютеров, ПЛК ориентированы на работу с машинами и имеют развитый 'машинный' ввод-вывод сигналов датчиков и исполнительных механизмов в противовес возможностям компьютера, ориентированного на человека (клавиатура, мышь, монитор и т. п.); - встраиваемых систем — ПЛК изготавливается как самостоятельное изделие, отдельно от управляемого при его помощи оборудования. В системах управления технологическими объектами логические команды преобладают над числовыми операциями, что позволяет при сравнительной простоте микроконтроллера, получить мощные системы действующие в режиме реального времени. В современных ПЛК числовые операции реализуются наравне с логическими. В то же время, в отличие от большинства процессоров компьютеров, в ПЛК обеспечивается доступ к отдельным битам памяти.

50Программируемые логические интегральные схемы. Программируемая логическая интегральная схема (ПЛИС, PLD) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программаторы и отладочные среды, позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры. Альтернативой ПЛИС являются: программируемые логические контроллеры (ПЛК), базовые матричные кристаллы (БМК), требующие заводского производственного процесса для программирования; ASIC — специализированные заказные большие интегральные схемы(БИС); специализированные компьютеры, процессоры (например, цифровой сигнальный процессор) или микроконтроллеры, которые из-за программного способа реализации алгоритмов в работе медленнее ПЛИС. ПЛИС широко используется для построения различных по сложности и по возможностям цифровых устройств. Это приложения, где необходимо большое количество портов ввода-вывода, цифровая обработка сигнала, высокоскоростная передача данных, криптография и др.

Процессоры цифровой обработки сигналов (ПЦОС). Требования к ПЦОС. Процессор цифровой обработки сигналов (сигнальный процессор, Digital Signal Processor) – это микропроцессор, особенностью работы которого является поточный характер обработки больших объемов данных в реальном масштабе времени и, как правило, с интенсивным обменом данных с внешними устройствами. ПЦОС данные с гораздо большими скоростями, чем обычные МК. DSP-процессоры оптимизируются для обработки аудио- и видеосигналов. Отсюда возникают требования: -большие регистровые контексты, поскольку чем больше данных можно сохранить в регистрах, тем меньше времена циклов ожидания при чтении и записи во внешнюю память. -Очень высокие частоты прерываний вплоть до 100 КГц, тк в процессе работы DSP-приложения получают данные из внешнего мира в реальном времени, нередко со скоростями до Мбайт/секунду. -специальные регистры для исполнения циклов с нулевыми накладными расходами -аппаратные стеки, экономящие целый такт при выполнении вызова функции. -высокая точность обработки данных -реализация устройства в весьма компактном и миниатюрном виде -достижение высокой стабильности характеристик устройства в различных температурных условиях функционирования Чтобы соответствовать таким требованиям, большинство процессоров цифровой обработки сигналов имеют множество приоритетов прерываний, теневые регистры (как минимум, один набор) для снижения накладных расходов на переключение контекстов, а также немаскируемое прерывание.

TMS C281x. Общие сведения Это цифровой сигнальный процессор. Производитель Texas Instruments. Обладают повышенной производительностью и широкими функциональными возможностями. Имеют возможность использования внешнего контроллера ПДП. Умножитель микропроцессоров помимо операций умножения позволяет выполнять за один такт возведение в квадрат. Аппаратная поддержка кратного выполнения команды, реализован режим двоичной инверсно-косвенной адресации, предназначенный для эффективной реализации быстрого преобразования Фурье. Характеристики: • Три 32-разрядных таймера ЦПУ • Два модуля-менеджера событий (EVA, EVB) • Расширенный аналого-цифровой преобразователь (АЦП) • Улучшенный модуль Controller Area Network (ECAN) • Многоканальный буфер последовательного порта (McBSP) • Последовательный интерфейс модулей связи (SCI-A, SCI-B) • последовательный периферийный интерфейс (SPI) • Цифровые входы / выходы и выводы общего назначения

TMS C281x. Архитектура.

Базовая архитектура ПЦОС – это совокупность характерных особенностей процессора, направленная на повышение его производительности и отличающая ПЦОС от микросхем других типов. Она обусловлена: применением модифицированной гарвардской архитектуры; широкому использованием конвейерного режима работы; наличием специализированного устройства умножения; наличием специальных команд для цифровой обработки сигналов; реализацией короткого командного цикла. Модифицированная гарвардская архитектура предусматривает раздельные шины команд и данных, позволяет одновременно выбирать инструкции и операнды. Возможность обмена между памятью программ и данных увеличивает гибкость ПЦОС. Так, коэффициенты, расположенные в памяти программ, могут быть переданы в память данных, что приводит к экономии памяти, выделяемой для коэффициентов. Такая архитектура позволяет выполнять параллельную выборку команд и операндов. В совмещении с четырехкаскадным конвейером это позволяет процессору производить параллельную обработку нескольких команд. Модифицированная гарвардская архитектура допускает обмен содержимым между памятью программ и памятью данных, что расширяет возможности устройства.

Система тактирования Современные МК содержат встроенные тактовые генераторы, которые требуют минимального числа внешних времязадающих элементов. На практике используются три основных способа определения тактовой частоты генератора: с помощью кварцевого резонатора, керамического резонатора и внешней RC-цепи.

Микропроцессоры. История появления и развития. 1. Микропроцессор, объявленный как «компьютер-на-чипе», был 4-битный Intel 4004 (ноябрь 1971). 2. Появление универсальных многопрограммных 8-битных Intel 8080 (апрель 1974) и MOS Technology 6502 (сентябрь 1975). Они использовались в производстве настольных компьютеров и игровых консолей. В отличие от 4004, они использовали раздельные шины адреса и данных, а инструкции и данные хранились в одних и тех же областях памяти. Таким образом, это были первые CPU, работающие на основе архитектуры фон Неймана и выполняющие функции АЛУ и устройства управления. 3. выпуск 16-битных Intel 8086/88 (июнь 1978), которые положили начало архитектуре x86 и массовому распространению ПК. В 1980 был представлен первый процессор с RISC-архитектурой — IBM 801. По сравнению с CISC-процессорами того времени он имел меньшие размеры и число инструкций, был проще и дешевле в изготовлении. 4. Переход на 32-разрядные модели, позволявшие эффективнее работать с большими числами и адресовать ранее недоступные объемы памяти. В октябре 1985 вышел первый 32-битный x86-процессор, Intel 80386, а в 1986 появились три новые 32-битные RISC-архитектуры — MIPS, SPARC и PA-RISC, представленные компаниями MIPS Technologies, Sun и HP соответственно. 5. появление 64-битных процессоров MIPS R4000 (февраль 1991) и DEC Alpha 21064 (ноябрь 1992). Alpha был также первым CPU, поддерживающим суперскалярность, то есть возможность исполнять более одной инструкции за такт. Первыми суперскалярными процессорами других архитектур стали IntelPentium (март 1993), MIPS R8000 (июнь 1994) и др. 6. динамическое исполнение команд - процессор исполняет команды не в том порядке, в котором он их считывает из памяти, а в том, который был более эффективен по времени выполнения, и при этом, конечно же, не нарушал семантики программы. Эта технология была реализована во всех процессорах соответствующих архитектур, начиная с MIPS R10000 (октябрь 1994), PA-RISC 8000 (март 1995), IntelPentiumPro (ноябрь 1995). 7. С 2000-х годов развитие центральных процессоров пошло в сторону увеличения количества ядер в одном процессорном корпусе.

|

|||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-09; просмотров: 331; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.16.49.213 (0.018 с.) |

, троичный 8-ми разрядный АЦП, способен выдать 6561 дискретное значение, поскольку

, троичный 8-ми разрядный АЦП, способен выдать 6561 дискретное значение, поскольку  .

. В непрерывном режиме таймер многократно считает вверх до 0FFFFh и перезапускается от нуля, как показано на рис. Регистр захвата/сравнения TACCR0 работает подобно другим регистрам захвата/сравнения.

В непрерывном режиме таймер многократно считает вверх до 0FFFFh и перезапускается от нуля, как показано на рис. Регистр захвата/сравнения TACCR0 работает подобно другим регистрам захвата/сравнения. Флаг прерывания TAIFG устанавливается, когда таймер считает от 0FFFFh к нулю. На рис. показан цикл установки флага.

Флаг прерывания TAIFG устанавливается, когда таймер считает от 0FFFFh к нулю. На рис. показан цикл установки флага. Используется, если период таймера должен отличаться от значения 0FFFFh и необходима генерация симметричных импульсов.Таймер непрерывно считает вверх до значения, находящегося в регистре сравнения TACCR0 и назад к нулю, как показано на рис. Период составляет

Используется, если период таймера должен отличаться от значения 0FFFFh и необходима генерация симметричных импульсов.Таймер непрерывно считает вверх до значения, находящегося в регистре сравнения TACCR0 и назад к нулю, как показано на рис. Период составляет удвоенную величину значения в TACCR0.

удвоенную величину значения в TACCR0.

Параллельные АЦП являются самым быстрым типом АЦП, использующим большое количество компараторов, работающих параллельно, по этой причине АЦП называют параллельный. N-разрядный параллельный АЦП состоит из 2N резисторов и 2N–1 компараторов, размещенных, как это показано на рис. 3. На каждый компаратор подается опорное напряжение, значение которого для соседних точек отличается на величину, соответствующую одному младшему значащему разряду (LSB) (более старшие разряды — в верхних по схеме элементах). При фиксированном входном напряжении все компараторы, размещенные на схеме ниже некоторой точки, имеют входное напряжение выше опорного напряжения. На их логическом выходе присутствует "1". У всех же компараторов выше этой точки опорное напряжение больше входного, и их логический выход установлен в "0".

Параллельные АЦП являются самым быстрым типом АЦП, использующим большое количество компараторов, работающих параллельно, по этой причине АЦП называют параллельный. N-разрядный параллельный АЦП состоит из 2N резисторов и 2N–1 компараторов, размещенных, как это показано на рис. 3. На каждый компаратор подается опорное напряжение, значение которого для соседних точек отличается на величину, соответствующую одному младшему значащему разряду (LSB) (более старшие разряды — в верхних по схеме элементах). При фиксированном входном напряжении все компараторы, размещенные на схеме ниже некоторой точки, имеют входное напряжение выше опорного напряжения. На их логическом выходе присутствует "1". У всех же компараторов выше этой точки опорное напряжение больше входного, и их логический выход установлен в "0".

Отличительной чертой задач цифровой обработки сигналов является поточный характер обработки больших объемов данных в реальном масштабе времени, требующий от технических средств высокой производительности и возможности интенсивного обмена с внешними устройствами. Это достигается в настоящее время благодаря специфической архитектуре ПЦОС, называемой базовой архитектурой ПЦОС.

Отличительной чертой задач цифровой обработки сигналов является поточный характер обработки больших объемов данных в реальном масштабе времени, требующий от технических средств высокой производительности и возможности интенсивного обмена с внешними устройствами. Это достигается в настоящее время благодаря специфической архитектуре ПЦОС, называемой базовой архитектурой ПЦОС.