Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Микроконтроллер MSP430. Модуль таймера микроконтроллера. Блоки захвата/сравнения.

В таймере А представлено три одинаковых блока захвата/сравнения TACCRx. Любой из блоков может быть использован для фиксации (захвата) данных таймера или для генерации временных интервалов. Режим захвата выбирается, когда CAP=1. Режим захвата используется для регистрации временных событий. Это может потребоваться для быстрых вычислений или для измерения времени. Входы захвата CCIxA и CCIxB подключаются к внешним выводам или к внутренним сигналам и выбираются с помощью битов CCISx. Биты CMx определяют, как будет происходит захват:по фронту входного сигнала, по его спаду или в обоих случаях. Захват происходит по выбранному фронту входного сигнала. Если захват произошел, тогда: Значение таймера копируется в регистр TACCRx Устанавливается флаг прерывания CCIFG Уровень входного сигнала может быть прочитан в любое время через бит CCI. К входам CCIxA и CCIxB в устройствах семейства MSP430x1xx могут подключаться различные сигналы. См. справочное руководство конкретного устройства для выяснения особенностей подключения этих сигналов. Сигнал захвата может быть асинхронен тактовой частоте таймера и вызывать состояние гонки сигналов. Установка бита SCS будет синхронизировать захват со следующим тактовым импульсом таймера. Рекомендуется устанавливать бит SCS для синхронизации сигнала захвата с тактовыми импульсами таймера. Логика переполнения предусмотрена в каждом регистре захвата/сравнения для индикации в случае, если произошел второй захват перед прочтением значения первого захвата. Когда это происходит, устанавливается бит COV, как показано на рис. Бит COV должен сбрасываться программно. Инициирование захвата программным обеспечением Захваты могут быть инициированы программно. Биты CMx могут быть установлены для выполнения захвата по обоим фронтам. В этом случае программное обеспечение устанавливает CCI=1 и переключает бит CCISO для переключения сигнала захвата между VCC и GND, инициируя захват каждый раз, когда CCISO изменяет состояние: MOV #CAP+SCS+CCIS1+CM_3,&TACCTLx;Настройка TACCTLx XOR #CCIS0,&TACCTLx;TACCTLx = TAR

Режим сравнения выбирается, когда CAP=0. Режим сравнения использует- ся для генерации выходных ШИМ-сигналов или прерываний через конкретные временные интервалы. Когда TAR досчитывает до значения в TACCRx, происходит следующее:

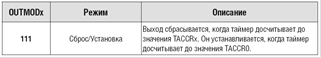

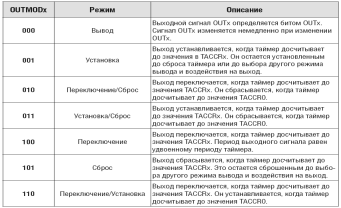

Устанавливается флаг прерывания CCIFG Внутренний сигнал EQU=1 EQUx воздействует на выход согласно режиму вывода Входной сигнал CCI фиксируется в SCCI Микроконтроллер MSP430. Модуль таймера микроконтроллера. Устройство вывода. Модуль вывода Каждый блок захвата/сравнения содержит модуль вывода. Модуль вывода используется для генерации выходных сигналов, в т.ч. таких, как ШИМ-сигналы. Каждый модуль вывода имеет восемь рабочих режимов, которые генерируют сигналы, основываясь на сигналах EQU0 и EQUx. Режимы вывода устанавливаются битами OUTMODx, их описание приведено в таблице 11-2. Сигнал OUTx изменяется с нарастающим фронтом тактового сигнала таймера во всех режимах, кроме режима 0. Режимы вывода 2, 3, 6 и 7 не используются для модуля вывода 0, потому что EQUx=EQU0.

Примечание: Переключение между режимами выводаПри переключении между режимами вывода один из битов OUTMODx должен оставаться установленным во время перехода, кроме переключения в режим 0. В противном случае может произойти сбой, поскольку режим вывода 0 декодирует элемент NOR (НЕ-ИЛИ). Безопасный метод переключения между режимами вывода заключается в использовании режима вывода 7 как переходного состояния: BIS #OUTMOD_7,&TACCTLx;Установка режима вывода 7 BIC #OUTMODx,&TACCTLx;Очистка лишних битов

38АЦП. Типы АЦП. Параллельного преобразования.

Рис. 3 Параллельный АЦП Такая архитектура предполагает использование большого числа резисторов и компараторов, имеет ограничение по максимальной разрешающей способности. Обычно параллельные АЦП имеют разрешающую способность, соответствующую 8-разрядам. Их максимальная частота дискретизации может достигать 1 ГГц.

|

||||||

|

Последнее изменение этой страницы: 2017-02-09; просмотров: 329; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.15.156.140 (0.007 с.) |

Параллельные АЦП являются самым быстрым типом АЦП, использующим большое количество компараторов, работающих параллельно, по этой причине АЦП называют параллельный. N-разрядный параллельный АЦП состоит из 2N резисторов и 2N–1 компараторов, размещенных, как это показано на рис. 3. На каждый компаратор подается опорное напряжение, значение которого для соседних точек отличается на величину, соответствующую одному младшему значащему разряду (LSB) (более старшие разряды — в верхних по схеме элементах). При фиксированном входном напряжении все компараторы, размещенные на схеме ниже некоторой точки, имеют входное напряжение выше опорного напряжения. На их логическом выходе присутствует "1". У всех же компараторов выше этой точки опорное напряжение больше входного, и их логический выход установлен в "0".

Параллельные АЦП являются самым быстрым типом АЦП, использующим большое количество компараторов, работающих параллельно, по этой причине АЦП называют параллельный. N-разрядный параллельный АЦП состоит из 2N резисторов и 2N–1 компараторов, размещенных, как это показано на рис. 3. На каждый компаратор подается опорное напряжение, значение которого для соседних точек отличается на величину, соответствующую одному младшему значащему разряду (LSB) (более старшие разряды — в верхних по схеме элементах). При фиксированном входном напряжении все компараторы, размещенные на схеме ниже некоторой точки, имеют входное напряжение выше опорного напряжения. На их логическом выходе присутствует "1". У всех же компараторов выше этой точки опорное напряжение больше входного, и их логический выход установлен в "0".