Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Структурная схема и состав УСДСтр 1 из 2Следующая ⇒

Курсовая работа «Устройство сбора данных»

Выполнил:

Москва 2009 Введение

Информационно-измерительные и управляющие цифровые микропроцессорные системы, к которым относится проектируемое устройство сбора данных (УСД), предназначены для измерения, сбора, обработки, хранения и отображения информации с реальных объектов. Такие системы используются практически во всех отраслях народного хозяйства для контроля и управления технологическими процессами, накопления статистических данных. В радиотехнических системах и в технике связи УСД используются для обработки сигналов, функционального контроля каналов связи, диагностирования состояния аппаратуры. Первичная информация в УСД поступает, как правило, по каналам от датчиков в виде аналогового напряжения. В УСД информационные каналы опрашиваются. Поступающие из них мгновенные отсчеты сигналов преобразуются в цифровую форму и помещаются в оперативное запоминающее устройство (ОЗУ) с целью последующей их обработки. Аппаратура УСД состоит из двух частей — операционного и управляющего устройств (ОУ и УУ). УУ является цифровым автоматом, который вырабатывает в некоторой временной последовательности управляющие сигналы. Существуют два принципиально разных подхода к проектированию микропрограммного автомата: использование принципа схемной логики и программной логики. Курсовой проект выполнен основываясь на принципах схемной логики. Задание

Спроектировать устройство сбора данных (УСД). Имеется F аналоговых каналов. Необходимо, опрашивая их согласно заданной последовательности, получаемые из каналов аналоговые величины с помощью АЦП преобразовывать в цифровую форму (двоичные слова стандартной длины 1 байт = 8 бит) и помещать в последовательные ячейки некоторой области ЗУ, начиная с ячейки, имеющей адрес G. Цифровая процессорная система, фрагментом которой является проектируемое УСД, имеет в своем составе ЗУ емкостью Q бит.

Требуется: 1. Исходя из задания разработать ОЗУ цифровой системы. 2. Разработать системы формирования адресов ячеек ОЗУ и номеров опрашиваемых каналов. 3. Реализовать УСД в виде процессорного устройства, построенного на принципах схемной логики, и привести его функциональную схему.

4. Синтезировать схему УУ. 5. Составить полную электрическую схему УСД.

Исходные данные приведены в таблице 1.Вариант 7 Таблица 1

Порядок опроса каналов задан в таблице 2. Таблица 2

Разработка блока выработки адреса ЗУ

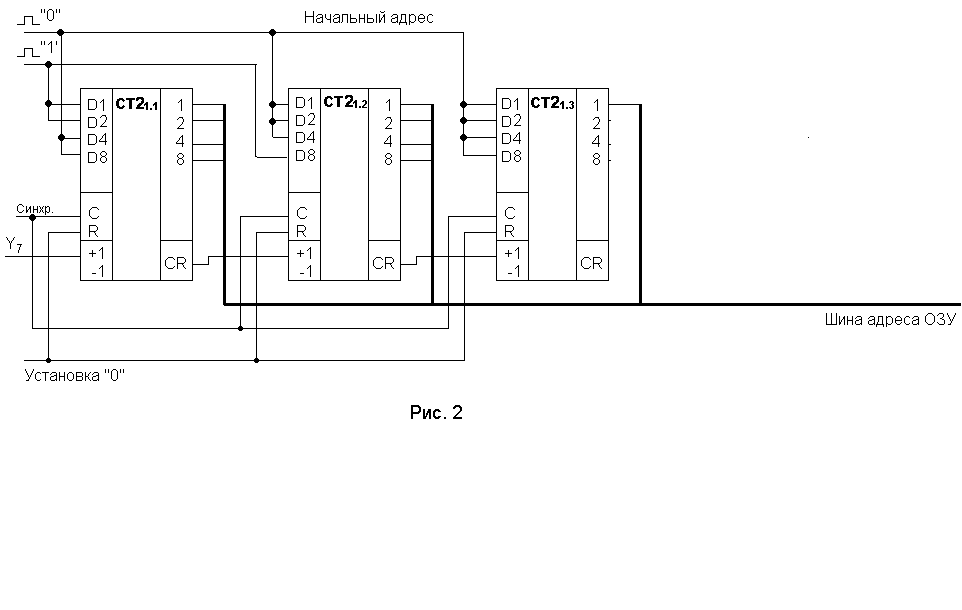

Требуется синтезировать устройство, которое, начиная с определенного начального адреса G, производить формирование последующих адресов, отличающихся друг от друга на единицу, размещение данных идёт в ячейки с последовательно возрастающими адресами. Разработку такого устройства можно осуществить с помощью счетчиков. Длина адресного слова определяется емкостью памяти.

Емкость памяти θ = 512 = 29

Начальный адрес ячейки памяти G = 0083 16 = 0000 0000 1000 00112

Блок будет содержать четыре четырехразрядных суммирующих двоичных счетчика с предустановкой. Схема блока представлена на рис. 2.

Абстрактный синтез УУ

На основе изложенного выше описания цикла сбора данных составляем блок-схему алгоритма функционирования:

Рис. 4

Анализ алгоритма показывает, что микрооперации y1, y2, а также y3, y4, y5 и y6, y7, y8 не зависят друг от друга и могут выполняться одновременно в одном такте. Следовательно, эти микрооперации в группах можно объединить в микрокоманды. Затем следует произвести разметку получившейся блок-схемы. Начало и конец блок-схемы обозначим a0, что соответствует исходному состоянию управляющего автомата. Вход каждого блока, следующего за операторными блоками, которые имеют прямоугольную форму, помечаем символами a1, a2, a3, соответствующими последующим состояниям УУ.

Рис.5

Далее на основе произведенной разметки блок-схемы алгоритма строится граф функционирования УСД. Каждому из состояний управляющего автомата соответствует узел графа, дугами графа изображаются переходы автомата из одного состояния в другое, причем возле каждой дуги указывается условие перехода X и выполняемая на данном тактовом интервале микрокоманда Y.

Рис.6 Список литературы

1. Лебедев О.Н. “Микросхемы памяти и их применение” – М.: Радио и связь, 1990. 2. Багданович М.И. “Цифровые и интегральные схемы” – Беларусь, 1981. 3. Калабеков Б.А. “Микропроцессоры и их применение в системах передачи и обработки сигналов” – М.: Радио и связь, 1998 4. Конспект лекций по ВТиИТ.

Курсовая работа «Устройство сбора данных»

Выполнил:

Москва 2009 Введение

Информационно-измерительные и управляющие цифровые микропроцессорные системы, к которым относится проектируемое устройство сбора данных (УСД), предназначены для измерения, сбора, обработки, хранения и отображения информации с реальных объектов. Такие системы используются практически во всех отраслях народного хозяйства для контроля и управления технологическими процессами, накопления статистических данных. В радиотехнических системах и в технике связи УСД используются для обработки сигналов, функционального контроля каналов связи, диагностирования состояния аппаратуры. Первичная информация в УСД поступает, как правило, по каналам от датчиков в виде аналогового напряжения. В УСД информационные каналы опрашиваются. Поступающие из них мгновенные отсчеты сигналов преобразуются в цифровую форму и помещаются в оперативное запоминающее устройство (ОЗУ) с целью последующей их обработки. Аппаратура УСД состоит из двух частей — операционного и управляющего устройств (ОУ и УУ). УУ является цифровым автоматом, который вырабатывает в некоторой временной последовательности управляющие сигналы. Существуют два принципиально разных подхода к проектированию микропрограммного автомата: использование принципа схемной логики и программной логики. Курсовой проект выполнен основываясь на принципах схемной логики. Задание

Спроектировать устройство сбора данных (УСД). Имеется F аналоговых каналов. Необходимо, опрашивая их согласно заданной последовательности, получаемые из каналов аналоговые величины с помощью АЦП преобразовывать в цифровую форму (двоичные слова стандартной длины 1 байт = 8 бит) и помещать в последовательные ячейки некоторой области ЗУ, начиная с ячейки, имеющей адрес G. Цифровая процессорная система, фрагментом которой является проектируемое УСД, имеет в своем составе ЗУ емкостью Q бит.

Требуется: 1. Исходя из задания разработать ОЗУ цифровой системы. 2. Разработать системы формирования адресов ячеек ОЗУ и номеров опрашиваемых каналов. 3. Реализовать УСД в виде процессорного устройства, построенного на принципах схемной логики, и привести его функциональную схему. 4. Синтезировать схему УУ. 5. Составить полную электрическую схему УСД.

Исходные данные приведены в таблице 1.Вариант 7

Таблица 1

Порядок опроса каналов задан в таблице 2. Таблица 2

Структурная схема и состав УСД

Структурная схема УСД приведена на рис. 1. В состав УСД входят: Мультиплексор (MS): имеет F аналоговых входов и m управляющих (адресных) входов. При подаче на адресный вход двоичного числа — адреса — происходит подключение одного из аналоговых каналов, имеющих данный адрес, к выходу MS. Число опрашиваемых аналоговых каналов связано с числом адресных входов k = 2m. АЦП: имеет 1 аналоговый вход и 8 выходов, по которым в двоичном, параллельном коде выдается число, соответствующее уровню поданного на вход АЦП отсчета аналогового сигнала. Перед началом работы АЦП на него должен быть подан сигнал запуска. АЦП выполняет преобразования за несколько тактов. После окончания преобразования АЦП выдает сигнал ОК (окончание преобразования) на устройство управления. Сигнал ОК - флаг (обозначается как Тфл), должен быть зафиксирован с помощью триггера до момента окончания записи данных опрашиваемого канала в ячейку памяти ОЗУ. MS и АЦП берутся как стандартные схемы с соответствующими характеристиками. Устройство управления на некоторых тактовых интервалах с учетом осведомительных сигналов, поступающих от других устройств (в дальнейшем такие сигналы обозначаются буквой Xi), формирует управляющие сигналы Yn, которые обеспечивают запуск других устройств и согласованную их работу.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 335; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.117.196.217 (0.031 с.) |