Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Однокристальные микроконтроллеры семейства MCS-51Содержание книги

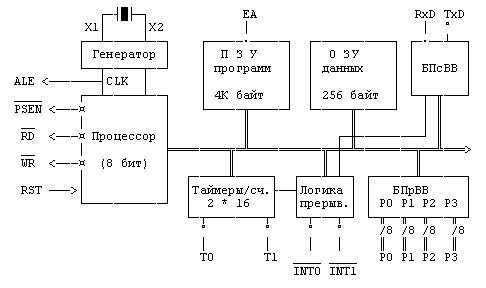

Поиск на нашем сайте Структура 80С51 Отдельный класс МП представляют однокристальные микроконтроллеры, являющиеся основной базой для построения встроенных систем управления нижнего уровня. Различными фирмами были разработаны ряды семейств однокристальных микроконтроллеров. Сегодня многие из них можно считать стандартными компонентами для построения встроенных МПС. Базовым представителем семейства MCS - 51 является микроконтроллер 80С51 фирмы INTEL. В СССР это микроконтроллеры выпускались на базе n-МОП технологии (серия 1816) и на базе КМОП технологии (серия 1830). Микроконтроллеры семейства MCS - 51 выпускаются многими другими фирмами. О собого внимания заслуживают:- АТ89СXX фирмы Atmel, имеющие большое число модификаций с широким набором периферии и различными комплектами встроенных ЗУ. Основные характеристики микроконтроллера 80С51: · восьмиразрядный ЦП, оптимизированный для реализации функций управления; · встроенный тактовый генератор; · адресное пространство памяти программ - 64 К; · адресное пространство памяти данных - 64 К; · внутренняя память программ - 4 К; · внутренняя память данных - 128 байт; · дополнительные возможности по выполнению побитовых операций булевой алгебры; · 32 двунаправленные и индивидуально адресуемые линии ввода/вывода; · 2 шестнадцатиразрядных таймера/счетчика; · полнодуплексный асинхронный приемопередатчик; · векторная система прерываний с двумя уровнями приоритета и шестью источниками событий Структурная схема I-8051 показана на рис.7.1.

Рис. 7.1. Структурная схема I-8051

В MCS-51 используются следующие сигналы: ALE - строб адреса; PSEN\ - строб чтения внешней памяти программ; RD\,WR\- стробы чтения и записи внешней памяти данных; EA\ - разрешение обращения во внутреннюю память программ; T0,T1 - входы счетчиков внешних событий; INT0,INT1- запросы внешних радиальных прерываний; RxD - вход данных последовательного канала; TxD - выход данных последовательного канала. В состав MCS-51 входят параллельные 8-разрядные квазидвунаправленные порты P0..P3. Порт Р3 может быть использован для ввода и вывода управляющих сигналов. Таким образом, в циклах обращения к внешним ресурсам на линиях порта P3 работают управляющие сигналы, а при отсутствии необходимости управления внешними ресурсами эти же линии могут быть использованы как линии порта.

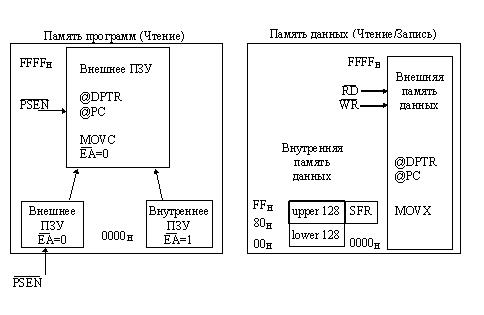

Организация памяти 80С51 MCS-51 имеет гарвардскую архитектуру, то есть раздельные адресные пространства памяти программ и данных. Организация памяти изображена на рис.7.2.

Рис.7.2. Организация памяти семейства MCS-51

Объем внутренней (резидентной) памяти программ (ROM, EPROM или OTP ROM), располагаемой на кристалле, в зависимости от типа микросхемы может составлять 0К (ROMless), 4К (базовый кристалл), 8К, 16К или 32К. При необходимости пользователь может расширять память программ установкой внешнего ПЗУ(ВПП). Доступ к ВПП возможен при выполнении двух условий: либо на вход отключения резидентной памяти программ (EA) подается активный сигнал, либо содержимое счетчика команд превышает значение 0FFFH.Доступ к внутреннему или внешнему ПЗУ определяется значением сигнала на выводе ЕА (External Access). Для кристаллов без ПЗУ (ROMless) вывод ЕА должен быть постоянно подключен к Vss(потенциал земли). Строб чтения внешнего ПЗУ – PSEN (Program Store Enable) генерируется при обращении к внешней памяти программ и является неактивным во время обращения к ПЗУ, расположенному на кристалле. Область нижних адресов памяти программ используется системой прерываний, архитектура микросхемы 8051обеспечивает поддержку пяти источников прерываний: · двух внешних прерываний; · двух прерываний от таймеров; · прерывания от последовательного порта.

Рис.7.3. Адреса векторов прерываний семейства MCS-51 Адреса векторов прерываний расположены с интервалом в 8 байт: · стартовый адрес при сбросе (вывод Reset); · внешнее прерывание EINT0 –INT0; · прерывание от таймера 0 –TF0; · внешнее прерывание EINT1 –INT1; · прерывание от таймера 1 –TF1; · прерывание от последовательного порта Serial Port. Память данных отделена от памяти программ. В этой области возможна адресация 64К внешнего ОЗУ. При обращении к внешней памяти данных ЦП микроконтроллера генерирует соответствующие сигналы чтения Нижние 128 байт внутренней памяти данных (lower 128) присутствуют на всех кристаллах MCS-51.Первые 32 байта представляют собой 4 банка (Register Bank) по 8 регистров (R7...R0). Регистры R0 и R1 в любом из банков могут использоваться в качестве регистров косвенного адреса. Следующие за регистровыми банками 16 байт образуют блок побитно-адресуемого пространства. Набор инструкций MCS-51 содержит широкий выбор операций над битами, а 128 бит в этом блоке адресуются прямо; адреса этих бит имеют значения от 00Н до 7FH. Все байты в нижней 128-байтной половине памяти могут адресоваться как прямо, так и косвенно. Рис. 7.4. Верхняя 128 байтная половина памяти ОЗУ (upper 128) в микросхеме I-8051 отсутствует, но имеется в версиях кристаллов с 256 байтами ОЗУ. В этом случае область "Upper 128" доступна только при косвенной адресации. Область SFR (Special Function Register) доступна только при прямой адресации. Размещение регистров специальных функций в пространстве SFR показано на рис. 7.5. Они включают в себя регистры портов, таймеры, средства управления периферией и так далее. Для 16 адресов в пространстве SFR имеется возможность как байтовой, так и битовой адресации. Для побитно-адресуемых регистров шестнадцатеричный адрес заканчивается на "0Н" или на "8Н". Битовые адреса в этой области имеют значения от 80Н до FFH. В кристаллах, представляющих собой дальнейшее развитие семейства MCS-51 в область SFR, добавляются новые регистры для расширения функциональных возможностей, например, матрица программируемых счетчиков (PCA), сторожевой таймер (WDT), аналого-цифровое преобразователь, синхронный последовательный интерфейс и так далее. Назначение регистров области SFR и отдельных битов этих регистров приведены ниже.

Рис.7.4. Организация нижней области ОЗУ семейства MCS-51 побитовая адресация

Рис.7.5. Организация области регистров специальных функций (SFR)

Аккумулятор А (E0H). Команды MCS-51 используют аккумулятор как источник и как приемник при вычислениях и пересылках. Регистр В (F0H). Регистр В используется как источник и как приемник при операциях умножения и деления., Регистр PSW (Слово состояния программы - D0H). Данный регистр содержит биты, отражающие результаты исполнения операций, биты выбора регистрового банка и бит общего назначения, доступный пользователю. PSW содержит:

Регистры портов Р0+Р3 (адреса 80Н, 90Н, А0Н, В0Н). Каждый порт является фиксатором - защелкой и может адресоваться как побайтно, так и побитно. Помимо работы в качестве обычных портов ввода/вывода, линии портов могут выполнять ряд альтернативных функций: · через порт 0 (в мультиплексном режиме) выводится младший байт адреса, а также выдается и принимается в микроконтроллер байт данных при работе с внешней памятью программ/данных. Задаются данные при программировании внутренней памяти программ и читается ее содержимое; · через порт 2 выводится байт старший байт адреса внешней памяти программ и данных, а также задаются старшие разряды адреса при программировании и верификации УФРПЗУ; · порт 1 предназначен для задания младшего байта адреса при программировании и проверке ПЗУ микросхемы. Линии порта используются также для обслуживания работы Т/С2 и модуля PCA (для тех версий кристаллов MCS-51, в составе которых имеются эти функциональные узлы); · порт 3 имеет следующие альтернативные функции: · Р3.7 - строб чтения из внешней памяти данных (Read Data for External Memory, · P3.6 - строб записи во внешнюю память данных (Write Data for External Memory, · P3.5 - внешний вход T/C1 (Timer/Counter 1 External Input, T1); · P3.4 - внешний вход T/C0 (Timer/Counter 0 External Input, T0); · P3.3 - вход внешнего прерывания 1 (External Interrupt 1 Input Pin, · P3.2 - вход внешнего прерывания 0 (External Interrupt 0 Input Pin, · P3.1 - выход данных передатчика последовательного порта (Serial Port Transmit Pin, TxD); · P3.0 - вход данных передатчика последовательного порта (Serial Port Receive Pin, RxD). Указатель стека SP (81Н). Используется для указания на вершину стека в операциях записи в стек и чтения из него. Неявно используется такими командами, как PUSH, RET, RETI, POP. По аппаратному сбросу от ЦП устанавливается в значение 07Н (область стека в этом случае начинается с адреса внутренней памяти данных 08Н) и инкрементируется при каждой записи в стек. Запись в SFR-регистр-SP (с использованием байтовой адресации) производится для предопределения положения стека во внутренней памяти данных. Указатель данных DPTR (Data Pointer, адреса 82Н, 83Н). Команды MCS-51 используют DPTR для пересылки данных, пересылки кода и для переходов (JMP@A+DPTR). DPTR состоит из двух регистров: младшего - DPL и старшего - DPH, обращение к ним - только байтовое. Регистр управления энергопотреблением PCON (Power Control Register, адрес 87Н). Для кристаллов, изготовленных по CHMOS-технологии, SFR-регистр PCON имеет следующее назначение битов: PCON.7 - бит удвоения скорости передачи (Double Baud Rate Bit, SMOD); PCON.6+PCON.4 - зарезервированы (Reserved); PCON.3, PCON.2 - флаги общего назначения (General Purpose Flags, GF1, GF0); PCON.1 - бит режима микропотребления (Power Down Bit, PD); PCON.0 - бит холостого режима (Idle Mode Bit, IDL). При установке холостого режима производится отключение ЦП при сохранении работоспособности внутрикристальных периферийных устройств и ОЗУ. В режиме микропотребления приостанавливаются все операции при сохранении данных в ОЗУ (потребление тока микроконтроллером в этом случае менее 10 мкА). Выход из режима микропотребления осуществляется аппаратным сбросом длительностью не менее 10 мс (время восстановления работы задающего генератора), выход из холостого режима может быть произведен активизацией любого разрешенного прерывания, либо по сигналу RESET длительностью не менее двух машинных циклов. Регистры таймеров/счетчиков TL0, TL1, TH0, TH1 (адреса 8АН, 8ВН, 8СН, 8DH). Образуют 16-битные (Low/High) регистры таймеров/счетчиков "Т/C0" и "Т/C1". Обращение к регистрам только байтовое. Регистры управления режимами таймеров/счетчиков TMOD, TCON (89Н и 88Н). Предназначены для управления работой таймерной секции микроконтроллера. Буфер последовательного порта SBUF (99Н). Представляет собой два отдельных регистра. При записи в SBUF загружается "буфер передачи" последовательного порта, при чтении SBUF считывается содержимое "буфера приема" последовательного порта. Регистр управления последовательным портом SCON (98Н) Предназначен для управления работой последовательного порта. Обращение к данному регистру может быть как байтовым, так и побитным. Регистр разрешения прерываний IE и регистр управления приоритетом прерывания IP (А8Н и В8Н). Поддерживают работу системы прерываний микроконтроллера. Внешние устройства 80С51

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 442; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.007 с.) |

или записи (

или записи ( ), взаимодействие с внутренней памятью данных осуществляется на командном уровне, при этом сигналы

), взаимодействие с внутренней памятью данных осуществляется на командном уровне, при этом сигналы

8 байт

8 байт );

); );

);