Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Лабораторный практикум по курсу «схемотехника».Содержание книги

Поиск на нашем сайте

ЛАБОРАТОРНЫЙ ПРАКТИКУМ ПО КУРСУ «СХЕМОТЕХНИКА».

Для моделирования схем предлагается использовать САПР Quartus II Web Edition

Рис. 1. Интерфейс пакета Quartus II

Опишем указанные на рис. 1 меню, панели и окна. Меню менеджера пакета: · File (Файл) New... (Новый…); Open... (Открыть…); Close... (Закрыть…); New Project Wizard... (Мастер нового проекта…); Open Project... (Открыть проект…); Save Project... (Сохранить проект…); Close Project (Закрыть проект); Save (Сохранить); Save As... (Сохранить как…); File Properties... (Свойства файла…); Create / Update (Создать / Обновить); Export... (Экспорт…); Page Setup... (Параметры страницы…); Print Preview (Предварительный просмотр); Print... (Печать…); Recent Files (Последние файлы); Exit (Выход). · Edit (Правка) Undo (Отменить); Redo (Повторить); Cut (Вырезать); Copy (Копировать); Paste (Вставить); Delete (Удалить); Select (Выбрать); Find and Replace (Найти и заменить); Go To... (Перейти к…); Insert (Вставить); Value (Значение); Grouping (Группирование); End Time... (Время окончания…); Grid Size... (Шаг сетки…); Sort... (Сортировать…); Properties (Свойства). · View (Вид) Utility Windows (Служебные окна); Full Screen (Развернуть на весь экран); Fit in Windows (Вписать в окно); Zoom In (Увеличить масштаб); Zoom Out (Уменьшить масштаб); Zoom... (Масштаб…); Compare to Waveforms in File... (Сравнить с временной диаграммой из файла…); Next Transition (Следующий фронт); Previous Transition (Предыдущий фронт); Show Absolute Times (Показывать абсолютное время); Show Time Relative to Master Time Bar (Показывать время относительно основного маркера); Show Comments (Показать комментарии); Snap to Transition (Привязка к фронту); Snap to Grid (Привязка к сетке); Display Format (Формат отображения); Nodes (Узлы). · Project (Проект) Add Current File to Project (Добавить текущий файл в проект); Add/Remove Files in Project... (Добавить / Удалить файлы в проекте…); Revisions... (Ревизия…); Copy Project... (Копировать проект…); Archive Project... (Упаковать проект в архив…); Restore Archived Project... (Распаковать проект из архива…); Generate Tcl File for Project... (Генерировать Tcl-файл для проекта…). · Assignments (Назначения) Device... (Устройство…); Pins... (Выводы…); Timing Analysis Settings... (Настройки временного анализа); Settings... (Настройки…); Assignment Editor (Редактор назначений); Pin Planner (Планировщик выводов); Import Assignments... (Импортировать назначения…); Export Assignments... (Экспортировать назначения…). · Processing (Обработка) Stop Processing (Остановить обработку); Start Compilation (Начать компиляцию); Analyze Current File (Анализировать текущий файл); Update Memory Initialization File (Обновить файл инициализации памяти); Compilation Report (Отчет о результатах компиляции); Start Compilation and Simulation (Начать компиляцию и симуляцию); Generate Functional Simulation Netlist (Генерировать список соединений для функциональной симуляции); Start Simulation (Начать симуляцию); Simulation Report (Отчет о результатах симуляции). · Window (Окно) New Window (Новое окно); Detach Window (Открепить окно); Close All (Закрыть все); Cascade (Отобразить каскадом); Tile Horizontally (Разместить горизонтально); Tile Vertically (Разместить вертикально). Панель инструментов Панель инструментов, изображенная на рис. 2, предназначена для размещения на ней элементов, вызывающих часто используемые функции, также доступные из меню менеджера проекта.

Рис. 2. Панель инструментов В табл. 1 приведены обозначения значков панели инструментов. Таблица 1

Навигатор проекта Закладка навигатора проекта “ Hierarchy ” отображает иерархию проекта, как показано на рис. 3.

Рис. 3. Закладка “Hierarchy” Закладка «Files» навигатора проекта (рис. 4) отображает: · Device Design Files (логические файлы проекта); · Software Files (файлы с программами); · Other Files (вспомогательные файлы проекта).

Рис. 4. Закладка «Files» Закладка «Design Units» навигатора проекта (рис. 5): · отображает все компоненты проекта; · использованный способ описания проекта и язык описания; · файл с описанием компонента.

Рис. 5. Закладка «Design Units» Окно процессора сообщений Окно сообщений, приведенное на рис. 7, отображает: · информационные сообщения (синий символ) – informational; · предупреждения (желтый символ) – warning; · сообщения об ошибках (красный символ) – error messages.

Рис. 7. Окно процессора сообщений Окно моделирования схемы Интерфейсное окно моделирования схемы представлено на рис. 9.

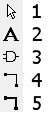

Рис. 9. Окно моделирования схемы Назначения основных кнопок окна моделирования схемы приведены ниже:

Кнопка 2 – позволяет добавлять текстовые пометки. Кнопка 3 – открывает диалог выбора элементов для добавления в схему. Кнопка 4 – позволяет рисовать одиночные проводники. Кнопка 5 – позволяет рисовать объединенные проводники (шины). Окно симуляции Интерфейсное окно симуляции представлено на рис. 10.

Рис. 10. Окно симуляции Назначения основных кнопок окна симуляции приведены ниже:

Кнопка 2 – действует аналогично, только устанавливает сигнал в логи-ческую единицу. Кнопка 3 – устанавливает сигнал в третье состояние. Кнопка 4 – инвертирует сигнал. Кнопка 5 – позволяет произвести двоичный пересчет для сгруппиро- ванных сигналов. Кнопка 6 – позволяет задать тактовый сигнал. Кнопка 7 – позволяет задать сигнал случайным образом. Остальные кнопки специфичные и при выполнении лабораторных работ не задействуются.

Шаг 2. Создание проекта Создаем новый проект (рис. 12). Для этого выбираем пункт меню File \ New Project Wizard.

Рис. 12. Выбор пункта меню File\New Project Wizard В появившемся диалоговом окне мастера-помощника создания проекта нажимаем кнопку Next и в ыбираем папку, где будет размещен проект. Например d :\ quartus \ quartus \ Lab 1. И указываем название проекта Lab 1, как показано на рис. 13.

Рис. 13. Окно мастера-помощника создания проекта Затем появляется окно, в котором спрашивается, нужно ли создать папку, которая еще не существует? Отвечаем – да, как показано на рис. 14.

Рис. 14. Окно для создания папки Нам предлагается добавить файлы проекта (рис. 15), но если у нас их нет, то нажимаем Finish.

Рис. 15. Возможность добавления файлов проекта Шаг 3. Создание файла схемы Чтобы создать новый файл разрабатываемой схемы, принадлежащий проекту, выбираем пункт меню File\New. Нам нужно создать файл, описывающий наше устройство. Это Design File. Выбираем рисование схемы Block Diagram \ Schematic File, как показано на рис. 16.

Рис. 16. Рисование схемы Block Diagram\Schematic File Шаг 4. Создание схемы 1. Добавление интегральной микросхемы Слева от поля графического редактора схем на панели инструментов (рис. 17) нажимаем иконку

Рис. 17. Кнопка Symbol Tool – вставить элемент Для добавления микросхемы, например мультиплексора КП7, в поле Name пишем серию микросхемы – 74151, и нажимаем ОК, как показано на рис. 18.

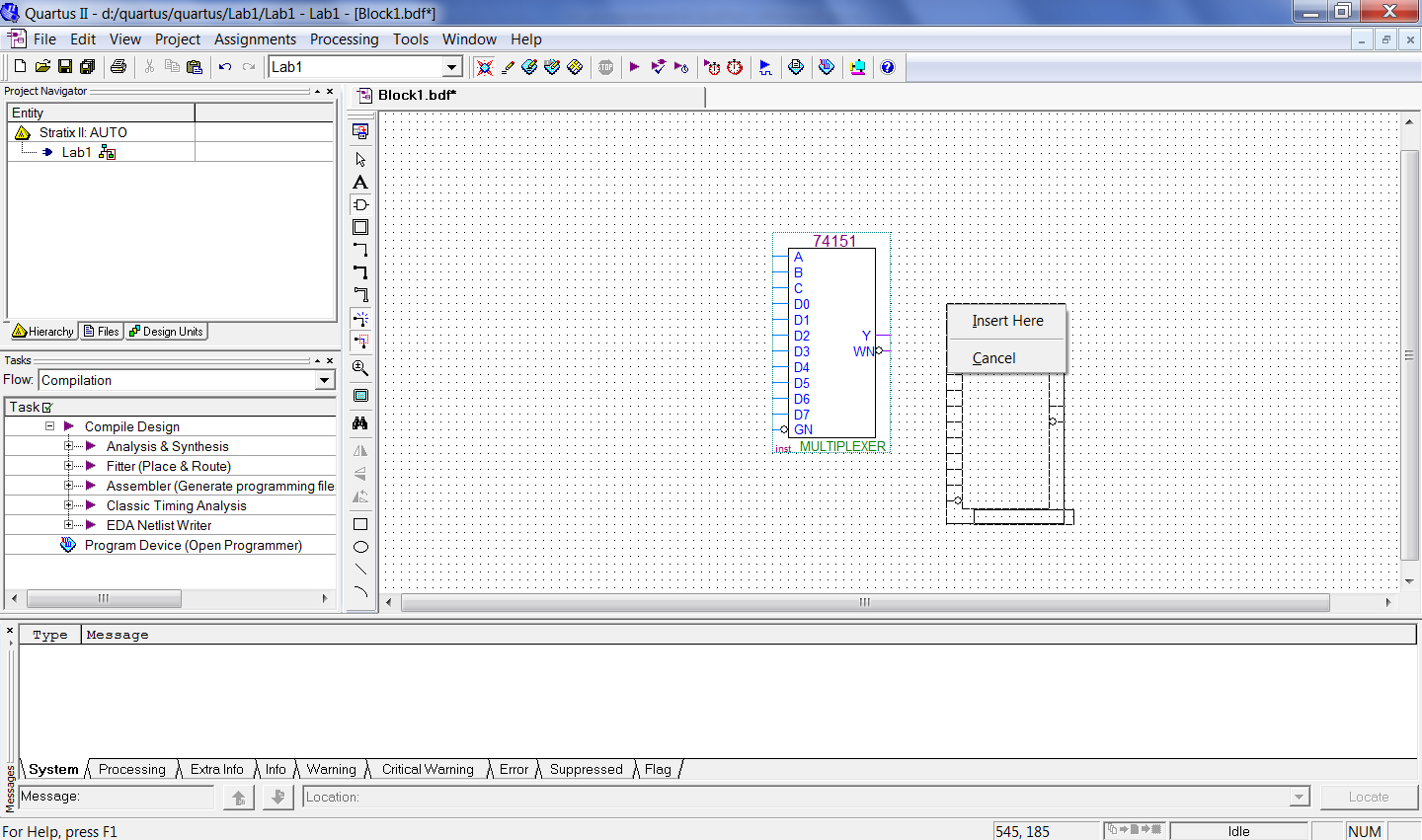

Рис. 18. Добавление микросхемы Затем нажимаем левой кнопкой мыши на поле графического редактора схем. Появляется микросхема. Если нужно еще несколько таких, то проделываем предыдущее действие, иначе нажимаем правую кнопку мыши и в выпадающем меню выбираем пункт Cancel – отмена, как видно на рис. 19.

Рис. 19. Процедура отказа от выбранного элемента 2. Добавление входов-выходов микросхемы Слева от поля графического редактора схем нажимаем на иконку

Рис. 20. Добавление pin\input На поле графического редактора схем (рис. 21) добавляем \ primitives \ other \ gnd (земля – логический ноль) и \ primitives \ other \ vcc (питание – логическая единица).

Рис.21 Добавление GND и VCC Для задания имен входов и выходов схемы следует задать их свойства. Для этого нажимаем правой кнопкой мыши на один из входов или выходов и в выпадающем меню выбираем пункт Properties – свойства, как показано на рис. 22.

Рис.22 Выбор свойств Properties входов-выходов Затем в поле Pin name(s) пишем имя входа или выхода, в зависимости от элемента, свойства которого вы изменяете (рис. 23).

Рис.23. Задание имени в поле Pin name (s) 3. Добавление связей Выбирая на панели инструментов иконку

Рис.24. Добавление связей Orthogonal Node Tool в схеме Шаг 5. Компиляция проекта Прежде чем делать симуляцию, нужно откомпилировать проект. Для этого выбираем пункты меню Processing \ Start Compilation. Шаг 6. Подготовка симуляции После того как выполнена компиляция проекта, нужно еще создать специальный netlist для функциональной симуляции. Для этого выбираем пункт меню Processing \ Generate Functional Simulation Netlist и сохраняем его, как показано на рис. 25. Вообще симуляция бывает временная и функциональная. Функциональная симуляция позволяет проверить именно логику работы. С ее помощью можно убедиться, что проект может и должен работать так, как задумано. Как правило, следует делать именно функциональную симуляцию. Временная симуляция позволяет увидеть сигналы с учетом всех возникающих задержек сигнала между элементами, входами и выходами. Временную симуляцию делают в последнюю очередь, уже после функциональной симуляции, чтобы убедиться, что схема может работать на нужной заданной частоте.

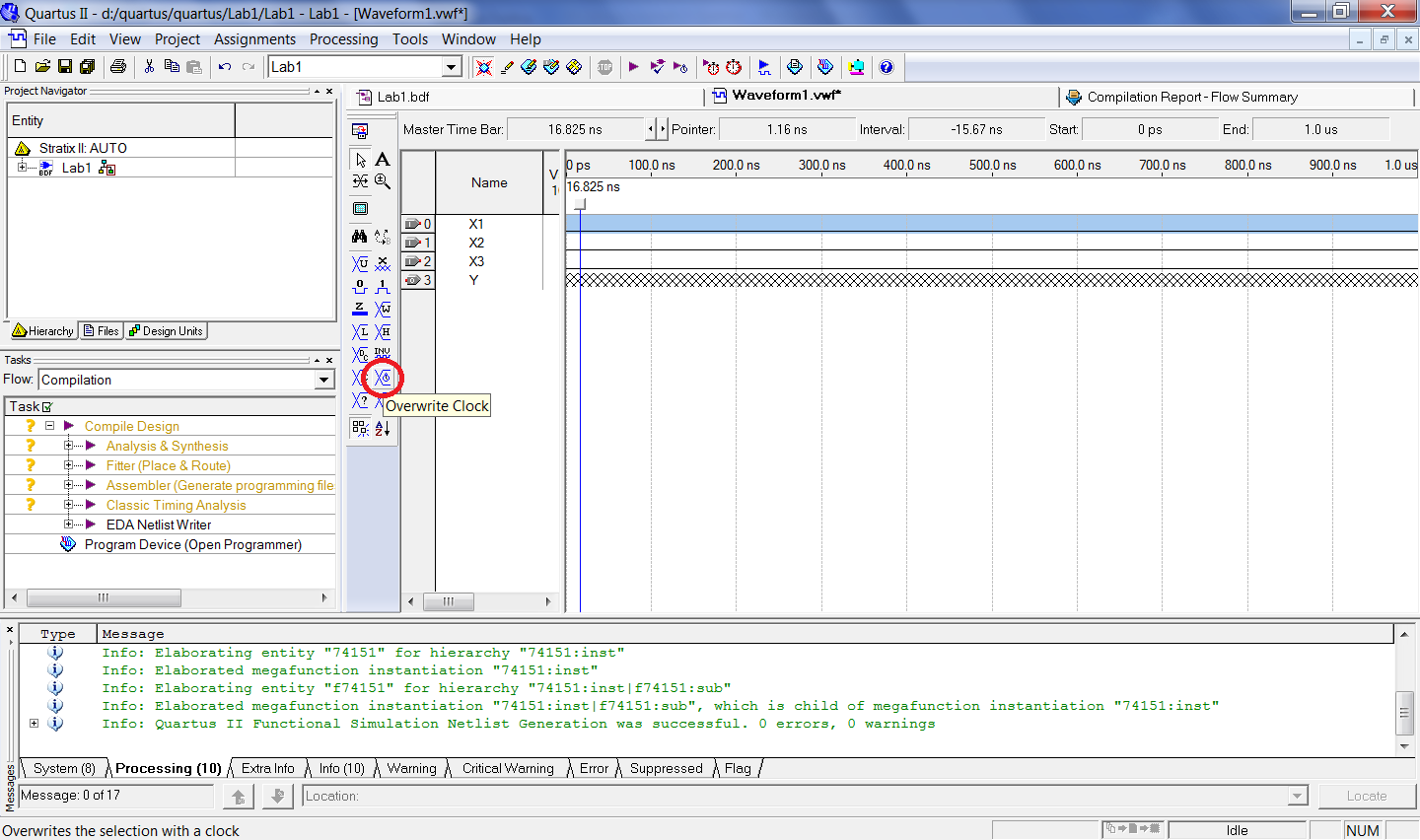

Рис.25. Создание специального netlist для функциональной симуляции Способ 1 (вручную) Выбираем сигнал, например, X 1 и нажимаем на панели инструментов кнопку Overwrite Clock, как показано на рис. 32. После этого появится диалоговое окно для задания тактовой частоты (рис. 33). Сейчас в этом диалоговом окне мы сможем задать поведение сигнала как тактовой частоты. Задаем для сигнала X 1 период тактовой частоты, например, 250ns, для сигнала X 2 – 500 ns, для сигнала X 3 – 1000 ns.

Рис. 32. Кнопка панели инструментов Overwrite Clock

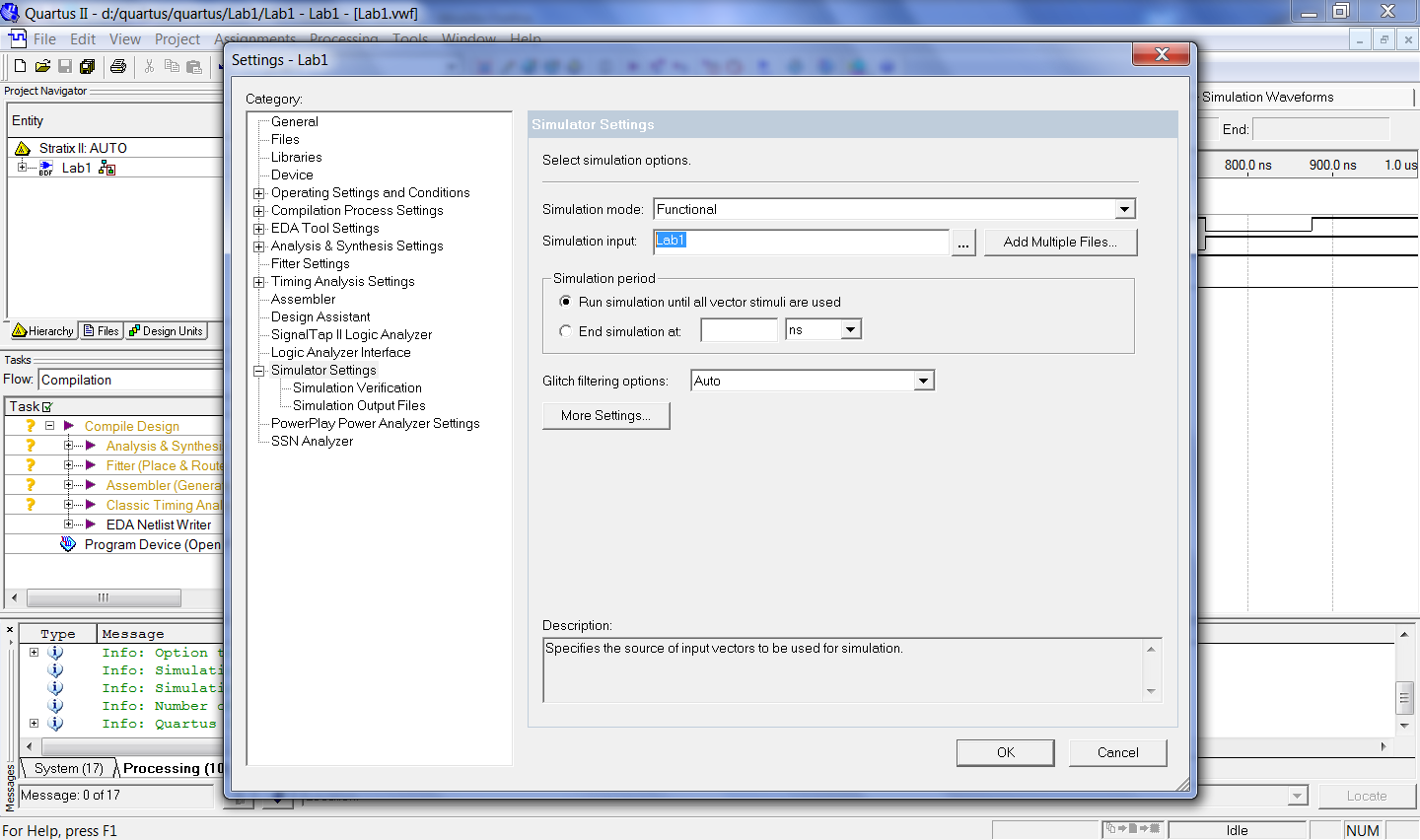

Рис. 33. Задание периода тактовой частоты 250ns для сигнала X 1 Затем нужно задать тип симуляции. Для этого следует зайти в пункт меню Assignment\Settings. В диалоговом окне Settings выбираем раздел Simulator Settings. Здесь нужно задать тип симуляции – Functional (функциональная). Задаем имя входного файла симуляции Lab 1 и нажимаем OK. Это наглядно отображено на рис. 34.

Рис. 34. Выбор типа симуляции

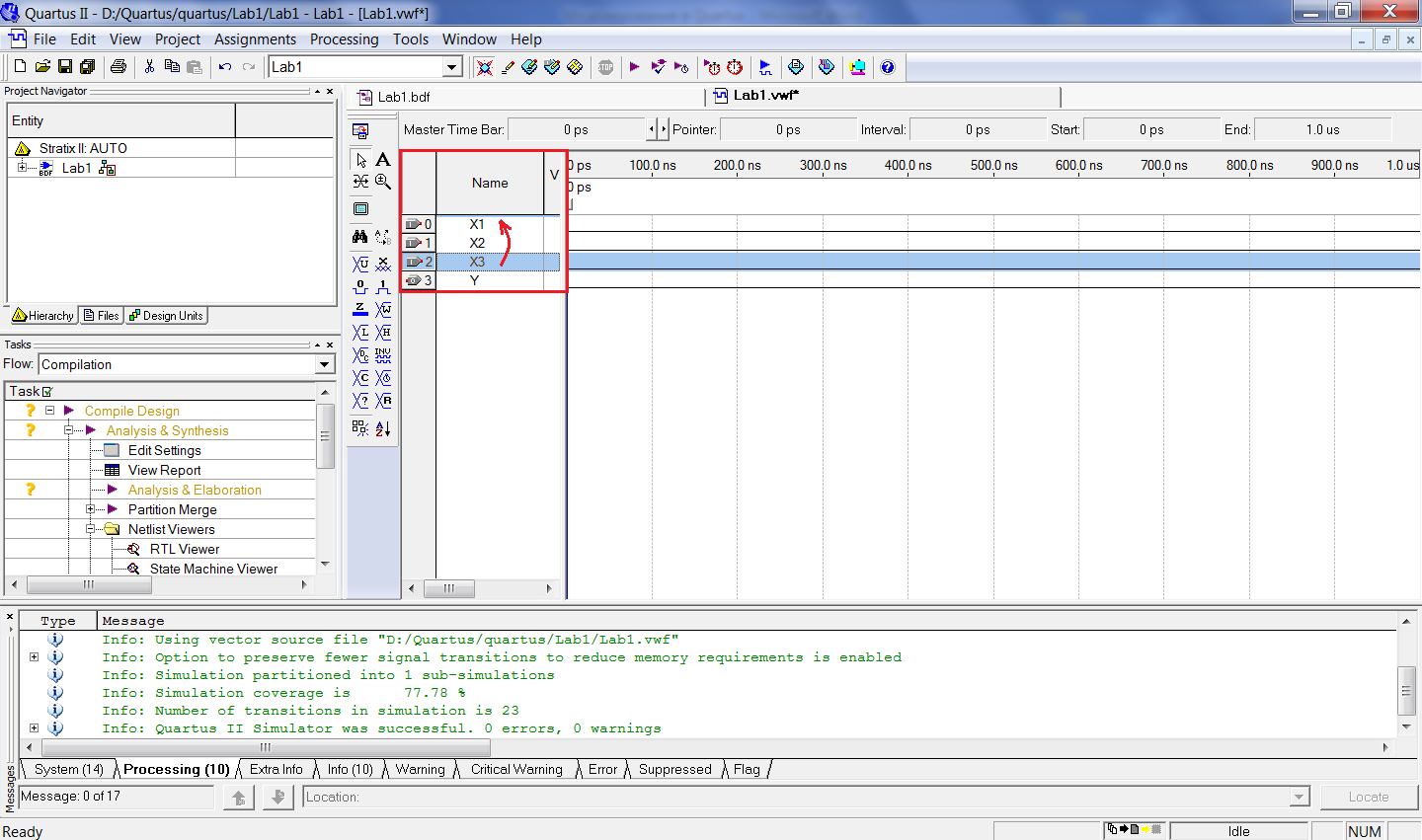

Запускаем симулятор из пункта меню Processing \ Start Simulation. После успешной симуляции можно рассмотреть сигналы на выходе Y, как показано на рис. 35.

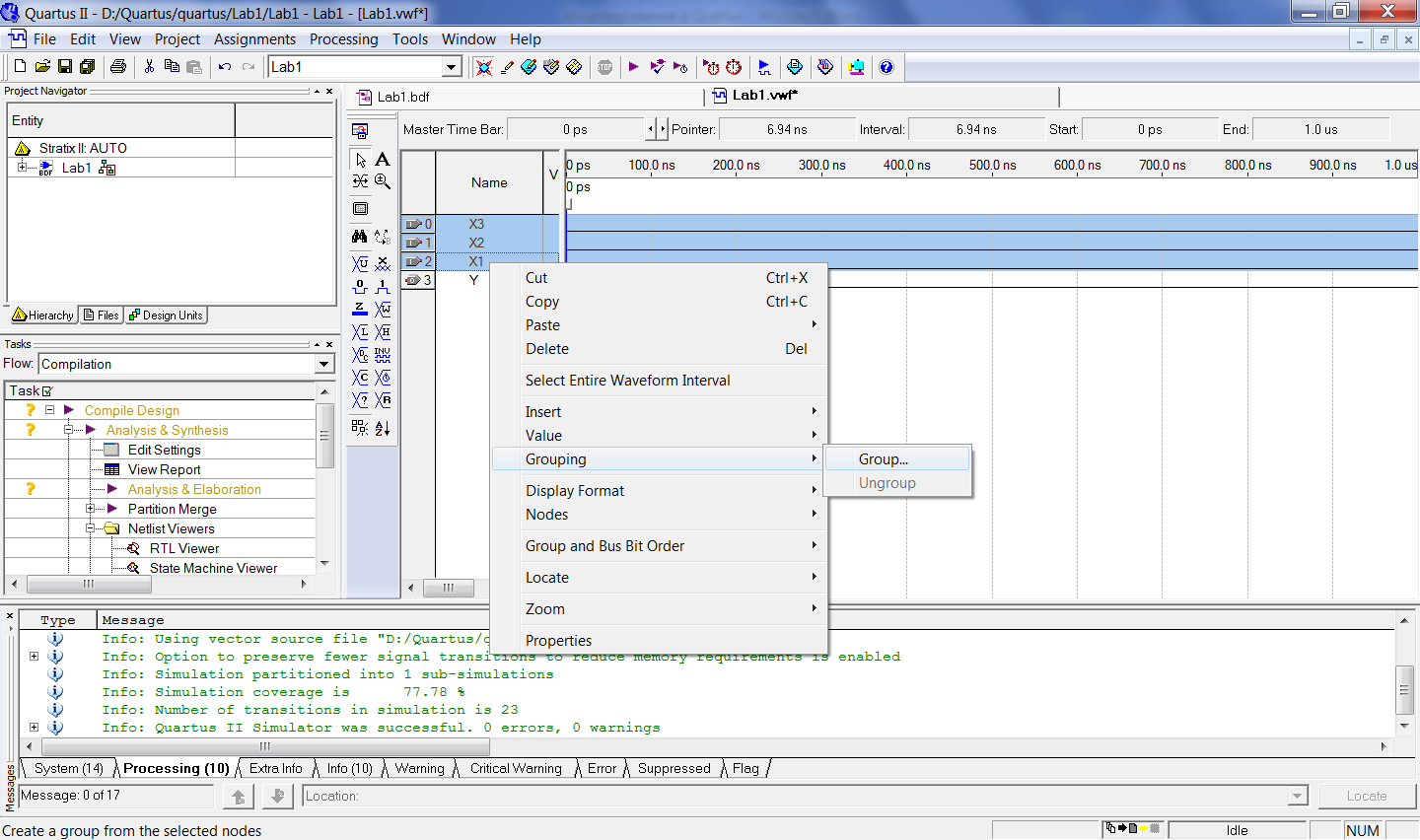

Рис. 35. Результат симуляции комбинационной схемы Способ 2 (автоматический) Для того чтобы автоматически задать пересчет всех возможных комбинаций входных сигналов в Quartus II, необходимо в столбце с именем Name расположить входные сигналы в порядке убывания: X 3, X 2, X 1. Для этого наводим курсор мыши на сигнал X 3, нажимаем левую кнопку мыши, и, не отпуская ее, перетаскиваем в нужную нам позицию, как показано на рис. 36. Затем аналогичные действия выполняем и для других сигналов.

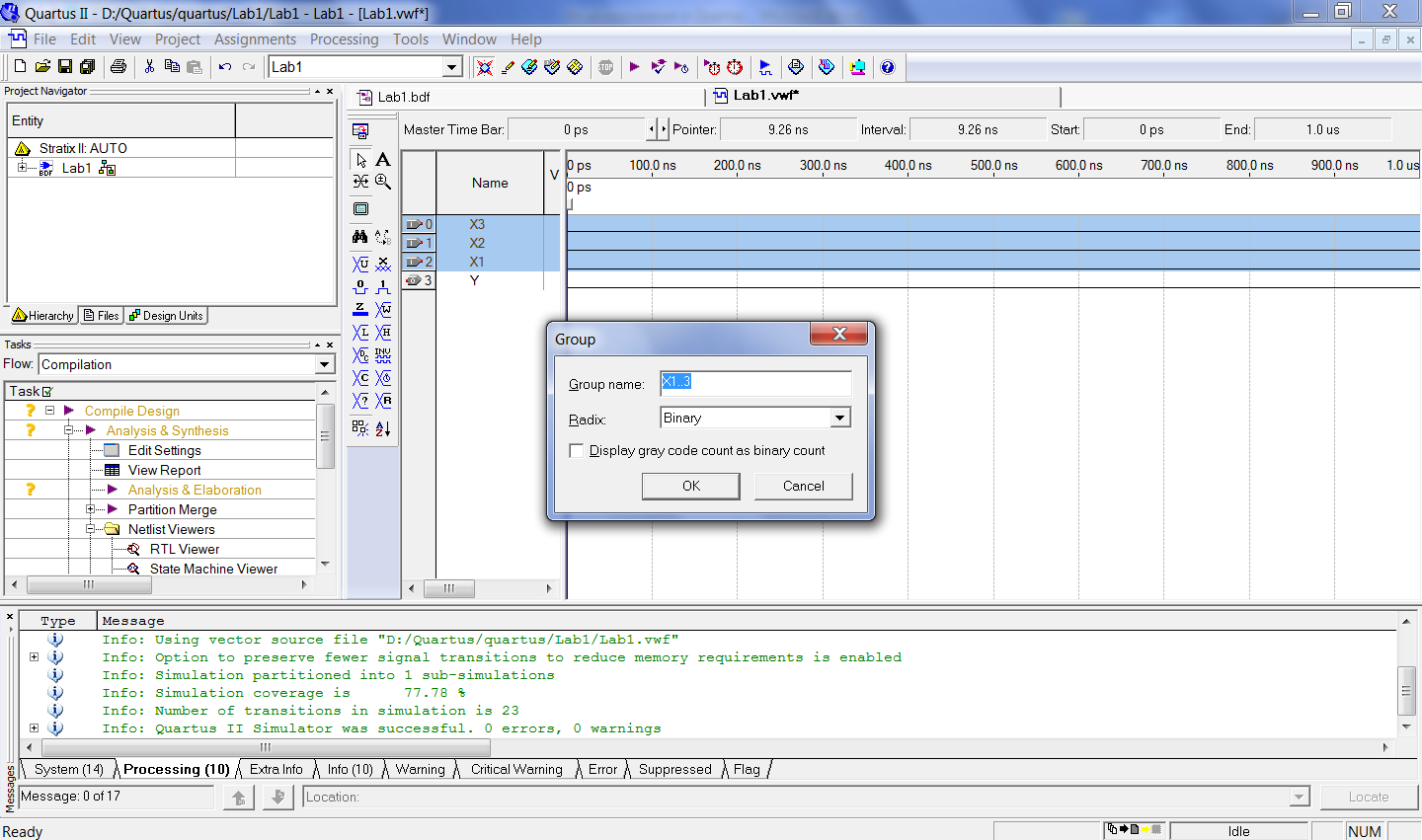

Рис. 36. Способ изменения позиции входных сигналов Теперь необходимо выделить входные сигналы и объединить их в группу. Для этого зажимаем клавишу Ctrl и наводим курсор мыши на каждый сигнал, щелкнув левой кнопкой мыши по нему. Так, мы выделили три сигнала. Теперь нажимаем правой кнопкой мыши на один из выделенных сигналов и в выпадающем меню выбираем пункт Grouping \ Group … – группа, как показано на рис. 37. В появившемся окне вводим в поле Group name (имя группы) – X 1..3. На рис. 38 показано, как мы выбираем Binary (двоичная) в раскрывающимся списке Radix (система счисления). После чего нажимаем кнопку ОК.

Рис. 37. Объединение входных сигналов в группу

Рис. 38. Задание имени группы и типа системы счисления После этого выбираем группу X 1..3 и нажимаем на панели инструментов кнопку В окне Count Value можно задавать параметры сигнала (рис. 39). Во вкладке Counting: Radix (система счисления), Start value (начальное значение), Increment by (шаг изменения) и Count type (тип счета).

Рис. 39. Способ задания параметров сигнала во вкладке Counting Во вкладке Timing: Start time (время начала), End time (время окончания), Count every (считать каждый) и Multiplied by (множитель) можно задать цифровое значение и размерность интервала Count every – 125нс, как показано на рис. 40, или любое другое, например 250 нс. После этого нажимаем кнопку ОК.

Рис. 40. Способ задания параметров сигнала во вкладке Timing Задать тип симуляции можно, как показано ранее на рис. 34. Для этого требуется зайти в пункт меню Assignment\Settings. Запускаем симулятор, как и раньше, из пункта меню Processing\Start Simulation. Результаты успешной симуляции представлены на рис. 41.

Рис. 41. Результаты успешной симуляции вторым способом ЛАБОРАТОРНЫЙ ПРАКТИКУМ ПО КУРСУ «СХЕМОТЕХНИКА».

Для моделирования схем предлагается использовать САПР Quartus II Web Edition

Рис. 1. Интерфейс пакета Quartus II

Опишем указанные на рис. 1 меню, панели и окна. Меню менеджера пакета: · File (Файл) New... (Новый…); Open... (Открыть…); Close... (Закрыть…); New Project Wizard... (Мастер нового проекта…); Open Project... (Открыть проект…); Save Project... (Сохранить проект…); Close Project (Закрыть проект); Save (Сохранить); Save As... (Сохранить как…); File Properties... (Свойства файла…); Create / Update (Создать / Обновить); Export... (Экспорт…); Page Setup... (Параметры страницы…); Print Preview (Предварительный просмотр); Print... (Печать…); Recent Files (Последние файлы); Exit (Выход). · Edit (Правка) Undo (Отменить); Redo (Повторить); Cut (Вырезать); Copy (Копировать); Paste (Вставить); Delete (Удалить); Select (Выбрать); Find and Replace (Найти и заменить); Go To... (Перейти к…); Insert (Вставить); Value (Значение); Grouping (Группирование); End Time... (Время окончания…); Grid Size... (Шаг сетки…); Sort... (Сортировать…); Properties (Свойства). · View (Вид) Utility Windows (Служебные окна); Full Screen (Развернуть на весь экран); Fit in Windows (Вписать в окно); Zoom In (Увеличить масштаб); Zoom Out (Уменьшить масштаб); Zoom... (Масштаб…); Compare to Waveforms in File... (Сравнить с временной диаграммой из файла…); Next Transition (Следующий фронт); Previous Transition (Предыдущий фронт); Show Absolute Times (Показывать абсолютное время); Show Time Relative to Master Time Bar (Показывать время относительно основного маркера); Show Comments (Показать комментарии); Snap to Transition (Привязка к фронту); Snap to Grid (Привязка к сетке); Display Format (Формат отображения); Nodes (Узлы). · Project (Проект) Add Current File to Project (Добавить текущий файл в проект); Add/Remove Files in Project... (Добавить / Удалить файлы в проекте…); Revisions... (Ревизия…); Copy Project... (Копировать проект…); Archive Project... (Упаковать проект в архив…); Restore Archived Project... (Распаковать проект из архива…); Generate Tcl File for Project... (Генерировать Tcl-файл для проекта…). · Assignments (Назначения) Device... (Устройство…); Pins... (Выводы…); Timing Analysis Settings... (Настройки временного анализа); Settings... (Настройки…); Assignment Editor (Редактор назначений); Pin Planner (Планировщик выводов); Import Assignments... (Импортировать назначения…); Export Assignments... (Экспортировать назначения…). · Processing (Обработка) Stop Processing (Остановить обработку); Start Compilation (Начать компиляцию); Analyze Current File (Анализировать текущий файл); Update Memory Initialization File (Обновить файл инициализации памяти); Compilation Report (Отчет о результатах компиляции); Start Compilation and Simulation (Начать компиляцию и симуляцию); Generate Functional Simulation Netlist (Генерировать список соединений для функциональной симуляции); Start Simulation (Начать симуляцию); Simulation Report (Отчет о результатах симуляции). · Window (Окно) New Window (Новое окно); Detach Window (Открепить окно); Close All (Закрыть все); Cascade (Отобразить каскадом); Tile Horizontally (Разместить горизонтально); Tile Vertically (Разместить вертикально). Панель инструментов Панель инструментов, изображенная на рис. 2, предназначена для размещения на ней элементов, вызывающих часто используемые функции, также доступные из меню менеджера проекта.

Рис. 2. Панель инструментов В табл. 1 приведены обозначения значков панели инструментов. Таблица 1

Навигатор проекта Закладка навигатора проекта “ Hierarchy ” отображает иерархию проекта, как показано на рис. 3.

Рис. 3. Закладка “Hierarchy” Закладка «Files» навигатора проекта (рис. 4) отображает: · Device Design Files (логические файлы проекта); · Software Files (файлы с программами); · Other Files (вспомогательные файлы проекта).

Рис. 4. Закладка «Files» Закладка «Design Units» навигатора проекта (рис. 5): · отображает все компоненты проекта; · использованный способ описания проекта и язык описания; · файл с описанием компонента.

Рис. 5. Закладка «Design Units»

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-09; просмотров: 719; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.126.51 (0.01 с.) |

Кнопка 1 – позволяет выделять и перемещать объекты.

Кнопка 1 – позволяет выделять и перемещать объекты.

Кнопка 1 – устанавливает сигнал в логический ноль на протяжении всего времени симуляции либо на выделенном отрезке.

Кнопка 1 – устанавливает сигнал в логический ноль на протяжении всего времени симуляции либо на выделенном отрезке.

Symbol Tool – вставить элемент.

Symbol Tool – вставить элемент.

– Orthogonal Node Tool, можно рисовать связи в нашей схеме. Начнем их рисовать, как показано на рис. 24.

– Orthogonal Node Tool, можно рисовать связи в нашей схеме. Начнем их рисовать, как показано на рис. 24.

Count Value.

Count Value.