Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Формат передачі по асинхронному інтерфейсу.Содержание книги

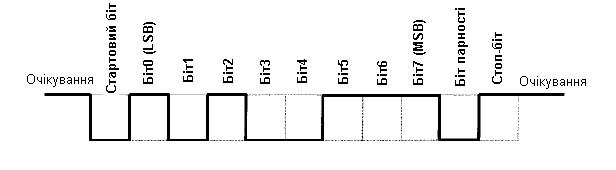

Поиск на нашем сайте У відповідності до стандарту V.24, в лінії передачі даних у стані очікування встановлена логічна 1. Передача може бути розпочата у будь-який момент часу. Для того, щоб передати приймачу повідомлення про початок передачі, посилається стартовий біт з рівнем логічного 0. після цього слідують розряди даних (у більшості випадків 7 або 8, їх число призначається у протоколі передачі даних), при цьому спочатку передається молодший біт. Для підвищення надійності передачі даних може бути добавлений біт парності. Біт парності доповнює розряди даних таким чином, що досягається пряма парність (сума усіх бітів, в тому числі біт парності, парна) або непряма парність (сума усіх бітів, в тому числі біт парності, непарна). Необхідний вид парності (відсутність, пряма, непряма) також повинен бути оголошений у протоколі передачі даних. Передача закінчується стоп-бітом з рівнем логічної 1, який в деяких мікроконтролерах може бути запрограмований з протяжністю 1; 1.5 або 2 довжини біта. Після відправлення стоп-біта лінія даних знову переходить у вихідний стан очікування і готова до наступної передачі. Часова діаграма передачі байта #Е5 (11100101b) з непрямою парністю і стоп-бітом через інтерфейс типу V.24 наведена на рис. 4.

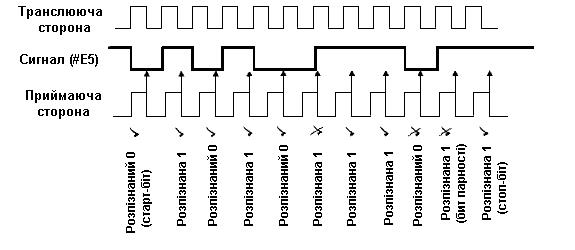

Рис.4. Часова діаграма передачі байта #Е5 (11100101b) з непрямою парністю і стоп-бітом через інтерфейс типу V.24. У зв’язку з тим, що такт для синхронізації передачі не пересилається, початок розряду може бути розпізнаний тільки за допомогою вимірювання часу, який пройшов з моменту появи спадаючого фронту стартового біта. Саме для цього потрібно встановлювати швидкість передачі даних, яка являється обов’язковою для передаючої і приймаючої сторони. Ці швидкості визначені в стандарті інтерфейсу RS232C і для уникнення помилок при розпізнаванні окремих розрядів їх необхідно дотримуватися. Наслідок суттєвої різниці між тактами передачі і прийому, а також випадку, коли передача здійснюється по наростаючому фронту такту, а опитування на стороні приймача – по спадаючому, який може попадати в середину імпульсу даних наведені на рис.5.

Рис.5. Вплив різних тактів передачі на транслюючій і приймаючій стороні.

На рис.5 зображений випадок, коли розряд 4 і розряд 7, а також біт парності розпізнані не правильно. Оскільки, в цьому прикладі оголошена непряма парність, то помилка може бути помічена за допомогою біта парності, так як байт розпізнаний як #75 і встановлений біт парності дають в результаті пряму парність, але при виникненні двох помилок біт парності про це не просигналізував би. Відмінність у тактах на транслюючій та приймаючій стороні в розглянутому прикладі складає 20%, що не допускається. Для уникнення помилок і для забезпечення надійної передачі даних слід уникати відхилень, що перевищують 3%. Послідовний порт може працювати в чотирьох режимах. Режим 0. 8 бітів даних (LSD перший). Швидкість передачі фіксована (1/12 частоти генератора fosc). Режим 1. 10 бітів передаються/приймаються: старт-біт (0), 8-бітів даних (LSB перший) і стоп-біт. При прийомі стоп-біт переміщується в RB8 регістра SCON. Швидкість передачі змінна. Режим 2. передача/прийом здійснюється 11-бітним словом: старт-біт (0), 8 бітів даних, програмований 9-ий біт (біт парності) і стоп-біт. При передачі 9-ий біт даних (TB8 в SCON) може містити „0” або „1”. При прийомі, 9-ий біт прямує в RB8 регістра SCON. Швидкість передачі 1/32 або 1/64 частоти генератора. Режим 3. передача/прийом здійснюється 11-бітним словом. Режим 3 аналогічний режиму 2 лише швидкість передачі даних є зміна. Для роботи з послідовним портом виділено два регістри: SCON (Serial Port Control Register) – призначений для управління функціями прийомопередавача та регістр даних; SBUF (Serial Data Buffer) – регістр даних, фізично складається з двох регістрів (звернення до цих регістрів відбувається за однією адресою, причому один з них використовується для передачі, а інший – для прийому даних). Мультипроцесорний зв’язок. Режим 2 і 3 має спеціальне забезпечення для мультипроцесорного зв’язку. В цьому режимі приймається 9 бітів даних, 9-ий біт поступає в RB8. Порт може бути запрограмований так, що коли отриманий стоп-біт, то переривання від послідовного порту буде активоване якщо RB8=1 (SM2=1). Цей режим надає можливість передачі даних між декількома пристроями. Прийом призначається в режимі 0 умовою RI=0 і REN=1, прийом введений в інші режими прийнятим стартовим бітом якщо REN=1. На рис.6 наведений вигляд регістра конфігурації.

Рис.6. Регістр конфігурації SCON.

Бод рейт (Baud Rates) В режимі 0 бод рейт фіксований і визначається наступною формулою

в режимі 2 бод рейт визначається бітом SMOD регістра PCON. Якщо SMOD=0 (значення за замовчуванням) бод рейт рівний 1/64 частоти генератора, як показано нижче

В AT89C51 переповнення таймера1 (Timer1) визначає бод рейт при використанні режимів 1 та 3. Використання таймера1 для генерування бод рейту. Коли таймер (Timer1) визначає (задає) бод рейт для режимів 1 та 3, то він визначається переповненням таймера і значенням SMOD:

для цого режиму повинно бути встановлено переривання від таймера (Timer1). Для найбільш поширеного випадку (при наступних настроюваннях TMOD=0010b) швидкість передачі визначається наступною формулою

За допомогою таймера1 можна досягти дуже низької швидкості передачі, якщо його сконфігурувати як 16-бітний (TMOD=0001b). В таблиці 7 наведені значення бод рейту і як вони можуть бути отримані за допомогою таймера.

У режимі 0 послідовний порт являє собою 8-розрядний регістр зсуву. Байт інформації передається через вивід RxD, при цьому через вивід TxD видаються сигнали синхронізації зсуву. Приймання і видача байта починається з молодшого розряду і закінчується старшим. Швидкість обміну фіксована і дорівнює 1/12 частоти синхронізації ОМК. Передавання починається з будь-якої команди, яка використовує буфер приймача-передавача SBUF як регістр призначення, наприклад MOV SBUF,A.

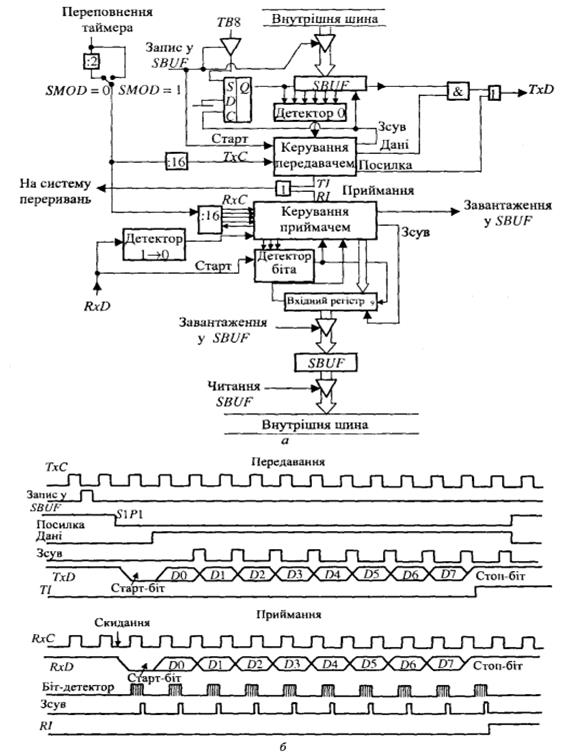

Рис.7. Послідовний порт в режимі 0: а – функціональна схема; б – діаграми.

У фазі Р2 стану S6 (S6P2) пристрій керування за сигналом «Запис у SBUF» записує байт у peгicтp зсуву передавача, встановлює D-тригер дев'ятого біта в одиницю та ініціює роботу блока керування передавачем. Останній через один машинний цикл формує сигнал дозволу «Посилка», який дозволяє видачу вмісту регістра зсуву передавача на вивід RxD та сигналу «Синхронізація зсуву» на вивід TxD. За сигналом «Зсув» у момент S6P2 кожного машинного циклу вміст peгicтpa зсуву передавача зсувається праворуч на одну позицію молодшими бітами вперед інадходить на bивід RxD. У старші біти peгicтpa зсуву передавача, що звільняються, записуються нулі. При отриманні від детектора нуля сигналу „Передавач звільнений” блок керування передавачем знімає сигнал «Посилка» i встановлює біт переривання передавача ТІ на початку інтервалу S1P1 десятого машинного циклу після надходження сигналу «Запис у SBUF». Приймання починається при одночасному виконанні умов REN=1 і RI = 0. На початку інтервалу S6P2 наступного машинного циклу (рис. 7 ) блок керування приймачем формує сигнал дозволу «Приймання», за яким на вивід TxD передаються синхросигнали зсуву, i в peгістрі зсуву приймача починають формуватися значення бітів даних, які зчитуються з виводу RxD в інтервалі S5P2 кожного машинного циклу. В інтервалі S6P2 кожного машинного циклу за сигналом «Зсув» здійснюється зсув вмісту регістра зсуву приймача ліворуч на одну позицію, i прийнятий біт записується у крайній правий розряд. Після надходження восьмого імпульсу «Зсув» вміст peгістрa приймача переписується у SBUF. В інтервалі S1P1 десятого машинного циклу блок керування приймачем переписує вміст регістра зсуву в буфер SBUF, знімає сигнал «Приймання» та встановлює біт переривання приймача RI в одиницю. У режимі 1 послідовний порт являє собою 8-розрядний універсальний асинхронний приймач-передавач зі змінною швидкістю обміну. Через TxD передаються, а через RxD приймаються 10 біт: нульовий старт-біт, 8 біт інформації та одиничний стоп-біт. Швидкість обміну є змінною. Бона визначається частотою переповнення таймера 1 ібітом SMOD регістра PCON. На рис. 8, показано функціональну схему i діаграми послідовного порту в режимі 1. Передавання починається з будь-яко'1 команди, що використовує SBUF як peгicтp призначення, наприклад: MOV SBUF, #25; переслати в SBUF число 25 Пристрій керування ОМК за сигналом «Запис у SBUF» завантажує 1 у дев'ятий біт регістра зсуву передавача, ініціює роботу блока керування передавачем i в інтервалі S1Р1 формує сигнал дозволу «Посилка» низького рівня. За цим сигналом на вивід TxD спочатку надходить старт-біт, а потам за сигналом дозволу «Дані» та імпульсами «Зсув» вміст регістра передавача зсувається на одну позицію, i на вивід TxD по черзі надходять 8 біт даних. За дев'ятим імпульсом «Зсув» формується одиничний стоп-біт, біт ТІ встановлюється в нуль, сигнали «Посилка» i «Дані» знімаються, i передавання закінчується. Приймання починається при переході сигналу на вході RxD з одиниці в нуль, який виявляється за допомогою детектора спадання. Як тільки перехід з одиниці в нуль виявлений, у регістр зсуву приймача завантажується число 1FFH, тобто всі 9 розрядів регістра заповнюються одиницями. При переході сигналу на вході RxD з одиниці в нуль також скидається значення внутрішнього лічильника-подільника частота на 16, який формує сигнал «Синхронізація приймача». Внутрішній лічильник починає відраховувати імпульси синхронізації. Під час сьомого, восьмого та дев'ятого імпульсів здійснюється опитування сигналу на вході RxD для підтвердження нульового значення старт-біта. Отримані три значення прийнятого біта надходять на детектор біта, який визначає дійсне значення прийнятого біта за мажоритарним принципом «два з трьох». У тому випадку, якщо дійсне значення старт-біта дорівнює нулю, починається приймання по черзі 8 біт даних. Значення кожного біта даних також перевіряється детектором біта в сьомому, восьмому та дев'ятому імпульсах сигналу «Синхронізація приймача» i лише після цього заноситься в регістр зсуву приймача. Якщо значення старт-біта не дорівнює нулю, то блок керування прийманням знову починає пошук переходів сигналу на вході RxD з одиниці в нуль. . Рис.8. Послідовний порт в режимі 1: а – функціональна схема; б – діаграми.

Приймання старт-біта та 8 біт даних у кожному машинному циклі супроводжується зсувом вмісту регістра приймача на одну позицію за сигналом «Зсув». Після прийняття старт-біта та 8 біт даних приймається стоп-біт, значення якого обов'язково має бути одиничним. Отже, після десятого імпульсу «Зсув» у регістрі приймача знаходяться 8 біт інформації i стоп-біт. Блок керування прийманням формує сигнал «Завантаження буфера», за яким вісім інформаційних бітів надходять у SBUF, стоп-біт - у розряд RB8 регістра SCON. Біт переривання приймача RI встановлюється в нуль. Приймання закінчується, i послідовний порт знову починає процес виявлення переходу сигналу на вході RxD з одиниці в нуль. У режимах 2 i 3 послідовний порт являє собою 9-розрядний універсальний синхронний приймач-передавач із фіксованою (для режиму 2) та змінною (для режиму 3) швидкістю обміну. У режимі 2 швидкість обміну дорівнює fOSC/32 при SMOD = 1 або fOSC/64 при SMOD = 0. У режимі 3 швидкість обміну визначається таймером 1, як i в режимі 1.

Рис.9. Послідовний порт в режимі 2: а – функціональна схема; б – діаграми. На рис. 9, а показано функціональну схему, а на рис. 9, б - діаграми послідовного порту в режимі 2. Функціональна схема послідовного порту в режимі 3 збігається зі схемою на рис. 8, а, а діаграми - з діаграмами на рис. 9, б. Через вивід TxD послідовний порт передає або з виходу RxD приймає 11 біт: нульовий старт-біт, 8 біт даних, програмований дев'ятий біт TB8 та одиничний стоп-біт. Режими 2 i 3 відрізняються від режиму 1 лише наявністю дев'ятого програмованого біта. Унаслідок цього змінюються умови закінчення циклу приймання: блок керування прийманням формує сигнал керування «Завантаження буфера», завантажує стоп-біт у розряд RB8 регістра SCON i встановлює біт переривання приймача RI в одиницю лише в тому разі, якщо в останньому такті зсуву виконуються дві умови: RI = 0 та SM2 = 0 або значення дев'ятого прийнятого біта даних дорівнює одиниці. Приклад програми до лабораторної роботи.

P3 data 0B0h;адреса порту Р3 SCON data 098h;адресація регістра конфігурації послідовного порту SBUF data 099h;адресація буфера послідовного порту IE data 0A8h;адресація регістра переривань IP data 0B8h; адресація регістра пріоритетів переривань PCON data 087h TCON data 088h;адреса регістра контролю переривань TMOD data 089h;настроювання таймерів TR1 bit TCON.6;побітова адресація регістрв TCON TF1 bit TCON.7 TL1 data 8Bh TH1 data 8Dh TI bit SCON.1 TB8 bit SCON.3

ORG 0 jmp start

start: mov IE,#010000000b mov IP,#000000000b mov SCON,#001000000b;налаштування передачі в режимі 1 mov TH1,#248 mov R0,#000111111b mov PCON,#00b mov TMOD,#000010000b;налаштування Timer1 в режим Auto-reload

mov A,#000000010b;--- mov DPTR,#0C000h; ----переключення мультиплексора на порт Х12 movx @DPTR,A;---

mov A,R0 setb TR1;запуск Timer1 mov SBUF,A;помістити вміст акумулятора в послідовний буфер loop: mov A,R0 mov A,#011b mov DPTR,#0A004h movx @DPTR,A mov A,R0 mov DPTR,#0A001h movx @DPTR,A inc A mov R0,A jbc TI,rec;перехід на мітку rec якщо TI=1 jmp loop

rec: clr TR1;зупинка роботи Timer1 mov A,R0;--- mov DPTR,#0A006h;----- виведення нової посилки на лінійку світлодіодів movx @DPTR,A;--- call ZAD mov A,#0h;--- mov DPTR,#0A006h;----- погашення світлодіодів movx @DPTR,A;--- call zad setb TR1;запуск роботи Timer1 mov A,R0 mov SBUF,A;відправлення нової посилки в SBUF jmp loop ZAD:;підпрограма затримки mov R1,#0FFh C2: mov R2,#0FFh C4: djnz R2, C4 djnz R1, C2 ret end

Програма роботи

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 455; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.115 (0.007 с.) |