Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Базовые логические элементы эмиттерно-связанной логикиСодержание книги

Поиск на нашем сайте

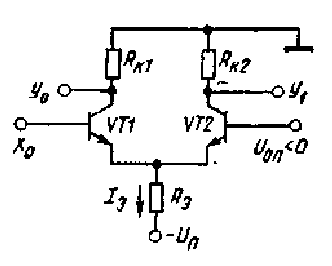

Причиной появления БЛЭ ЭСЛ явилось желание повысить быстродействие цифровых устройств. Это привело к использованию в них совершенно отличного от ТТЛ схемотехнического решения. Основными причинами инерционности биполярных ключей являются время рассасывания неосновных носителей из базовой области транзисторов и постоянная времени перезаряда выходной емкости. Если время рассасывания заряда неосновных носителей при работе транзистора в активном режиме может быть полностью исключено, то от влияния постоянной времени перезаряда выходной емкости полностью избавиться не удается. Это влияние можно лишь уменьшить путем увеличения коллекторного тока транзистора. При неизменном постоянном токе перезаряда выходной емкости транзистора, длительность его перехода из состояния лог.0 в состояние лог.1 и обратно может быть уменьшена только за счет уменьшения логического перепада. Такое решение позволяет увеличить быстродействие, но ухудшает помехоустойчивость, что накладывает дополнительные ограничения при создании схем, менее подверженных помехам. Основой БЛЭ ЭСЛ является токовый ключ, выполненный на двух транзисторах (рис. 8.14). На базу одного их них, например VT 2, подано некоторое постоянное опорное напряжение U оп. Изменение напряжения, подаваемого на вход х 0 ниже или выше U оп приводит к перераспределению постоянного тока I Э, заданного токостабилизирующим резистором R Э, между транзисторами VT 1 и VT 2. При этом транзисторы не попадают в режим насыщения и, следовательно, в ключе принципиально отсутствует интервал рассасывания их неосновных носителей. Таким образом, особенностью ЛЭ ЭСЛ является постоянство потребляемого тока независимо от значения выходного сигнала ключа.

Рис. 8.14 Принципиальная электрическая схема токового ключа ЭСЛ

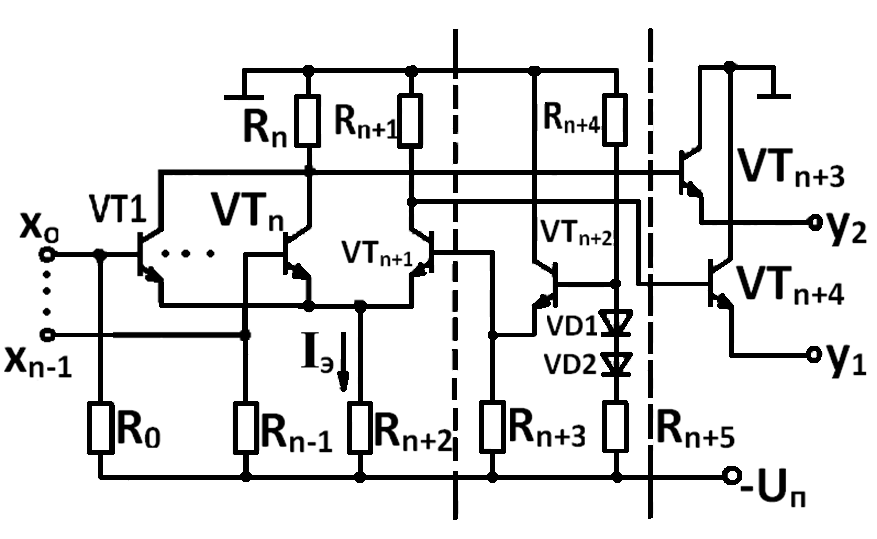

Эта особенность выгодно отличает ЛЭ ЭСЛ от ТТЛ, в которых в момент переключения ток, потребляемый элементом, резко возрастает, создавая внутренние помехи, ухудшающие помехозащищенность цифрового устройства. Нетрудно заметить, что общей шиной для элемента является шина + U п, в результате чего все потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме токового ключа так же, как и в схемах ТТЛ, реализован принцип положительной логики, при которой большему выходному напряжению соответствует сигнал лог.1, а меньшему – сигнал лог.0 (см. предыдущую лекцию). Быстродействие токового ключа весьма велико, так как, во-первых, транзисторы принципиально не заходят в область насыщения, и, во-вторых, мал логический перепад напряжений между значениями лог.0 и лог.1. последнее реализовано выбором малых сопротивлений R к1 и R к2 схемы, что крайне полезно с точки зрения уменьшения постоянной времени перезаряда выходной емкости транзистора. С токового ключа снимается одновременно два сигнала – прямой и инверсный, связанные с сигналом х 0 на входе схемы соотношениями: y 1 = x 0, y 0 = Можно отметить, что схемотехнически токовый ключ повторяет схему дифференциального усилителя постоянного тока (из лекции «Операционные усилители»). Выходное напряжение, снимаемое с выходов y 1 и y 0 всегда больше U оп, так как транзисторы VT 1 и VT 2 работают в ненасыщенном режиме. Поэтому непосредственное последовательное включение таких ключей невозможно. Для этого необходим согласующий каскад. В качестве такого согласующего каскада используют схемы эмиттерных повторителей, включенные между выходами токового ключа и выходом логического элемента. Полная схема БЛЭ, выполненного на ЭСЛ, приведена на рис. 8.15. Базовый элемент получен путем замены транзистора VT 1 токового ключа на группу параллельно включенных транзисторов VT 1 … VT n.

Рис. 8.15 Принципиальная электрическая схема БЛЭ ЭСЛ ИС серии 500

Функционально схему БЛЭ ЭСЛ можно разбить на три узла: - токовый ключ на транзисторах VT 1 … VT n+1 и резисторе R n+2; - источник эталонного напряжения, включающий параметрический стабилизатор на элементах R n+4, R n+5, VD 1, VD 2 и эмиттерный повторитель на VT n+2 и R n+3; - выходные эмиттерные повторители на транзисторах VT n+3 и VT n+4. Цепи нагрузок транзисторов VT n+3 и VT n+4 вынесены за пределы ИС, что снижает рассеиваемую на ней мощность и расширяет функциональные возможности БЛЭ. Диоды в задающей цепи источника эталонного напряжения служат для термокомпенсации опорного напряжения U оп. Принцип действия ЭСЛ.

Предположим, что все входы схемы (рис. 8.20) х 0, …, х n-1 подано напряжение, близкое к – U п. тогда транзисторы VT 1 … VT n будут заперты. Весь ток резистора R n+2 протекает через транзистор VT n+1, к выводу базы которого приложено опорное напряжение U оп. Этот транзистор поддерживается в активном режиме работы за счет действия глубокой последовательной отрицательной обратной связи по току. Если не учитывать обратные токи коллекторных переходов транзисторов VT 1 … VT n через резистор R n протекает только базовый ток транзистора VT n+3 выходного эмиттерного повторителя. Следовательно, напряжение на выходе близко к нулевому U у2 = - I Б VTn+3 R n – U БЭ VTn+3. (8.7) Численно это напряжение U у2 примерно равно -0,9 В. Через резистор R n+1 кроме базового тока транзистора VT n+4 протекает ток I К VTn+1, примерно равный I Э. эти токи создают на резисторе R n+1 падение напряжения, равное U Rn+1 = (I Kn+1 + I Бn+4) R n+1 = [(I Э h 21Э)/(h 21Э + 1) + I Бn+4] R n+1 ≈ I Э R n+1.

Это напряжение преобразуется выходным эмиттерным повторителем на транзисторе VT n+4 в выходное напряжение U у1, определяемое выражением U у1 ≈ - U БЭ VTn+4 - I Э R n+1. (8.8) Численно напряжение U у1 равно – 1,7 В. Если хотя бы на один из входов х 0, …, х n-1 подать напряжение, превышающее по уровню опорное U ОП (-1,3 В), соответствующий транзистор VT перейдет в активный режим работы. Его ток равен току эмиттера I Э, что приведет к смене уровней выходного напряжения U у2 = – U БЭ VTn+3 – I Э R n, U у1 ≈ - I Б VTn+4 R n+1 - U БЭ VTn+4. (8.9)

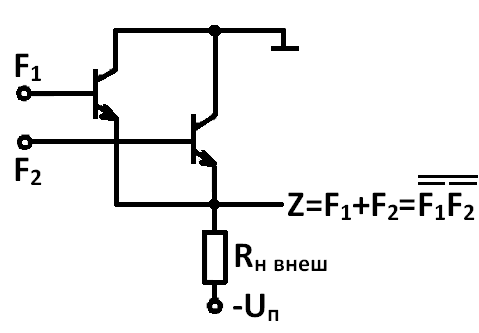

Из сказанного выше следует, что рассмотренная схема реализует по выходу у 2 операцию ИЛИ-НЕ, а по выходу у 1 – операцию ИЛИ. Резисторы R0 - Rn-1, включенные между базами транзисторов токового ключа и выводом – UП, обеспечивают запертое состояние этих транзисторов при отсутствии входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых входов ИС к выводам источника питания. Особенностью схемотехнического построения элементов ЭСЛ является использование для подключения общей шины собственно токового переключателя и выходных эмиттерных повторителей различных выводов ИС. Потребляемый ток, протекающий в этих цепях, имеет качественно различный характер. В принципе работы токового ключа заложено потребление принципиально постоянного тока, так как его работа связана с перераспределением эмиттерного тока резистора R Э (см. рис. 8.19). Эмиттерные же повторители потребляют импульсный ток. К тому же для улучшения частотных свойств сопротивление резисторов, подключаемых к выводам у1 и у2 ИС, подбираются весьма малыми (R ВНЕШ=75…100 Ом). поэтому совместное питание этих цепей из-за малой величины логического перепада может приводить к ложному срабатыванию соседних элементов, т.е. к появлению сбоев при обработке информации (внутренних помех). Разделение цепей питания позволяет устранить этот недостаток. Раздельное питание токовых ключей и выходных эмиттерных повторителей позволяет дополнительно решить задачу снижения мощности, рассеиваемой в реальной аппаратуре. Так как выходное напряжение лежит в диапазоне -0,9…-1,7 В, то для питания внешних резисторов может быть использовано напряжение, не превышающее 2 В. Такое решение при малых значениях сопротивления R ВНЕШ позволяет значительно уменьшить бесполезные потери мощности. Рассмотренные функциональные возможности БЛЭ ЭСЛ могут быть существенно расширены простыми схемотехническими приемами. Вот два из них: совместное включение выходов нескольких элементов на общую нагрузку; многоярусное включение переключателей тока. Первый прием использует свойство эмиттерных повторителей поддерживать высокий уровень выходного напряжения, если хотя бы один из параллельно соединенных транзисторов включен (находится в активном режиме, рис. 8.16).

Рис. 8.16. Совместное включение выходов нескольких ЛЭ ЭСЛ

Логические операции, реализуемые при объединении выходов пары двухвходовых элементов, работающих с переменными х 1, х 0, у 1, у 0, иллюстрируются в табл. 8.3.

|

||||

|

Последнее изменение этой страницы: 2021-04-13; просмотров: 267; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.141.192.174 (0.01 с.) |

.

.