Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Команды ветвления и передачи управления

Команды ветвления позволяют реализовывать условные операторы и операторы циклов. В микроконтроллерах семейства MCS-51 доступны следующие команды: q безусловный переход: LJMP, AJMP, SJMP q вызов и возврат из подпрограммы: LCALL, ACALL, RET, RETI q переход в зависимости от результата проверки содержимого аккумулятора: JZ, JNZ, CJNE, JMP q переход в зависимости от значения флага переноса С: JC, JNC q переход в зависимости от значения любого бита в битовом пространстве: JB, JNB, JBC Команды 16-разрядных безусловных переходов и вызовов подпрограмм позволяют осуществить переход в любую точку адресного пространства памяти программ объемом до 64 Кбайт. Примеры команд: LJMP Metka;Переход к команде, расположенной по адресу ;обозначенному меткой ‘Metka’ LCALL Podprogramma;Вызов подпрограммы по адресу, обозначенному меткой ;‘Podprogramma’ Команды 11-разрядных переходов и вызовов подпрограмм позволяют сократить объем программы, но при этом обеспечивают переходы только внутри сегмента программной памяти размером 2 Кбайт. Эти команды принципиально могут приводить к необнаруживаемым транслятором ошибкам, когда программный модуль размещается на двух соседних 2 Кбайтовых сегментах памяти. AJMP Metka;Переход к команде, расположенной по адресу ;обозначенному меткой ‘Metka’ ACALL Podprogramma;Вызов подпрограммы по адресу, ;обозначенному меткой ‘Podprogramma’ В системе команд микроконтроллеров семейства MCS-51 имеются команды условных и безусловных переходов относительно начального адреса следующей команды в пределах от (РС)-127 до (РС)+127. Примеры команд: SJMP Metka;Переход к команде, расположенной по адресу ;обозначенному меткой ‘Metka’ JB P3.5, TstNxtUsl;Если на выводе 6 порта P3 нулевой потенциал, ACALL Podprogramma;то вызвать подпрограмму, обозначенную меткой ;‘Podprogramma’ CJNE A, #5, TstNxtUsl;Если в аккумуляторе содержится число 5, ACALL Podprogramma;то вызвать подпрограмму, обозначенную меткой ;‘Podprogramma’ Команды условного перехода в зависимости от результата анализа содержимого аккумулятора или значения флага переноса C могут быть использованы для реализации проверки различных условий. При этом содержимое не изменяется, то есть если требуется произвести несколько проверок одной и той же переменной, то повторно заносить значение этой переменной в аккумулятор не нужно. Например:

MOV A, 34;Если в переменной, хранящейся в ячейке внутренней JNB ACC_7, TstEQ5;памяти с адресом 34, число меньше нуля, CALL Podprogramma;то вызвать подпрограмму, обозначенную меткой ;‘Podprogramma’ TstEQ5;----------------------------------------------------------------- CJNE A,#5,TstLT5;Если в переменной, хранящейся в ячейке внутренней ;памяти с адресом 34, занесено число 5, CALL Podpr5;то вызвать подпрограмму, обозначенную меткой ;‘Podpr5’ TstLT5;----------------------------------------------------------------- JNС TstGE5;Если в переменной, хранящейся в ячейке внутренней ;памяти с адресом 34, занесено число, меньшее 5, CALL PodprLT5;то вызвать подпрограмму, обозначенную меткой ;‘PodprLT5’ TstGE5;----------------------------------------------------------------- JC TstNxtUsl;Если в переменной, хранящейся в ячейке внутренней ;памяти с адресом 34 занесено число, большее или CALL PodprGE5;то вызвать подпрограмму, обозначенную меткой ;‘PodprGE5’ TstGT5;----------------------------------------------------------------- CJNE A,#6,$+3;Если в переменной, хранящейся в ячейке внутренней JC TstNxtUsl;памяти с адресом 34, занесено число, большее 5, CALL PodprGT5;то вызвать подпрограмму, обозначенную меткой ;‘PodprGT5’ ;------------------------------------------------------------------------ JNC TstNxtUsl;Если в переменной, хранящейся в ячейке внутренней ;памяти 34, занесено число, меньшее или равное 5, CALL PodprLE5;то вызвать подпрограмму, обозначенную меткой ;‘PodprLE5’ Косвенный переход JMP @A+DPTR в системе команд микроконтроллеров семейства MCS-51 обеспечивает ветвление программы по содержимому аккумулятора А. Это позволяет реализовывать операцию перехода по заданному коду, эквивалентную оператору case в языке программирования Pascal, но намного быстрее (за два машинных цикла). Использование в этой команде указателя данных DPTR позволяет размещать таблицу переходов в любом месте памяти программ. Пример реализации команды выбора варианта: BeginOpCase:;Начало команды выбора вариантов---------------------------- MOV DPTR, #JMP_TBL;Задать начальный адрес таблицы адресов переходов MOV A, 33;В ячейке с адресом 33 хранится переменная, по ;на обслуживающую программу

CLR C;Осуществить арифметический сдвиг аккумулятора RLC A;вправо (умножить на 2) т.к. команды переходов ;занимают два байта

JMP @A+DPTR;Перейти к выполнению заданного в ячейке 33 кода

;начало таблицы переходов по содержимому переменной в ячейке памяти 33--- JMP_TBL: JMP Case0;Перейти к выполнению кода по числу 0 JMP Case1;Перейти к выполнению кода по числу 1 JMP EndCase;Это число в ячейке 33 в список разрешенных не входит JMP EndCase;Это число в ячейке 33 в список разрешенных не входит JMP Case4;Перейти к выполнению кода по числу 4 EndCase:;---------------------------------------------------------------- Способы адресации операндов При определении способа адресации операндов в команде необходимо учитывать, что виды адресации для каждого операнда команды (источника или приемника) могут не совпадать. Неявная адресация. При неявной адресации регистр-источник или регистр-приемник подразумевается в самом коде операции. Например: 03 RR A;Сдвинуть содержимое аккумулятора вправо D4 DA A;Произвести десятичную коррекцию результата суммирования E8 MOV A, R0;В первом операнде использована неявная адресация, ;а во втором - регистровая Регистровая адресация используется для обращения к восьми рабочим регистрам выбранного банка рабочих регистров, а также для обращения к регистрам А, В, АВ (сдвоенному регистру), DPTR, и к флагу переноса С. Номер регистра записывается в трех младших битах команды. Например: F8 MOV R0, A;в первом операнде использована регистровая адресация, ;а во втором – неявная Прямая байтовая адресация используется для обращения к ячейкам внутренней памяти (ОЗУ) данных (адреса 0:127) и к регистрам специального назначения (адреса 128 … 256). Адрес ячейки памяти помещается во второй байт команды. Например: E520 MOV A, 20h;во втором операнде использована прямая байтовая ;адресация, а в первом – неявная 8D15 MOV 15h,R6;в первом операнде использована прямая байтовая ;адресация, а во втором – регистровая Прямая битовая адресация используется для обращения к отдельно адресуемым 128 битам, расположенным в ячейках с адресами 20Н-2FH, и к отдельно адресуемым битам регистров специального назначения. Например: D220 SETB 20h;использована прямая битовая адресация C215 CLR 15H;использована прямая битовая адресация Косвенно-регистровая адресация используется для обращения к ячейкам внутреннего ОЗУ данных. В качестве регистров-указателей используются регистры R0, R1 выбранного банка регистров. Например: E6 MOV A,@R0;В первом операнде использована неявная адресация, а во ;втором - косвенно-регистровая F7 MOV @R1,A;В первом операнде использована косвенно-регистровая ;адресация, а во втором - неявная Косвенно-регистровая адресация используется также для обращения к внешней памяти данных. В этом случае с помощью регистров- указателей R0 и R1 (рабочего банка рабочих регистров) выбирается ячейка из блока 256 байт внешней памяти данных. Номер блока предварительно задается содержимым порта Р2. E2 MOVX A,@R0;В первом операнде использована неявная адресация, а во ;втором - косвенно-регистровая F3 MOVX @R1,A;В первом операнде использована косвенно-регистровая ;адресация, а во втором - неявная Если в качестве регистра-указателя используется 16-разрядный указатель данных (DPTR), то можно выбрать любую ячейку внешней памяти данных объемом до 64 Кбайт. (В некоторых моделях микроконтроллеров семейства MSC-51 таким образом можно обращаться к внутренней памяти данных объемом более 256 байт).

E0 MOVX A,DPTR;В первом операнде использована неявная адресация, а во ;втором - косвенно-регистровая F0 MOVX DPTR,A;В первом операнде использована косвенно-регистровая ;адресация, а во втором - неявная Косвенно-регистровая адресация по сумме базового и индексного регистра (содержимое аккумулятора А) упрощает просмотр таблиц, записанных в памяти программ. Любой байт из таблицы может быть выбран по адресу, определяемому суммой содержимого DPTR или РС и содержимого А, например: 83 MOVC A,@A+PC;В первом операнде использована неявная адресация, а ;во втором - косвенно-регистровая 93 MOVC A,@A+DPTR;В первом операнде использована неявная адресация, а ;во втором - косвенно-регистровая Непосредственная адресация позволяет выбрать из адресного пространства памяти программ константы, явно указанные в команде, например: 7414 MOV A, #14h;В первом операнде использована неявная ;адресация, а во втором - непосредственная 902048 MOV DPTR, #2048h;В первом операнде использована неявная ;адресация, а во втором - непосредственная Полный список команд микроконтроллеров семейства MCS-51, упорядоченный по коду команды, приведен в приложении 1. Устройство параллельных портов микроконтроллеров MCS‑51 Порты ввода-выводаP0, P1, P2, P3 являются квазидвунаправленными и обеспечивают обмен информацией между микроконтроллером и внешними устройствами, образуя 32 линии ввода-вывода. Каждый из портов содержит 8-разрядный регистр, имеющий байтовую и битовую адресацию для установки (запись логической 1) или сброса (запись логического 0) разрядов этого регистра с помощью программного обеспечения микроконтроллера. Выходы этих регистров соединены с внешними выводами микросхемы. Все разряды параллельных портов устроены одинаково. Упрощенная схема одного разряда параллельного порта микроконтроллера показана на рис. 20.2. Отличаются только выводы порта P0, у которых отсутствуют внутренние генераторы тока в верхней части схемы. Один разряд регистра-защелки порта представляет собой D-триггер, запись входных данных в который происходит по высокому уровню синхросигнала. На рис. 20.2 этот сигналу назван «запись в защелку». Сигнал с инвертирующего выхода триггера умощняется при помощи МОП-транзистора и поступает на внешний вывод микросхемы.

Рис. 20.2. Упрощенная схема одного бита порта. Естественно, что внутреннее устройство порта намного сложнее приведенного на рис. 20.2. Упрощение сделано для облегчения понимания работы параллельных портов микроконтроллера. Желающие более подробно познакомиться с внутренним устройством параллельных портов микроконтроллера могут обратиться к техническому описанию конкретной микросхемы.

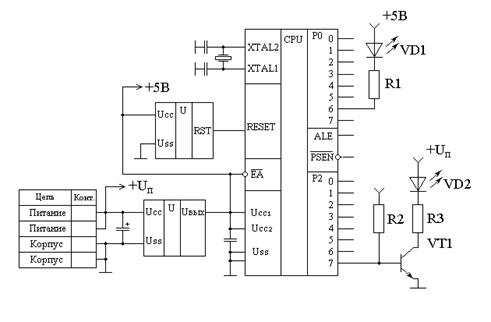

Внутренняя схема порта построена таким образом, чтобы максимально упростить подключение внешних устройств к микроконтроллеру. Например, умощняющий внешний транзистор может быть подключен непосредственно базой к выводу микроконтроллера без дополнительного токоограничивающего резистора, как показано на рис. 20.3. Это становится возможным благодаря внутреннему генератору тока.

Рис. 20.3. Схема подключения светодиодных индикаторов к параллельному порту. Значение сигнала непосредственно с внешнего вывода порта считывается по сигналу "чтение вывода". Однако при выполнении операций с отдельными битами требуется считывать содержимое внутреннего регистра-защелки порта. Если база биполярного транзистора непосредственно подключена к выводу порта, то считывание значения логической 1 с вывода порта становится невозможным. Дело в том, что напряжение на p-n-переходе база-эмиттер транзистора не может превысить ~0,7В (для кремниевого транзистора). Такое напряжение однозначно будет воспринято цифровой схемой как логический ноль, поэтому при выполнении операций над отдельными битами параллельного порта считывание производится непосредственно с выхода регистра-защелки порта. При этом выход Q D-триггера подключается к внутренней шине (считывается) по сигналу "чтение защелки". Чтение внешних выводов портаP3 осуществляется командами: MOV A, P3;Скопировать состояние выводов порта P3 в аккумулятор JB P3.4, Metka;Если на выводе 4 порта P3 логическая 1, то перейти на ;метку Metka

Чтение регистра-защелки осуществляется командами чтение-модификация-запись. Например: CPL P3.1;Проинвертировать сигнал на выводе 1 порта P3 ORL P2, #56h;Установить единичный сигнал на выводах 1,2,4 и 6 порта P2 ANL P3, #03h;Установить нулевой сигнал на выводах 0 и 1 порта P3 SETB P3.1;Установить высокий потенциал на выводе 1 порта P3 Порты микросхемы служат для управления внешними устройствами, подключенными к микроконтроллеру. Схема подключения простейших внешних устройств приведена на рис. 20.3. Он иллюстрирует особенности подключения светодиодных индикаторов к параллельным портам микроконтроллера MCS‑51. Присутствие в схеме порта выходного мощного транзистора позволяет подключать к выводам порта светодиодные индикаторы непосредственно, без усилителя мощности. Однако при этом необходимо следить за максимальной допустимой мощностью, рассеиваемой на микросхеме и отдельных выводах порта. Эквивалентная схема, на которой показан путь протекания выходного тока порта, приведена на рис. 20.4. Как видно из приведенной схемы именно выходной ток порта I0 используется для зажигания светодиода.

Рис. 20.4. Эквивалентная схема подключения светодиодного индикатора к параллельному порту.

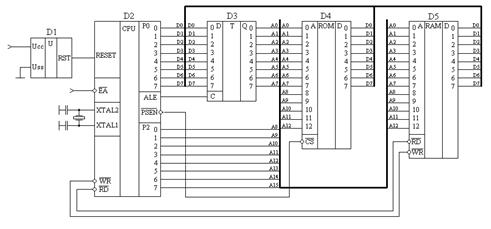

Для умощнения выводов порта можно применить транзисторный ключ, показанный также на рис. 20.3. Эта же схема используется при низковольтном питании микроконтроллера. Напряжения 3,3 В недостаточно для открывания p-n перехода светодиода. Обратите внимание, что база транзистора подключена непосредственно к выводу порта. Это стало возможным только благодаря использованию в схеме порта генератора тока в верхнем плече выходного каскада. Если выходного тока порта достаточно для открывания транзисторного ключа, то резистор R2 не используется. Этот резистор подключают для увеличения тока базы транзисторного ключа. На максимальное значение этого тока накладываются те же ограничения, что и для непосредственного подключения светодиодного индикатора к выводам порта. Резистор R3 рассчитывается исходя из допустимого тока через светодиод VD2. При возможности выбора напряжения питания для светодиодов лучше выбрать более высокое напряжение. Это позволит обеспечить более равномерное свечение светодиодов, так как разброс параметров светодиодов будет оказывать меньшее влияние на разброс токов, протекающих через них. Микроконтроллеры предназначены для управления внешними устройствами. Однако изменять напряжения на выводах параллельного порта микроконтроллера можно только при помощи программы, записанной в память программ. Какие напряжения необходимо подавать на выходы микросхемы, зависят от схемы подключения индикатора. В приведенной на рис. 20.3 схеме для зажигания светодиода VD1, в разряд 6 порта P0 необходимо записать логический 0. Для зажигания светодиода VD2 необходимо в разряд 7 порта P2 записать логическую единицу, а для его гашения – логический ноль. Чтобы изменять потенциалы на выводах микросхемы можно воспользоваться следующими командами с байтовой адресацией: ú MOV (пересылка), например: MOV P1, #01110011b;Выдать на все восемь выводов P1 число 011100112 MOV P3, A;Выдать на все восемь выводов P3 содержимое ACC ú ANL (логическое 'И'), например: ANL P1, #11110011b;выдать низкий потенциал на выводах P1.2 и P1.3 ú XRL (исключающее 'ИЛИ'), например: XRL P3, #01000100b;инвертировать состояние выводов P3.2 и P3.6 ú ORL (логическое 'ИЛИ'), например: ORL P1, #00001100b;выдать высокий потенциал на выводах P1.2 и P1.3 Эти команды изменяют потенциал сразу на нескольких выводах порта. Для изменения потенциалов только на одном выводе микросхемы, можно воспользоваться следующими командами с битовой адресацией: ú MOV (пересылка), например: MOV P1.2, C;выдать содержимое бита переноса через вывод 2 порта P2 ú CPL (инверсия), например: CPL P1.2;проинвертировать 2-й бит порта P2 ú SETB (установить бит), например: SETB P2.3;выдать высокий потенциал на вывод 3 порта P2 ú CLR (сбросить бит), например: CLR P2.3;выдать низкий потенциал на вывод 3 порта P2 При записи в разряд порта логического 0 выходной транзистор открывается, и на выводе микросхемы появляется низкий потенциал, изменить который извне невозможно. Поэтому при опросе этого вывода порта микросхемы входная информация в этом случае всегда будет восприниматься как логический 0 независимо от состояния выходов внешних устройств. Если в указанный разряд записать логическую 1, то выходной транзистор закрывается и на выводе микросхемы за счет генератора тока появляется высокий потенциал. Он может быть изменен извне на нулевой потенциал замыканием соответствующего вывода микросхемы на общий провод. В этом случае считываемое микроконтроллером значение бита будет соответствовать сигналу на выходе внешнего устройства. Поэтому, перед тем как осуществить ввод информации по какому-либо выводу порта, соответствующий разряд необходимо настроить на ввод — записать в него логическую единицу. По той же причине при настройке выводов порта на выполнение альтернативных функций в соответствующие разряды параллельного порта должны быть записаны логические 1. Кроме работы в качестве обычных портов ввода-вывода, внешние выводы портов Р0–Р3 могут выполнять ряд дополнительных (альтернативных) функций. Порт P0 может быть использован для организации части шины адреса и шины данных при работе микроконтроллера с внешней памятью данных или программ. При этом через него из микроконтроллера выводится младший байт адреса A0‑A7, а также принимается в микроконтроллер или выдается из него байт данных. Во время чтения содержимого внешней памяти во все триггеры-защелки порта P0 аппаратно записываются 1 (т.е. содержимое порта теряется). Кроме того, через порт P0 передаются данные при программировании внутреннего ППЗУ, и читается содержимое внутренней памяти программ при работе с программатором. При сбросе микросхемы во все разряды порта P0 записываются 1. У схемы P0, в отличие от схем всех других портов отсутствует внутренний генератор тока. Поэтому при работе с этим портом приходится подключать внешние резисторы к плюсу источника питания. Формат и адрес порта P0 приведены на рис. 20.5. На этом же рисунке приведены адреса отдельных битов порта P0 в битовом пространстве. На рис. 20.6 приведена схема использования выводов портов P0 и P2 для подключения внешней памяти программ и внешней памяти данных.

Рис. 20.5. Формат параллельного порта P0 Порт P1 может быть использован для чтения внутренней памяти программ или для передачи младшего байта адреса при программировании внутреннего РПЗУ. В младших моделях микроконтроллера семейства других альтернативных функций у порта P1 нет. При сбросе микросхемы во все разряды порта записываются 1.

Рис. 20.6. Использование выводов портов P0 и P2 для подключения внешней памяти программ и внешней памяти данных Формат и адрес порта P1 приведены на рис. 20.7. На этом же рисунке приведены адреса отдельных битов порта P1 в битовом пространстве. Заметим, что этот порт в самых младших моделях микроконтроллеров альтернативных функций не имеет, а приведенные альтернативные функции относятся к микроконтроллерам с ядром MCS‑52. Линии порта Р1 могут выполнять альтернативные функции только в том случае, если в соответствующие этим линиям разряды регистра записаны логические 1, иначе на линиях порта будет присутствовать логический 0 независимо от характера принимаемой или передаваемой информации.

P1.0 T2 — внешний вход таймера/счетчика 2 P1.1 T2EX — вход управления перезагрузки/захвата таймера Рис. 20.7. Формат параллельного порта P1 Порт P2 может быть использован для передачи старшего байта адреса при программировании внутреннего ППЗУ и при чтении внутренней памяти программ. Через порт Р2 выводится старший байт адреса А8 - А15 при работе с внешней памятью программ и внешней памятью данных (с 16- разрядным адресом). Во время доступа к внешней памяти содержимое регистра-защелки порта P2 не изменяется. При сбросе микросхемы во все разряды порта записываются 1. Формат и адрес порта P2 приведены на рис. 20.8. На рис. 20.6 приведена схема использования порта P2 при подключении внешней памяти программ и внешней памяти данных.

Рис. 20.8. Формат параллельного порта P2 Порт P3. Каждая линия порта Р3 имеет индивидуальную альтернативную функцию, которая может быть задействована простым обращением к устройству, соединенному с выводом порта. Например, для того чтобы был выработан строб WR, достаточно обратиться с внешней памяти командой MOVX @DPTR, A или MOVX @R0, A. Линии порта Р3 могут выполнять альтернативные функции только в том случае, если в соответствующие этим линиям разряды регистра записаны логические 1, иначе на линиях порта будет присутствовать логический 0 независимо от характера принимаемой или передаваемой информации. При сбросе микросхемы во все разряды порта записываются 1. Формат и адрес порта P3 приведены на рис. 20.9.

Р3.0RxD — вход последовательного порта; Р3.1TxD — выход последовательного порта; Р3.2INT0 — вход 0 внешнего запроса прерываний; Р3.3INT1 — вход 1 внешнего запроса прерываний; Р3.4Т0 — вход счетчика внешних событий 0; Р3.5Т1 — вход счетчика внешних событий 1; Р3.6WR — строб записи во внешнюю память данных; Р3.7RD — строб чтения из внешней памяти данных. Рис. 20.9. Формат параллельного порта P3

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 320; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.143.0.157 (0.084 с.) |