Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Архитектура микроконтроллеров MCS-51

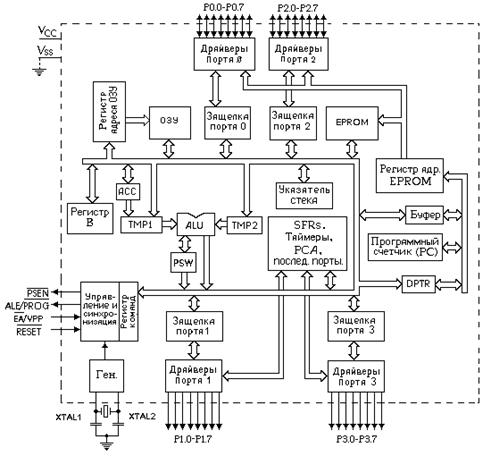

Архитектура семейства MCS-51в значительной мере предопределяет ее назначение — это построение компактных и дешевых цифровых устройств. Все функции микроконтроллера реализуются с помощью единственной микросхемы. В состав семейства MCS-51 входит ряд микросхем от самых простых микроконтроллеров до достаточно сложных. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать простейшие алгоритмы цифровой обработки сигналов. Все микросхемы этого семейства работают с одной и той же системой команд. Большинство микросхем выполняется в одинаковых корпусах с совпадающей цоколевкой(схемой расположения выводов). Это позволяет использовать для разработанного устройства микросхемы разных фирм-производителей (таких как Intel, Dallas, Atmel, Philips и т.д.) без переделки принципиальной схемы устройства и программы. Структурная схема микроконтроллера представлена на рис. 20.1 и состоит из следующих основных функциональных узлов: q блока управления; q арифметико-логического блока; q блока таймеров/счетчиков; q блока последовательного интерфейса и прерываний; q программного счетчика, памяти данных и памяти программ. Двусторонний обмен данными между элементами внутренней структуры микроконтроллера осуществляется с помощью внутренней 8-разрядной шины данных.

Рис. 20.1. Структурная схема микроконтроллера К1830ВЕ751 По такой схеме построены практически все представители семейства MCS‑51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд длиной 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одной микросхемы на другую. Рассмотрим подробнее назначение каждого блока. Блок управления и синхронизации предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков микроконтроллера во всех допустимых режимах его работы. В состав блока управления входят: q устройство формирования временных интервалов; q логика ввода-вывода;

q регистр команд; q регистр управления потреблением электроэнергии; q дешифратор команд, логика управления микроконтроллером. Устройство формирования временных интервалов предназначено для формирования и выдачи внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды микроконтроллера выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Обозначим частоту задающего генератора через Fг. Тогда длительность машинного цикла равна 12 / Fг или составляет 12 периодов сигнала задающего генератора. Логика ввода-вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода-вывода Р0–Р3. Регистр команд предназначен для записи и хранения 8-разрядного кода операции выполняемой команды. С помощью дешифратора команд и логики управления микроконтроллера он преобразуется в микропрограмму выполнения заданной команды. Регистр управления потреблением (PCON) позволяет останавливать микроконтроллер для уменьшения потребления электроэнергии и уменьшения уровня помех. Еще большего уменьшения потребления электроэнергии и уменьшения помех можно добиться, остановив задающий генератор микроконтроллера при помощи переключения битов регистра управления потреблением PCON. В вариантах микросхемы, изготовленных по технологии n-МОП (серия 1816 или иностранных микросхем, в названии которых в середине отсутствует буква 'c'), регистр управления потреблением PCON содержит только один бит, управляющий скоростью передачи последовательного порта SMOD, а биты управления потреблением электроэнергии отсутствуют. Арифметико-логический блок (АЛБ)представляет собой параллельное 8-разрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛБ состоит из: q регистров временного хранения TMP1 и TMP2; q ПЗУ констант; q арифметико-логического устройства; q дополнительного регистра (регистра В); q аккумулятора (ACC); q регистра состояния программ (PSW).

Регистры временного хранения – это восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Регистры временного хранения программно не доступны, ими управляет только микропрограмма выполнения команд. ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных или кода маски при битовых операциях и констант. Арифметико-логическое устройство представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций «И», «ИЛИ», суммирования по модулю два и инвертирования. Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный регистр внутренней памяти микроконтроллера. Аккумулятор- восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига Блок последовательного интерфейса и прерываний предназначен для организации последовательного ввода-вывода информации и организации прерываний выполнения программы. В состав этого блока входят: q логика управления; q регистр управления; q буфер передатчика; q буфер приемника; q приемопередатчик последовательного порта; q регистр приоритетов прерываний; q регистр разрешения прерываний; q логика обработки флагов прерываний.

Счетчик команд предназначен для формирования текущего 16-разрядного адреса внутренней или внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер счетчика команд, регистр счетчика команд и схема инкремента (увеличения содержимого на 1). Память данных предназначена для временного хранения информации, используемой в процессе выполнения программы. Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода-вывода и предназначены для обеспечения обмена информацией между микроконтроллером и внешними устройствами, образуя 32 линии ввода- вывода. Регистр состояния программы (PSW) предназначен для хранения информации о состоянии АЛУ при выполнении программы. Память программ предназначена для хранения программного кода и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ. Регистр указателя данных(DPTR) предназначен для формирования 16-разрядного адреса внешней памяти данных или памяти программ при считывании таблиц констант. Указатель стека (SP) представляет собой 8-разрядный регистр, предназначенный для организации особой области памяти данных (стека), в которой хранятся адреса возврата из подпрограмм, переменные и содержимое внутренних регистров микроконтроллера (в том числе регистры PSW и аккумулятор). Система команд микроконтроллеров MCS‑51 Ни один из видов микропроцессоров не может рассматриваться отдельно от системы команд. Не является исключением и семейство микроконтроллеров MCS‑51. Система команд микроконтроллеров этого семейства предоставляет большие возможности обработки данных, обеспечивает реализацию логических, арифметических операций, а также управление устройствами в режиме реального времени.

В этой системе командреализована побитная, потетрадная (4 бита), побайтовая (8 бит) и 16-разрядная обработка данных. Микросхемы семейства MCS-51 — это 8-разрядные микропроцессоры, а это означает, что ПЗУ, ОЗУ, регистры специального назначения, АЛУ и внешние шины имеют байтовую организацию. Двухбайтовые данные используются только регистром-указателем(DTPR) и счетчиком команд (PC). В машинном коде команда занимает один, два или три байта в зависимости от типа адресации. Команды выполняются за один, два или четыре (умножение и деление) машинных цикла. Запись команд в машинных кодах для человека неудобна. Кроме того, машинные команды, отличающиеся младшими битами или вторым байтом выполняют одинаковые действия над разными ячейками памяти. Поэтому для записи команд микропроцессоров была придумана система мнемонических обозначений. В записи команды микропроцессора сначала ставится мнемоническое обозначение кода операции, затем указывается ячейка памяти – приемник результата выполнения операции и, наконец, источник данных для выполнения операции. Например, в команде E535 MOV A, 35h символы MOV обозначают операцию копирования, второй операнд 35 определяет, что данные необходимо взять из ячейки памяти с шетнадцатеричным адресом 35, а первый операнд A определяет, что результат необходимо поместить в регистр-аккумулятор. При этом старое значение регистра-аккумулятора будет стерто. Слева приведена машинная команда микроконтроллера в шестнадцатеричной записи, соответствующая находящейся справа мнемонической записи команды. Мнемоническое обозначение кода операцииотделяется от операндов одним или несколькими символами пробела или табуляции, а операнды отделяются друг от друга запятыми. При этом между операндами допустимо использование символов пробела или табуляции, которые могут потребоваться для более наглядной записи команды. Если операция требует для выполнения двух источников и одного приемника результата операции (например, команда сложения ADD или вычитания SUBB), то первый операнд является одновременно и источником и приемником результата операции. Например, в команде 2535 ADD A, 35h символы ADD обозначают операцию сложения двух чисел, данные будут взяты из ячейки памяти с шестнадцатеричным адресом 35 и аккумулятора, а результат будет помещен в аккумулятор вместо старого значения этого регистра.

В табл. 20.1 приведены мнемонические обозначения машинных команд, влияющих на значения флагов регистра слова состояния программы PSW, а в табл. 20.2 приведены обозначения и символы, используемые при описании команд микроконтроллеров семейства MCS-51. Команды микроконтроллера условно можно разбить на пять групп: q арифметические команды; q логические команды с байтовыми переменными; q команды передачи данных; q команды битового процессора; q команды ветвления программ и передачи управления ОЭВМ. Арифметические команды В наборе команд микроконтроллера имеются следующие арифметические операции: q сложение — ADD; q сложение с учетом флага переноса — ADDC; q вычитание с заемом из флага переноса — SUBB; q инкрементирование (увеличение на 1) — INC; q декрементирование (уменьшение на 1) — DEC; q десятичная коррекция — DA; q умножение — MUL; q деление — DIV. Действия производятся над целыми беззнаковыми восьмиразрядными числами. Арифметические операции в рассматриваемой системе команд могут быть выполнены только над содержимым регистра-аккумулятора. При операции умножения содержимое аккумулятора A умножается на содержимое регистра B, и результат размещается следующим образом: младший байт в регистре B, старший — в регистре А. В случае выполнения операции деления целое от деления помещается в аккумулятор A, остаток — в регистр В.

|

||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 540; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.135.200.211 (0.016 с.) |