Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Арифметико-логические устройства

Арифметико-логическое устройство (АЛУ) (англ. arithmetic logic unit, ALU) — узел процессора, который под управлением устройства управления (УУ) служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова. Операции в АЛУ Все выполняемые в АЛУ операции являются логическими операциями (функциями), которые можно разделить на следующие группы: операции двоичной арифметики для чисел с фиксированной точкой; операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой; операции десятичной арифметики; операции индексной арифметики (при модификации адресов команд); операции специальной арифметики; операции над логическими кодами (логические операции); операции над алфавитно-цифровыми полями. Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами. К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»). Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство. Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами). Обширна группа операций редактирования алфавитно-цифровой информации. Каждая операция в АЛУ является логической функцией или последовательностью логических функций описываемых двоичной логикой для двоичных ЭВМ, троичной логикой для троичных ЭВМ, четверичной логикой для четверичных ЭВМ, десятичной логикой для десятичных ЭВМ и т. д.

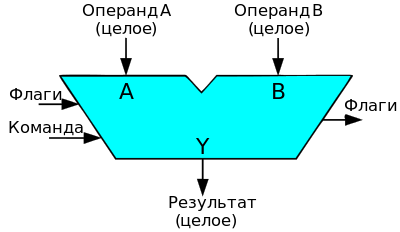

Обобщённая блок-схема арифметико-логического устройства (АЛУ)

Обобщённая блок-схема арифметико-логического устройства (АЛУ) приведена на ритсунке 48. Стрелками указаны входные и выходные слова. Флаги — признаки (например, результата сравнения операндов) выполнения предыдущей операции (вход) и результата выполнения текущей операции (выход). В одноместных операциях таких, например, как инверсия битов слова или битовый сдвиг второй операнд (B) не участвует в операции. Слово команды указывает необходимую операцию.

Рис. 48. Обобщённая блок-схема арифметико-логического устройства (АЛУ).

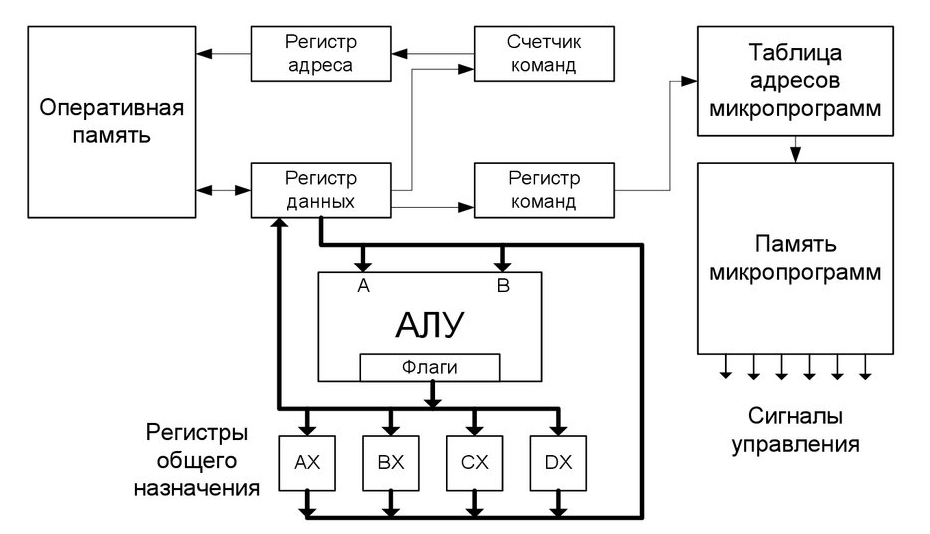

Классификация АЛУ По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ (они иногда называются микропрограммируемыми) операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами в процессе выполнения т. н. микропрограмм. При этом, каждой команде соответствует своя микропрограмма. На рисунке 49 представлена структура микропроцессорной системы с АЛУ последовательного типа. Главной особенностью структуры является наличие памяти микропрограмм (их нужно отличать от программ, выполняемых ЭВМ (микропроцессором или микроконтроллером), находящихся в ОЗУ!). Память микропрограмм содержит набор микропрограмм, каждая из которых управляет АЛУ и устройством управления микропроцессора для выполнения одной из команд, находящейся в регистре команд в настоящий момент времени.

Рис. 49. Структура микропроцессорной системы с микропрограммным управлением работой АЛУ.

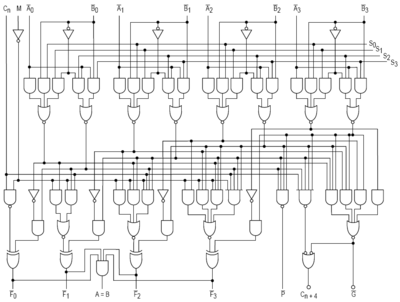

В параллельных АЛУ. Такие АЛУ также называются схемно-реализованными в виде сложных комбинационных логических схем. При этом каждой команде соответствует своя комбинационная схема.) операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов. Параллельные АЛУ по вполне понятным причинам быстрее последовательных, но гораздо сложнее и более энергозатратны. На рисунке 50 приведён пример схемно - реализованного АЛУ.

Рис. 50. Комбинационная логическая схема 4-битного АЛУ, реализованная в 24-выводной микросхеме ТТЛ, модель 74181, впервые разработанная и ранее изготавливаемая фирмой Texas Instruments. Выполняет сложение, вычитание, все элементарные логические функции и битовые сдвиги над двумя 4-битовыми операндами. Как и любая комбинационная схема не содержит в своем составе регистров.

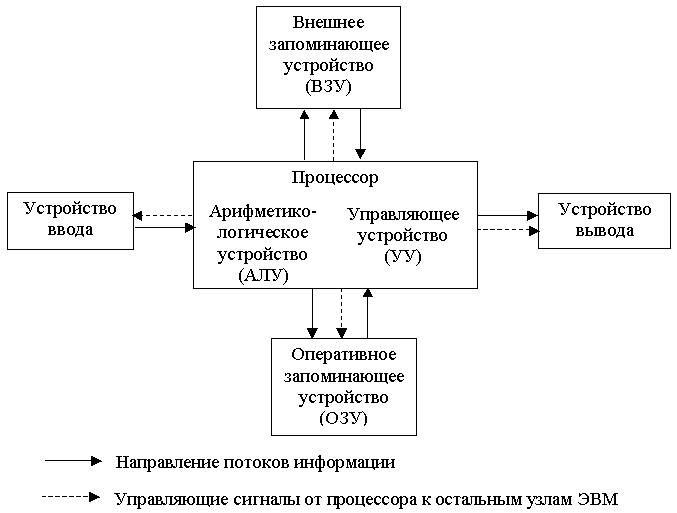

По способу представления чисел различают АЛУ: для чисел с фиксированной точкой; для чисел с плавающей точкой; для десятичных чисел. По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы. По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметико-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами. АЛУ в микропроцессорной системе занимает важное место, поскольку от его возможностей по выполнению набора команд микропроцессора и производительности зависит эффективность работы микропроцессорной системы. На рисунке 51 представлена структурная схема ЭВМ с архитектурой фон-Неймана, который первым чётко определил состав узлов ЭВМ и место в ней АЛУ. .

Рис. 51. Структура микропроцессорной системы (ЭВМ или микроконтроллера).

|

||||||

|

Последнее изменение этой страницы: 2021-07-18; просмотров: 134; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.220.126.5 (0.009 с.) |