Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Лекция 10. Логические и цифровые устройства. 4 часа.Стр 1 из 9Следующая ⇒

ЛЕКЦИЯ 10. ЛОГИЧЕСКИЕ И ЦИФРОВЫЕ УСТРОЙСТВА. 4 часа.

Логические вентили. Схемы инвертора, И, ИЛИ, ИЛИ-НЕ, И-НЕ на основе биполярных и МОП-транзисторов. Таблицы истинности. Сложные (комбинационные) схемы. Шифраторы. Дешифраторы. Двоичные коды. Двоичная арифметика. Простейший сумматор. Логические устройства последовательностного действия. Триггерный эффект. Триггер. Состояния триггера. Счётный триггер и триггер - защёлка (D-триггер). Регистры и двоичные счётчики. Микропроцессор и микропроцессорная система. Анализ функционирования логических схем Аналоговые, дискретные и цифровые сигналы

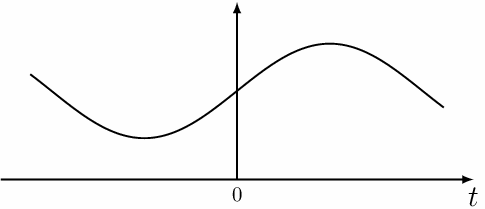

Любая физическая величина по характеру изменения ее значения может быть постоянной (если она имеет только одно фиксированное значение), дискретной (если она может иметь два или более фиксированных значений), или аналоговой (если она может иметь бесчисленное множество значений). Все эти величины могут быть преобразованы в цифровую форму. Аналоговые сигналы Аналоговым называется такой сигнал, который может быть представлен непрерывной линией из множества значений, определенных в каждый момент времени относительно временной оси. Значения аналогового сигнала произвольны в каждый момент времени, поэтому он может быть в принципе представлен как некая непрерывная функция (зависящая от времени как от переменной) либо как кусочно-непрерывная функция времени. Аналоговым сигналом можно назвать, например, звуковой сигнал, генерируемый обмоткой электромагнитного микрофона или ламповым акустическим усилителем, поскольку такой сигнал непрерывен и его значения (напряжение или ток) сильно отличаются друг от друга в каждый момент времени. На рисунке 1. изображен пример подобного рода аналогового сигнала.

Рис. 1. Аналоговый сигнал

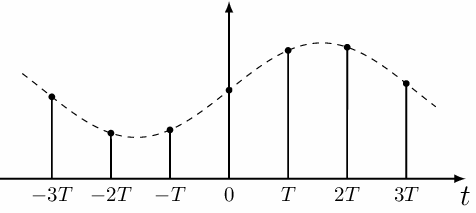

Аналоговые величины могу иметь бесконечное множество значений в определенных пределах. Они непрерывны и их значения не могут изменяться скачками. Дискретные сигналы Если некий сигнал принимает произвольные значения лишь в отдельные моменты времени, то такой сигнал называют дискретным. Чаще всего на практике применяются дискретные сигналы, распределенные по равномерной временной решетке, шаг которой называется интервалом дискретизации.

Дискретный сигнал принимает определенные не нулевые значения лишь в моменты дискретизации, то есть он является не непрерывным в отличие от аналогового сигнала. Если из звукового сигнала вырезать небольшие кусочки определенного размера через равные интервалы, такой сигнал можно будет назвать дискретным. Ниже приведен пример формирования подобного дискретного сигнала с интервалом дискретизации Т. Обратите внимание, что квантуется лишь интервал дискретизации, но не сами значения сигнала.

Рис. 2. К пояснению процесса формирования дискретного сигнала

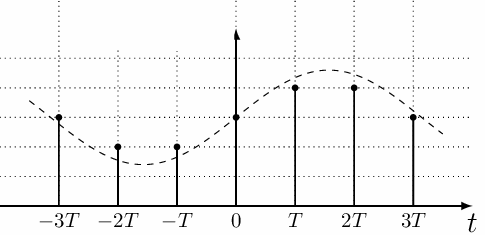

Дискретные сигналы имеют два и более фиксированных значений (количество их значений всегда выражается целыми числами). Пример простого дискретного сигнала на два значения: срабатывание путевого выключателя (переключение контактов выключателя в определенном положении механизма). Сигнал с путевого выключателя может быть получен только в двух вариантах - контакт разомкнут (нет действия, нет напряжения) и контакт замкнут (есть действие, есть напряжение). Цифровые сигналы Когда дискретный сигнал принимает только какие-то фиксированные значения (которые могут быть расположены по сетке с определенным шагом), такие что они могут быть представлены как количество квантовых величин, такой дискретный сигнал называется цифровым. То есть цифровой сигнал — это такой дискретный сигнал, который квантован не только по промежуткам времени, но и по уровню. Практически дискретные и цифровые сигналы в ряде задач отождествляются, и могут быть легко заданы в форме отсчетов с помощью вычислительного устройства. На рисунке 3 приведен пример формирования цифрового сигнала на базе аналогового. Обратите внимание, что значения цифрового сигнала не могут принимать промежуточных значений, а только определенные — целое количество вертикальных шагов сетки

.

Рис.3. Формирование дискретного сигнала

Цифровой сигнал легко записывается и перезаписывается в память вычислительных устройств, просто считывается и копируется без потери точности, тогда как перезапись аналогового сигнала всегда сопряжена с утратой некоторой, пусть и незначительной, части информации.

Обработка цифровых сигналов позволяет получать устройства с очень высокими характеристиками благодаря выполнению вычислительных операций совершенно без потерь качества, либо с пренебрежимо малыми потерями. В силу этих достоинств, именно цифровые сигналы повсеместно распространены сегодня в системах хранения и обработки данных. Вся современная память — цифровая. Аналоговые носители информации (такие как пленочные кассеты и т.д.) давно ушли в прошлое.

Рис. 4. Аналоговый и цифровой приборы для измерения напряжения:

Но даже у цифровых сигналов есть свои недостатки. Их невозможно передать напрямую как есть, ибо передача обычно реализуется посредством непрерывных электромагнитных волн. Поэтому при передаче и приеме цифровых сигналов необходимо прибегать к аналого-цифровому преобразованию. Меньший динамический диапазон цифровых сигналов (отношение наибольшего значения к наименьшему), обусловленный квантованностью значений по сетке, является еще одним их недостатком. Существуют и такие области, где аналоговые сигналы незаменимы. Например, аналоговый звук никогда не сравнится с цифровым, поэтому ламповые усилители и пластинки до сих пор не выходят из моды, несмотря на обилие цифровых форматов записи звука с самой высокой частотой дискретизации. Логические элементы Ключ замкнут

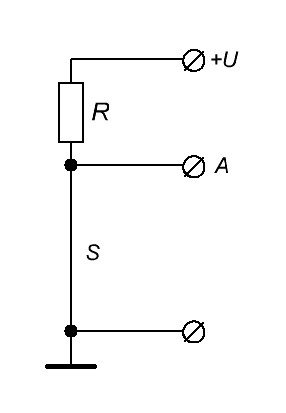

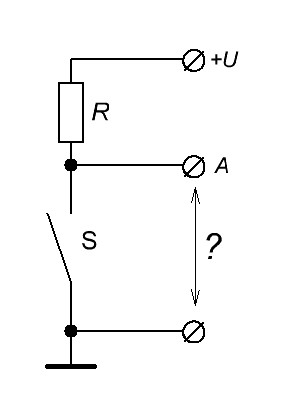

Рис. 9. Замкнутое состояние ключа.

Так как ключ у нас замкнут, следовательно, в идеале его сопротивление 0 Ом.. Значит, напряжение между землей и клеммой “А” будет 0 Вольт. 2) Ключ разомкнут

Рис. 10. Разомкнутое состояние ключа.

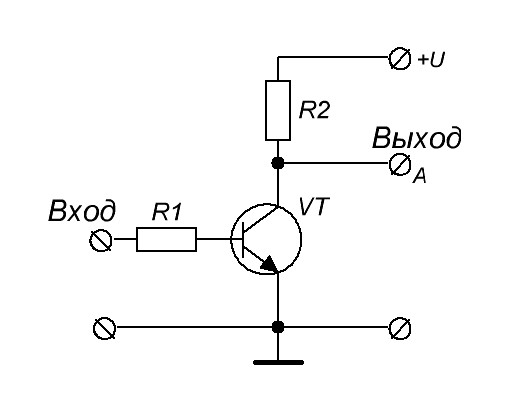

Падение напряжения на резисторе R будет равняться нулю, поэтому, на клемме “А” будет напряжение +U. Если в качестве ключа использовать транзистор, работающий в режимах насыщения и отсечки, мы получим реализацию функции инвертирования, т. к. при поступлении на вход высокого потенциала, соответствующего логической единице, на выходе появится практически нулевое напряжения, соответствующее логическому нулю.

Рис. 11. Схема инвертора на основе транзисторного ключа.

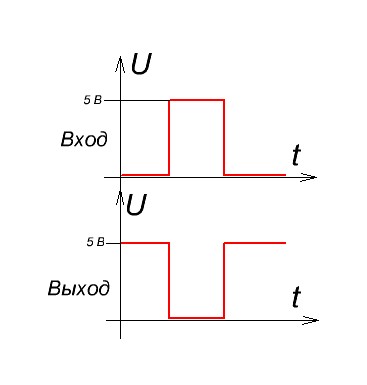

Работу инвертора в импульсном режиме поясняет рисунок 12:

Рис. 12. Работа инвертора в импульсном режиме.

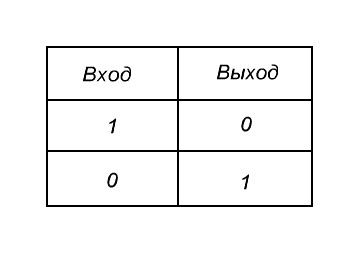

В информатике и логике есть такое понятие, как таблица истинности, которая показывает значение выходов каких-либо логических элементов со всеми возможными комбинациями на Входе. Для инвертора таблица истинности имеет вид:

Рис. 13. Таблица истинности инвертора.

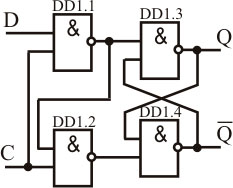

Примеры реализации логических элементов в цифровой схемотехнике. D-триггер Немного изменив схему синхронного RS-триггера, можно получить D-триггер. (D-delay, задержка). У него только один информационный вход D. Если на этот вход подать «1», а затем подать импульс на вход C, то на выходе Q будет «1», если на вход подать «0», затем импульс на C, то на выходе Q будет «0». Таким образом, D-триггер осуществляет фиксацию информации, поступающей на вход. Иногда такой триггер называют триггер - защёлку, т.к. он как бы защёлкивает состояние на входе D в момент прихода импульсов на вход С, и не реагирует на изменение состояния входа D в промежутках между этими импульсами (рисунок

Рис. 34. Схема D - триггера на основе 2И-НЕ элементов.

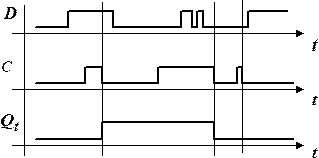

На рисунке 35 приведена временная диаграмма работы D -триггера.

Рис. 35. Временные диаграммы работы D- триггера.

Если вход D соединить с выходом НЕ_Q, то триггер будет менять свое состояние при каждом изменении состояния входа С от «0» к «1». При изменении от «1» к «0» состояние триггера меняться не будет. Таким образом, частота выходных импульсов будет вдвое меньше частоты входных импульсов. Такой триггер называется счетным или T-триггером. Делитель частоты используется очень широко в цифровой технике.

Рис. 36. Работа Т-триггера.

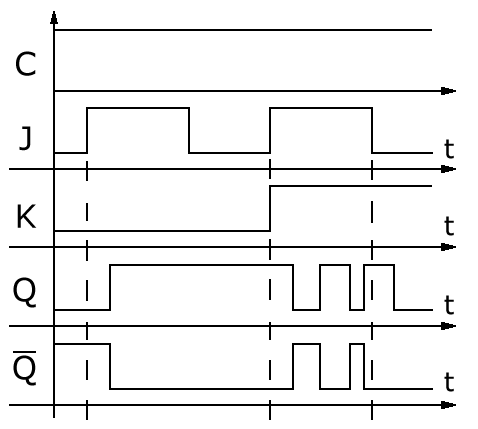

Существует разновидность синхронного RS-триггера, не имеющая запрещенной комбинации – JK-триггер. Он имеет три входа: J (вместо R), K (вместо S), и C. Если на оба информационных входа подана «1», то JK-триггер работает как счетный T-триггер с входом C.

Рис. 37. Работа JK - триггера.

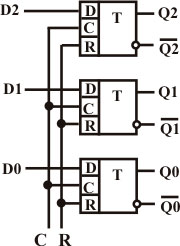

Регистр хранения На триггерах можно строить более сложные цифровые устройства, например, такие, как регистры. Регистры предназначены для хранения многобитовой информации, то есть чисел, записанных в двоичном коде. Рассмотри трех битовый регистр хранения на D-триггерах:

Рис. 38. Регистр хранения (или памяти).

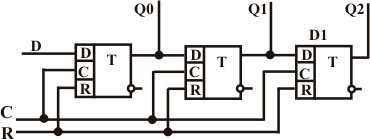

Каждый триггер может хранить один разряд (бит) числа. Вход R служит для установки выходов всех триггеров в нулевое (исходное) состояние перед записью числа, которое подается на входы D0,D1 и D2. При подаче импульса на вход C производится запись информации с этих входов. Информация может храниться сколь угодно долго, пока на вход С не подаются импульсы и подается питание. Регистр сдвига Другой разновидностью регистров является регистр сдвига. Он предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. На следующем рисунке приведена схема простейшего регистра сдвига информации вправо (по схеме):

Рис. 39. Регистр сдвига

В отличие от регистра хранения выход предыдущего триггера соединен с входом последующего. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд.

Сдвиговые регистры используются во многих схемотехнических решениях при построении цифровых устройств, прежде всего для преобразования последовательного кода в параллельный, а также для выполнения арифметических операций (умножения и деления на 2)с двоичными числами, организации линий задержки, формирования импульсов заданной длительности, генерирования псевдослучайных последовательностей (кодов) и т.п.

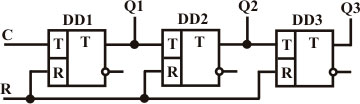

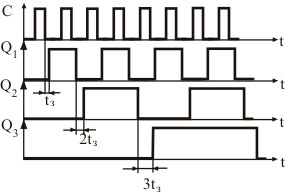

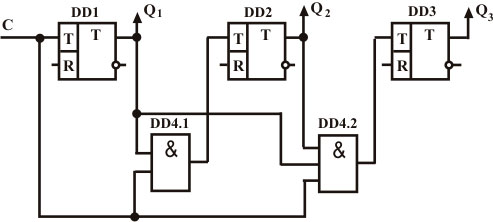

Счетчик Еще один класс цифровых устройств, которые можно построить на триггерах – счетчики. Как следует из названия, они осуществляют счет входных импульсов в заданном коде и могут хранить результат. Простейший счетчик с последовательным переносом можно получить с помощью счетных T-триггеров:

Рис. 40. Счётчик с последовательным переносом.

Рис. 41. Временные диаграммы работы счётчика

Подачей импульса на вход R счетчик приводится в исходное состояние, когда на выходах Q1-Q3 – уровень логического нуля. На вход C подаются импульсы для счета. С приходом заднего фронта первого импульса первый (левый) по схеме триггер устанавливается в «1». Если читать код справа налево, то он соответствует единице. Для нашего трехразрядного счетчика это код 001. С приходом второго импульса в «1» переключается второй триггер, а первый переключается в «0». Таким образом, код на выходах счетчика будет 010, что соответствует десятичной цифре 2. Следующий импульс установит код 011, то есть 3. Трехразрядный счетчик может досчитать до кода 111, что соответствует десятичной цифре 7. При этом наступает так называемое переполнение счетчика, и с приходом следующего импульса счетчик обнулится. Поскольку триггеры счетчика соединены последовательно, то и переключаться они будут также последовательно. Этот процесс отображен на графике, из которого видно, что время задержки переключения tз будет удваиваться и утраиваться. С увеличением числа разрядов задержка может оказаться неприемлемой, что является недостатком счетчиков с последовательным переносом. Для повышения быстродействия применяются счетчики с параллельным переносом, что достигается одновременной подачей входных импульсов на входы всех триггеров счетчика. Это реализуется с помощью введения в схему логических элементов И:

Рис. 42. Счётчик с параллельным переносом.

Рис. 43. Работа счётчика с параллельным переносом

Из схемы видно, что на вход второго триггера счетный импульс поступит только тогда, когда на выходе первого триггера будет «1», а на третий – когда «1» будет на выходах и первого, и второго триггеров. Очевидно, что с увеличением числа разрядов необходимо увеличивать как число логических элементов И, так и число их входов, что, в свою очередь, является недостатком такого типа счетчиков.

Регистры и счетчики, в свою очередь, могут применяться для построения более сложных цифровых устройств: сумматоров, ОЗУ и ПЗУ (оперативных и постоянных запоминающих устройств), АЛУ (арифметическо-логических устройств), входящих в состав процессоров, и так далее, к все более сложным цифровым устройствам.

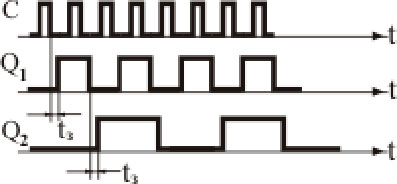

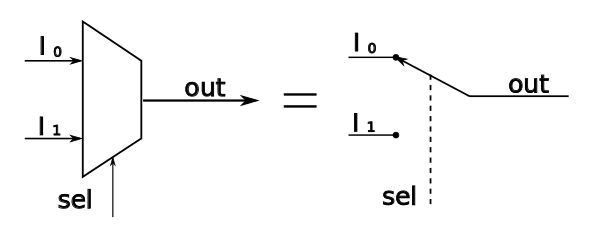

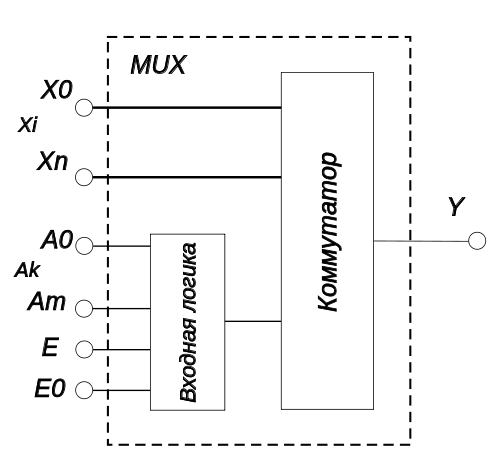

Мультиплексор Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из нескольких входов на один выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Рис. 44. Схема мультиплексора 2-к-1.

Аналоговые и цифровые мультиплексоры значительно различаются по принципу работы. Первые электрически соединяют выбранный вход с выходом (при этом сопротивление между ними невелико — порядка сотен или десятков ом). Вторые же не образуют прямого электрического соединения между выбранным входом и выходом, а лишь «копируют» на выход логический уровень ('0' или '1') с выбранного входа. Аналоговые мультиплексоры иногда называют ключами или коммутаторами. Устройство, противоположное мультиплексору по своей функции, называется демультиплексором. В случае применения аналоговых мультиплексоров (с применением ключей на полевых транзисторах) не существует различия между мультиплексором и демультиплексором; такие устройства могут называться коммутаторами. Устройство Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Коммутатор обслуживает управляющая схема, в которой имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов и числом адресных входов действует соотношение, то такой мультиплексор называют полным. Если, то мультиплексор называют неполным. Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, то есть могут блокировать действие всего устройства. В качестве управляющей схемы обычно используется дешифратор. В цифровых мультиплексорах логические элементы коммутатора и дешифратора обычно объединяются. Обобщённая схема мультиплексора

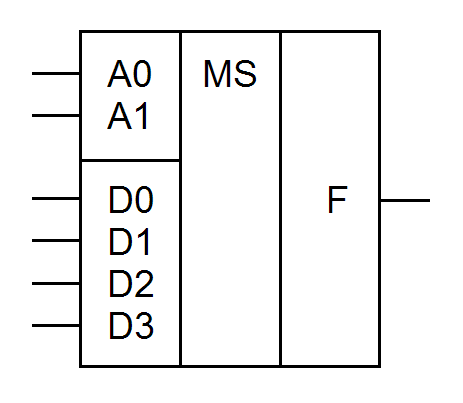

Рис. 45. Обобщённая схема мультиплексора.

Входные логические сигналы Xi поступают на входы внутреннего коммутатора и через коммутатор передаются на выход Y. На вход управляющей схемы подаётся слово адресных сигналов Ak (от англ. Address). Мультиплексор также может иметь дополнительный управляющий вход E (от англ. Enable), иногда этот вход обозначают на схемах CS (от англ. Chip Select — «выбор микросхемы»), который разрешает или запрещает прохождение входного сигнала на выход Y. Логический уровень разрешающего сигнала в разных конкретных моделях мультиплексоров может быть как логическая 1, так и логический 0, но в подавляющем количестве типов мультиплексоров выпускаемых промышленностью разрешающий сигнал логический 0. В разных типах мультиплексоров при запрещающем состоянии передачи на входе E на выходе Y может быть состояние 0 или 1. Кроме этого, некоторые мультиплексоры имеют выход, который может принимать три состояния: два логических состояния 0 и 1, и третье состояние — отключённый выход (высокоимпедансное состояние, часто говорят, Z -состояние — выходное сопротивление велико, выходной внутренний логический вентиль отключается от выхода специальным внутренним ключом). Такое техническое решение облегчает наращивание количества входных сигналов мультиплексора каскадированием нескольких микросхем мультиплексоров, при этом выходы микросхем просто электрически соединяются. Перевод мультиплексора в третье состояние производится подачей на вход OE (от англ. Output Enable) логической 1, чаще логического 0 — опять же зависит от модели конкретного мультиплексора. Использование Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры могут использоваться для преобразования параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и заканчивая последним. Обозначение Мультиплексоры обозначают сочетанием MUX (от англ. multiplexer), а также MS (от англ. multiplexer selector).

Рис. 46. Условное графическое обозначение (УГО) мультиплексора «4 в 1».

Демультиплексор

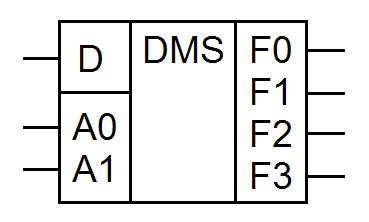

Рис. 47. Условное графическое обозначение (УГО) демультиплексора «1 в 4».

Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DM или DMS. Суть и схема реализации В случае ТТЛ логики для коммутации каналов применяются логические элементы "И". В КМОП-микросхемах широко применяются ключи на полевых транзисторах. Поэтому в них отсутствует понятие демультиплексора. Информационные входы и выход можно поменять местами, в результате чего мультиплексор может служить в качестве демультиплексора. Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют функцию входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров в отечественных микросхемах используются одинаковые буквы — ИД. Демультиплексоры выполняют унарные (одновходовые, однооперандные) логические функции с n-арным выходом.

Операции в АЛУ Все выполняемые в АЛУ операции являются логическими операциями (функциями), которые можно разделить на следующие группы: операции двоичной арифметики для чисел с фиксированной точкой; операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой; операции десятичной арифметики; операции индексной арифметики (при модификации адресов команд); операции специальной арифметики; операции над логическими кодами (логические операции); операции над алфавитно-цифровыми полями. Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами. К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»). Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство. Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами). Обширна группа операций редактирования алфавитно-цифровой информации. Каждая операция в АЛУ является логической функцией или последовательностью логических функций описываемых двоичной логикой для двоичных ЭВМ, троичной логикой для троичных ЭВМ, четверичной логикой для четверичных ЭВМ, десятичной логикой для десятичных ЭВМ и т. д.

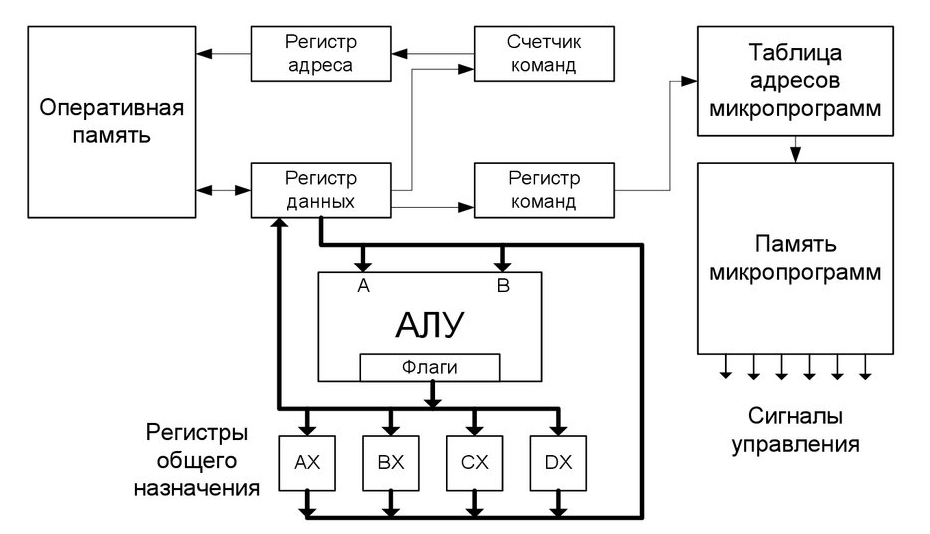

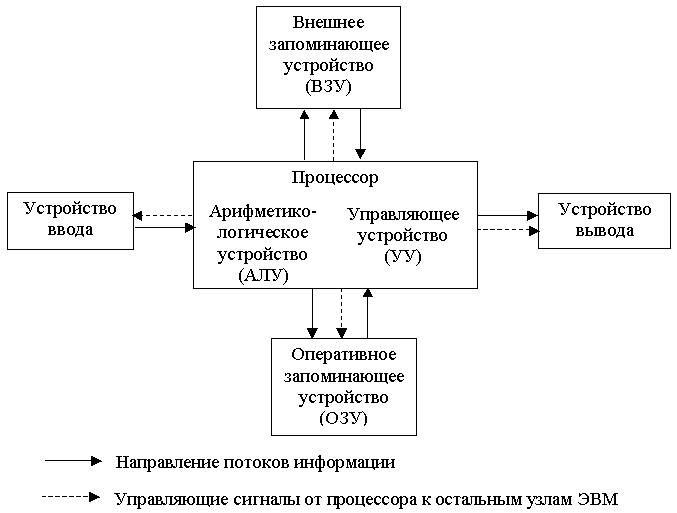

Классификация АЛУ По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ (они иногда называются микропрограммируемыми) операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами в процессе выполнения т. н. микропрограмм. При этом, каждой команде соответствует своя микропрограмма. На рисунке 49 представлена структура микропроцессорной системы с АЛУ последовательного типа. Главной особенностью структуры является наличие памяти микропрограмм (их нужно отличать от программ, выполняемых ЭВМ (микропроцессором или микроконтроллером), находящихся в ОЗУ!). Память микропрограмм содержит набор микропрограмм, каждая из которых управляет АЛУ и устройством управления микропроцессора для выполнения одной из команд, находящейся в регистре команд в настоящий момент времени.

Рис. 49. Структура микропроцессорной системы с микропрограммным управлением работой АЛУ.

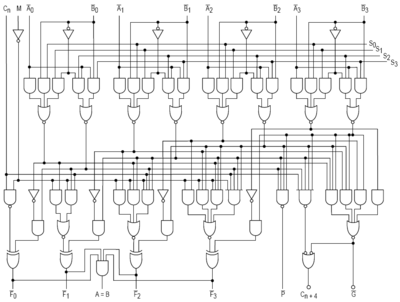

В параллельных АЛУ. Такие АЛУ также называются схемно-реализованными в виде сложных комбинационных логических схем. При этом каждой команде соответствует своя комбинационная схема.) операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов. Параллельные АЛУ по вполне понятным причинам быстрее последовательных, но гораздо сложнее и более энергозатратны. На рисунке 50 приведён пример схемно - реализованного АЛУ.

Рис. 50. Комбинационная логическая схема 4-битного АЛУ, реализованная в 24-выводной микросхеме ТТЛ, модель 74181, впервые разработанная и ранее изготавливаемая фирмой Texas Instruments. Выполняет сложение, вычитание, все элементарные логические функции и битовые сдвиги над двумя 4-битовыми операндами. Как и любая комбинационная схема не содержит в своем составе регистров.

По способу представления чисел различают АЛУ: для чисел с фиксированной точкой; для чисел с плавающей точкой; для десятичных чисел. По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы. По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметико-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами. АЛУ в микропроцессорной системе занимает важное место, поскольку от его возможностей по выполнению набора команд микропроцессора и производительности зависит эффективность работы микропроцессорной системы. На рисунке 51 представлена структурная схема ЭВМ с архитектурой фон-Неймана, который первым чётко определил состав узлов ЭВМ и место в ней АЛУ. .

Рис. 51. Структура микропроцессорной системы (ЭВМ или микроконтроллера).

Номер строки |

Управляющий код |

Выполняемая операция | |||||||||||

| K0 | K1 | K2 | K3 | PI | ||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | S = A + B | ||||||||

| 1 | 0 | 0 | 0 | 0 | 1 | S = A + B + 1 | ||||||||

| 2 | 0 | 0 | 0 | 1 | 0 | S = B − A − 1 | ||||||||

| 3 | 0 | 0 | 0 | 1 | 1 | S = B − A | ||||||||

| 4 | 0 | 0 | 1 | 0 | 0 | S = B − 1 | ||||||||

| 5 | 0 | 0 | 1 | 0 | 1 | S = B | ||||||||

| 6 | 0 | 0 | 1 | 1 | 0 | S = B | ||||||||

| 7 | 0 | 0 | 1 | 1 | 1 | S = B + 1 | ||||||||

| 8 | 0 | 1 | 0 | 0 | 0 | S = A − B − 1 | ||||||||

| 9 | 0 | 1 | 0 | 0 | 1 | S = A − B | ||||||||

| 10 | 0 | 1 | 0 | 1 | 0 | S = −A − B − 2 | ||||||||

| 11 | 0 | 1 | 0 | 1 | 1 | S = −A − B − 1 | ||||||||

| 12 | 0 | 1 | 1 | 0 | 0 | S = −B − 2 | ||||||||

| 13 | 0 | 1 | 1 | 0 | 1 | S = −B − 1 | ||||||||

| 14 | 0 | 1 | 1 | 1 | 0 | S = −B − 1 | ||||||||

| 15 | 0 | 1 | 1 | 1 | 1 | S = −B | ||||||||

| 16 | 1 | 0 | 0 | 0 | 0 | S = A − 1 | ||||||||

| 17 | 1 | 0 | 0 | 0 | 1 | S = A | ||||||||

| 18 | 1 | 0 | 0 | 1 | 0 | S = −A − 2 | ||||||||

| 19 | 1 | 0 | 0 | 1 | 1 | S = −A − 1 | ||||||||

| 20 | 1 | 0 | 1 | 0 | 0 | S = −2 | ||||||||

| 21 | 1 | 0 | 1 | 0 | 1 | S = −1 | ||||||||

| 22 | 1 | 0 | 1 | 1 | 0 | S = −1 | ||||||||

| 23 | 1 | 0 | 1 | 1 | 1 | S = 0 | ||||||||

| 24 | 1 | 1 | 0 | 0 | 0 | S = A | ||||||||

| 25 | 1 | 1 | 0 | 0 | 1 | S = A + 1 | ||||||||

| 26 | 1 | 1 | 0 | 1 | 0 | S = −A − 1 | ||||||||

| 27 | 1 | 1 | 0 | 1 | 1 | S = −A | ||||||||

| 28 | 1 | 1 | 1 | 0 | 0 | S = −1 | ||||||||

| 29 | 1 | 1 | 1 | 0 | 1 | S = 0 | ||||||||

| 30 | 1 | 1 | 1 | 1 | 0 | S = 0 | ||||||||

| 31 | 1 | 1 | 1 | 1 | 1 | S = +1 | ||||||||

Рис. 55. Коды математических операций арифметического устройства

Проанализируем эту таблицу. Если на все управляющие входы подать низкий потенциал (Управляющий код равен 0000), то к входу сумматора будут подключены коды A и B без инверсии. В этом случае будет производиться операция суммирования. Эта ситуация отображена первыми двумя строками таблицы выполняемых операций. Операция вычитания осуществляется второй, третьей, восьмой и девятой строкой. В этом случае один из операндов поступает на вход сумматора через блок инверторов. Правда для получения дополнительного кода не хватает единицы, но её можно подать на вход переноса сумматора PI. Ещё одной часто используемой операцией является увеличение числа на единицу или уменьшение числа на единицу. Эти операции позволяют легко организовывать циклы в программе и переходить от предыдущего операнда к следующему. Такие операции могут быть выполнены при помощи кодов, записанных в строках четыре, семь, шестнадцать и двадцать пять. Кроме того, схема арифметического устройства может просто передавать на выход любой из входных кодов без изменения, что позволяет осуществлять копирование данных (суммирование с константой ноль) через это устройство без дополнительных схем коммутации.

При небольшом изменении схемы такое устройство может быть преобразовано в схему, которая позволяет осуществлять не только арифметические, но и логические операции. Для этого нужно вести дополнительный коммутатор, который будет разрывать цепи переноса между разрядами. Эта управляющая цепь обычно называется M. Подобная схема реализована в микросхеме АЛУ К155ИП3 (иностранный аналог 74181). Ее внутренняя схема приведена на рисунке 56.

Рис. 56. Схема арифметико-логического устройства (АЛУ) К155ИП3

Подчеркнём основную особенность полученного устройства. Арифметико-логические устройства позволяют выбирать вид выполняемой операции при помощи кода, подаваемого на специальные выводы микросхемы. Это позволяет программировать одно и то же устройство для выполнения различных функций. Разработка такого устройства позволило обменивать большую скорость выполнения отдельных операций на сложность реализуемого алгоритма, что, в конце концов, привело к разработке микропроцессорных систем. Развитие этих систем изменило окружающий нас мир.

ЛЕКЦИЯ 10. ЛОГИЧЕСКИЕ И ЦИФРОВЫЕ УСТРОЙСТВА. 4 часа.

Логические вентили. Схемы инвертора, И, ИЛИ, ИЛИ-НЕ, И-НЕ на основе биполярных и МОП-транзисторов. Таблицы истинности. Сложные (комбинационные) схемы. Шифраторы. Дешифраторы.

Двоичные коды. Двоичная арифметика. Простейший сумматор.

Логические устройства последовательностного действия.

Триггерный эффект. Триггер. Состояния триггера. Счётный триггер и триггер - защёлка (D-триггер). Регистры и двоичные счётчики. Микропроцессор и микропроцессорная система.

Анализ функционирования логических схем