Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Микроархитектура процессоров 8086 и Pentium Pro

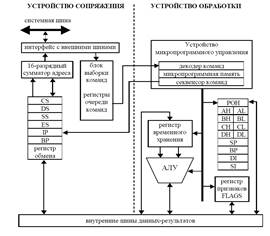

Микропроцессор 8086 ориентирован на выполнение команд параллельно с их выборкой и может быть условно разделен на две части, работающие асинхронно (см рис. ниже):

Устройство сопряжения обеспечивает формирование 20-разрядного физического адреса памяти, выборку команд и операндов из памяти, организацию очередности команд и запоминание результатов выполнения команд в памяти. В состав УС входит шесть 8-разрядных регистров очереди команд, четыре 16-разрядных сегментных регистра, 16-разрядный регистр обмена и 16-разрядный сумматор адреса, интерфейс с внешними шинами. Регистры очереди команд организованы по принципу FIFO - «первым пришел - первым вышел». УС готово выполнить цикл выборки 16-разрядного слова из памяти всякий раз, когда в очереди освобождаются, по меньшей мере, два байта, а УО извлекает из очереди команды по мере их выполнения. При выполнении команд передачи управления, например условных и безусловных переходов, очередь очищается УС и начинает заполняться заново.

Рисунок 1.Микроархитектура процессора In tel 8086. Устройство обработки предназначено для выполнения операций по обработке данных и состоит из устройства микропрограммного управления (УМУ), 16-разрядного АЛУ, восьми 16-разрядных регистров общего назначения и регистра признаков. Команды из очереди, сформированной УС, поступают в УМУ, где декодируются и выполняются в 16-разрядном АЛУ согласно процедурам, записанным в памяти микропрограмм. Последовательное выполнение команд обеспечивается секвенсором команд, часть которого (регистр счетчика команд IP) изображена в составе УС, т.к. именно УС записывает в IP смещение следующей команды, т.е. положение новой команды относительно начала сегмента команд. УО обменивается данными с УС через внутреннюю 16-разрядную шину и регистр обмена.

Для сравнения приводится (рис. 2) микроархитектура процессоров 39 шестого поколения Pentium Pro. Как видно, архитектура со времени 8086 претерпела не только количественные (разрядность внутренних и внешних шин данных, регистров), но и существенные качественные изменения. Pentium Pro имеет суперскалярную архитектуру, т.е. может одновременно вы-полнять несколько команд за один такт. Эту возможность обеспечивают несколько АЛУ - два блока целочисленной арифметики и два блока с плавающей точкой. Другая важная особенность – т.н. динамическое исполнение – команды разбиваются на простейшие операции, порядок независимого исполнения которых определяется блоком «завершения и удаления микрокоманд» с буферами переупорядочивания и пулом микрокоманд (рис. 2.).

Рисунок 2. Микроархитектура процессора P ent i um Pro.

На рис. 3 представлены обозначения микропроцессоров для принципиальных электрических схем, на которых видны внешние шины и сигналы 16-разрядного 8086 и 32-разрядного 80486.

Рисунок 3. Обозначения микропроцессоров для принципиальных электрических схем.

Регистры.

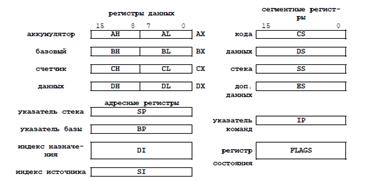

Микропроцессор 8086 имеет 12 программно-доступных шестнадцатиразрядных регистров, регистр счетчика команд IP (Instruction Pointer) и регистр флагов (или регистр состояния процессора) FLAGS. Среди программно-доступных регистров выделяют следующие группы (см. рис. 4):

16-битные регистры AX, BX, CX, DX состоят из двух 8-битных половин, к которым можно независимо обращаться по именам AH, BH, CH, DH - старшие байты и AL, BL, CL, DL - младшие байты.

Рисунок 4. Регистры процессора 8086. Биты (или флаги) регистра признаков FLAGS разделяются на условные, отражающие результат предыдущей операции ALU, и управляющие, от которых зависит выполнение специальных функций.

Рисунок 5. Флаги процессора Intel 8086.

Флаги TF, IF, DF относятся к управляющим флагам, остальные - к условным (флагам состояния). Флаги отражают следующие условия:

Организация памяти.

Хотя процессор имеет 20-разрядную адресную шину, которая соединяет его с физической памятью, он оперирует с 16-битными логическими адресами, состоящими из 16-разрядного базового адреса сегмента и 16-разрядного смещения в сегменте. Физические, 20-разрядные адреса данных и команд формируются путем сложения содержимого регистров указателей и смещенного на 4 бита влево содержимого сегментных регистров. Т.н. эффективный адрес данных получается как сумма содержимого регистров BX или BP, содержимого регистров SI или DI и смещения. Затем из эффективного адреса и содержимого сегментного регистра формируется физический адрес (Рис. 2.6). В формировании физического адреса команды участвуют IP и CS. Таким образом, адресное пространство разбивается на 4 сегмента емкостью 64К адресов по числу сегментных регистров. Регистр CS указывает на текущий сегмент кода (программы), откуда выбираются команды. Регистр DS указывает на текущий сегмент данных, в котором содержатся переменные. Регистр SS адресует текущий сегмент стека, в котором реализуются все стековые операции. Наконец, регистр ES определяет текущий дополнительный сегмент данных. Смещенное содержимое сегментного регистра определяет положение сегмента в 20-разрядном адресном пространстве, а регистры-указатели определяют положение команды или данных внутри сегментов. Поскольку при формировании эффективного адреса содержимое сегментного регистра сдвигается на 4 бита, сегмент всегда начинается с адреса, кратного 16, т.е. на границе 16-байтового блока памяти (параграфа). Сегменты в памяти могут располагаться как последовательно, так и с наложением друг на друга. Если программа превышает 64 Кбайт, то необходимо перезагружать сегментный регистр CS новым значением базового адреса. Точно также, если данные превышают 64 Кбайт, то необходимо перезагрузить регистр DS.

Рисунок 6. Формирование физического адреса данных и колманд.

Память организована в виде одномерного массива байтов с физическими адресами от 0000016 до FFFFF16. Две области адресного пространства памяти зарезервированы для выполнения специальных функций, связанных с обработкой прерываний и системным сбросом. Этими областями являются первые 128 байт (физические адреса 00000 - 0007F) и последние 16 байт (физические адреса FFFF0 - FFFFF). Данные области использовать для других целей нельзя.

Байты в памяти организуются в слова таким образом, что байту, имеющему меньший адрес, соответствуют менее значимые позиции разрядов в слове. Каждый байт или слово памяти адресуется с помощью 20-битного адреса, причем в случае адресации слова адрес указывает на его младшую часть. Например, адрес 0000016 может обозначать и байт с этим адресом, что условно записывается в виде [00000] = 34h, и слово с таким же адресом, что записывается в виде [00000] = 1234h. Тогда старший байт слова, [00001] = 12h. Квадратные скобки обозначают ячейку памяти, адрес которой находится в этих скобках, h – шестнадцатеричную систему счисления. Команды, байты и слова можно размещать по любому адресу байта, однако рекомендуется размещать слова в памяти по четным адресам, так как процессор может передавать такие слова за один цикл обращения к памяти. Слово с четным адресом называется выравненным на границу слова. Слова с нечетными адресами (невыравненные) также допустимы, однако они считываются в два раза медленнее (требуют два цикла обращения к памяти).

Форматы команд.

Команды i8086 имеют переменную длину от 1 до 6 байт. По числу обрабатываемых операндов команды подразделяются на безадресные, одноадресные и двухадресные. В двухадресных командах результат всегда записывается по первому адресу и только один из операндов может находиться в памяти. При этом в мнемонике, операнд-приемник записывается слева от запятой-разделителя операндов, а операнд-источник – справа. Всего существует четыре источника операндов: тело команды, регистр, память и порт ввода/вывода. В первом случае операнд называется непосредственным. Первый байт команды содержит код операции (КОП), в состав которого могут входить специальные разряды d, s и w. При w=1 операции выполняются с 16-разрядными словами, при w=0 – с байтами. Разряд d определяет направление передачи данных в двухоперандных командах: из регистра в регистр/память (d=0) или из регистра/памяти в регистр (d=1). S – определяет расширение 8-битных непосредственных данных до полного размера (s=1) или нет (s=0). При некоторых сочетаниях команд и методов адресации (регистровый метод адресации) положение операнда может задаваться непосредственно в байте кода операции (см. следующий раздел), но чаще для этого используется т.н. «постбайт».

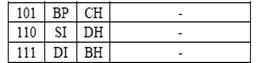

В командах, имеющих длину 2 и более байта, второй байт называется постбайтом. Он выполняет функции кодирования адресов операндов. Байты 3 - 6 присутствуют в команде в зависимости от типа адреса операнда, описанного постбайтом и наличия непосредственного операнда. Постбайт состоит из трех полей: режима - MOD, регистра - REG и регистра/памяти - R/M. Поле MOD занимает 2 бита (6 и 7) постбайта. Поле REG занимает 3 бита (3-5) постбайта. Поле R/M занимает 3 бита (0-2) постбайта. Полями MOD и R/M совместно кодируется тип адреса операнда, находящегося в памяти или регистре. 32 значения этих полей определяют нахождение операнда 24 возможными методами адресации либо в одном из 8 регистров. Ниже приведена структура байта кода операции и постбайта, а в таблицах показано формирование адресов регистровых операндов и адресов операндов памяти. DISP8 и DISP16 – смещения длиной 8 и 16 бит, расположенные в команде непосредственно за байтом адресации.

Рисунок 7. Формат байта КОП и постбайта.

Таблица 1. Формат поля REG.

Таблица 2.Кодирование типа адреса операнда. Команде может предшествовать префикс – байт со специальным кодированием, которое изменяет операцию следующей за ним команды. В системе команд процессоров 8086/8088 есть два таких префикса – REP (REPeat) для повторения команд обработки строк и SEG (SEGment) для прямого указания команде сегментного регистра вместо регистра, используемого по умолчанию.

Методы адресации.

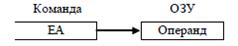

Методы адресации можно разделить на два класса: адресация данных и адресация переходов. Все методы можно отнести к одной из следующих групп: Прямая адресация. 16-битный эффективный адрес (EA) операнда является частью команды:

Пример: mov al, [0000h]

Примечание: запись в квадратных скобках обозначает ячейку, адрес которой (смещение по отношению к DS) записан в квадратных скобках. Регистровая адресация. Операнд содержится в определяемом командой регистре. 16-битный операнд может находиться в регистрах AX, BX, CX, DX, SI, DI, SP или BP, а 8-битный - в регистрах AH, AL, BH, BL, CH, CL, DH, DL:

Пример: mov ax, bx

|

||||||||

|

Последнее изменение этой страницы: 2021-06-14; просмотров: 71; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.218.172.210 (0.023 с.) |