Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Раздел 2. Архитектура и системы команд современных пэвм.Стр 1 из 6Следующая ⇒

Раздел 2. Архитектура и системы команд современных ПЭВМ.

Тема 2.1. Архитектура IA-16.

План: 1. Структура Intel 8086. 2. Регистры. 3. Организация памяти. 4. Форматы команд. 5. Методы адресации. 6. Система команд. 7. Типы данных. 8. Математический сопроцессор. 9. Организация ввода-вывода. 10. Организация прерываний.

Структура Intel x86.

Первым представителем семейства Intel x86, или, согласно официальной классификации фирмы Intel (Int egrated El ectronics, США), семейства процессоров IA (Intel Architecture), является микропроцессор 8086, разработанный к 1978 году. Программы, написанные для него, выполняются на всех последующих процессорах семейства, включая все современные модели.

Регистры.

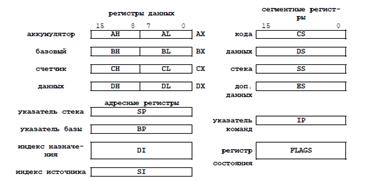

Микропроцессор 8086 имеет 12 программно-доступных шестнадцатиразрядных регистров, регистр счетчика команд IP (Instruction Pointer) и регистр флагов (или регистр состояния процессора) FLAGS. Среди программно-доступных регистров выделяют следующие группы (см. рис. 4):

16-битные регистры AX, BX, CX, DX состоят из двух 8-битных половин, к которым можно независимо обращаться по именам AH, BH, CH, DH - старшие байты и AL, BL, CL, DL - младшие байты.

Рисунок 4. Регистры процессора 8086. Биты (или флаги) регистра признаков FLAGS разделяются на условные, отражающие результат предыдущей операции ALU, и управляющие, от которых зависит выполнение специальных функций.

Рисунок 5. Флаги процессора Intel 8086.

Флаги TF, IF, DF относятся к управляющим флагам, остальные - к условным (флагам состояния). Флаги отражают следующие условия:

Организация памяти.

Хотя процессор имеет 20-разрядную адресную шину, которая соединяет его с физической памятью, он оперирует с 16-битными логическими адресами, состоящими из 16-разрядного базового адреса сегмента и 16-разрядного смещения в сегменте. Физические, 20-разрядные адреса данных и команд формируются путем сложения содержимого регистров указателей и смещенного на 4 бита влево содержимого сегментных регистров. Т.н. эффективный адрес данных получается как сумма содержимого регистров BX или BP, содержимого регистров SI или DI и смещения. Затем из эффективного адреса и содержимого сегментного регистра формируется физический адрес (Рис. 2.6). В формировании физического адреса команды участвуют IP и CS. Таким образом, адресное пространство разбивается на 4 сегмента емкостью 64К адресов по числу сегментных регистров. Регистр CS указывает на текущий сегмент кода (программы), откуда выбираются команды. Регистр DS указывает на текущий сегмент данных, в котором содержатся переменные. Регистр SS адресует текущий сегмент стека, в котором реализуются все стековые операции. Наконец, регистр ES определяет текущий дополнительный сегмент данных. Смещенное содержимое сегментного регистра определяет положение сегмента в 20-разрядном адресном пространстве, а регистры-указатели определяют положение команды или данных внутри сегментов.

Поскольку при формировании эффективного адреса содержимое сегментного регистра сдвигается на 4 бита, сегмент всегда начинается с адреса, кратного 16, т.е. на границе 16-байтового блока памяти (параграфа). Сегменты в памяти могут располагаться как последовательно, так и с наложением друг на друга. Если программа превышает 64 Кбайт, то необходимо перезагружать сегментный регистр CS новым значением базового адреса. Точно также, если данные превышают 64 Кбайт, то необходимо перезагрузить регистр DS.

Рисунок 6. Формирование физического адреса данных и колманд.

Память организована в виде одномерного массива байтов с физическими адресами от 0000016 до FFFFF16. Две области адресного пространства памяти зарезервированы для выполнения специальных функций, связанных с обработкой прерываний и системным сбросом. Этими областями являются первые 128 байт (физические адреса 00000 - 0007F) и последние 16 байт (физические адреса FFFF0 - FFFFF). Данные области использовать для других целей нельзя. Байты в памяти организуются в слова таким образом, что байту, имеющему меньший адрес, соответствуют менее значимые позиции разрядов в слове. Каждый байт или слово памяти адресуется с помощью 20-битного адреса, причем в случае адресации слова адрес указывает на его младшую часть. Например, адрес 0000016 может обозначать и байт с этим адресом, что условно записывается в виде [00000] = 34h, и слово с таким же адресом, что записывается в виде [00000] = 1234h. Тогда старший байт слова, [00001] = 12h. Квадратные скобки обозначают ячейку памяти, адрес которой находится в этих скобках, h – шестнадцатеричную систему счисления. Команды, байты и слова можно размещать по любому адресу байта, однако рекомендуется размещать слова в памяти по четным адресам, так как процессор может передавать такие слова за один цикл обращения к памяти. Слово с четным адресом называется выравненным на границу слова. Слова с нечетными адресами (невыравненные) также допустимы, однако они считываются в два раза медленнее (требуют два цикла обращения к памяти).

Форматы команд.

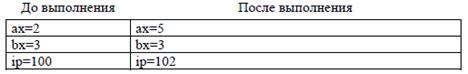

Команды i8086 имеют переменную длину от 1 до 6 байт. По числу обрабатываемых операндов команды подразделяются на безадресные, одноадресные и двухадресные. В двухадресных командах результат всегда записывается по первому адресу и только один из операндов может находиться в памяти. При этом в мнемонике, операнд-приемник записывается слева от запятой-разделителя операндов, а операнд-источник – справа. Всего существует четыре источника операндов: тело команды, регистр, память и порт ввода/вывода. В первом случае операнд называется непосредственным. Первый байт команды содержит код операции (КОП), в состав которого могут входить специальные разряды d, s и w. При w=1 операции выполняются с 16-разрядными словами, при w=0 – с байтами. Разряд d определяет направление передачи данных в двухоперандных командах: из регистра в регистр/память (d=0) или из регистра/памяти в регистр (d=1). S – определяет расширение 8-битных непосредственных данных до полного размера (s=1) или нет (s=0). При некоторых сочетаниях команд и методов адресации (регистровый метод адресации) положение операнда может задаваться непосредственно в байте кода операции (см. следующий раздел), но чаще для этого используется т.н. «постбайт».

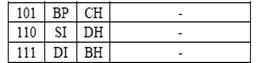

В командах, имеющих длину 2 и более байта, второй байт называется постбайтом. Он выполняет функции кодирования адресов операндов. Байты 3 - 6 присутствуют в команде в зависимости от типа адреса операнда, описанного постбайтом и наличия непосредственного операнда. Постбайт состоит из трех полей: режима - MOD, регистра - REG и регистра/памяти - R/M. Поле MOD занимает 2 бита (6 и 7) постбайта. Поле REG занимает 3 бита (3-5) постбайта. Поле R/M занимает 3 бита (0-2) постбайта. Полями MOD и R/M совместно кодируется тип адреса операнда, находящегося в памяти или регистре. 32 значения этих полей определяют нахождение операнда 24 возможными методами адресации либо в одном из 8 регистров. Ниже приведена структура байта кода операции и постбайта, а в таблицах показано формирование адресов регистровых операндов и адресов операндов памяти. DISP8 и DISP16 – смещения длиной 8 и 16 бит, расположенные в команде непосредственно за байтом адресации.

Рисунок 7. Формат байта КОП и постбайта.

Таблица 1. Формат поля REG.

Таблица 2.Кодирование типа адреса операнда. Команде может предшествовать префикс – байт со специальным кодированием, которое изменяет операцию следующей за ним команды. В системе команд процессоров 8086/8088 есть два таких префикса – REP (REPeat) для повторения команд обработки строк и SEG (SEGment) для прямого указания команде сегментного регистра вместо регистра, используемого по умолчанию.

Методы адресации.

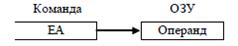

Методы адресации можно разделить на два класса: адресация данных и адресация переходов. Все методы можно отнести к одной из следующих групп: Прямая адресация. 16-битный эффективный адрес (EA) операнда является частью команды:

Пример: mov al, [0000h]

Примечание: запись в квадратных скобках обозначает ячейку, адрес которой (смещение по отношению к DS) записан в квадратных скобках. Регистровая адресация. Операнд содержится в определяемом командой регистре. 16-битный операнд может находиться в регистрах AX, BX, CX, DX, SI, DI, SP или BP, а 8-битный - в регистрах AH, AL, BH, BL, CH, CL, DH, DL:

Пример: mov ax, bx

Непосредственная адресация. Операнд длиной байт или слово является частью команды. Операнд помещается в последние байты команды, причем младший байт следует первым (находится по меньшему адресу).

Пример: mov ax, 1234h

Неявная адресация. Неявная адресация задается операцией. Например, в командах обработки строк неявно используются регистры SI, DI. В командах управления циклами неявно используется регистр CX и т.д.

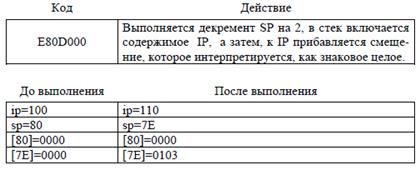

Стековая адресация. Стековая адресация применяется в командах работы со стеком PUSH и POP. Для этих команд адрес операнда находится в указателе стека SP и автоматически уменьшается или увеличивается на два при записи в стек или при чтении из стека. Заполнение стека происходит в направлении уменьшения адресов ячеек памяти. Стек может обмениваться данными с регистрами общего назначения и сегментными регистрами. Команды обмена данными между стеком и памятью содержат байт адресации, в котором 3-разрядное поле REG, совместно с полем КОП, идентифицирует команду.

Рисунок 8. Работа со стеком.

Пример: jmp 100

Система команд.

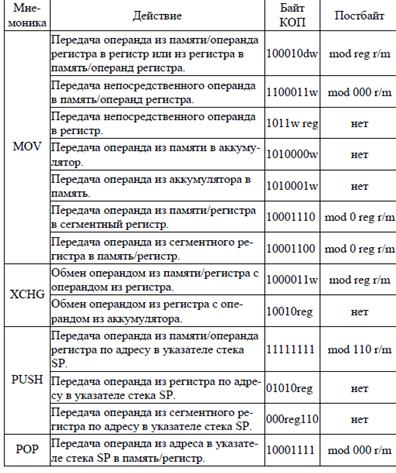

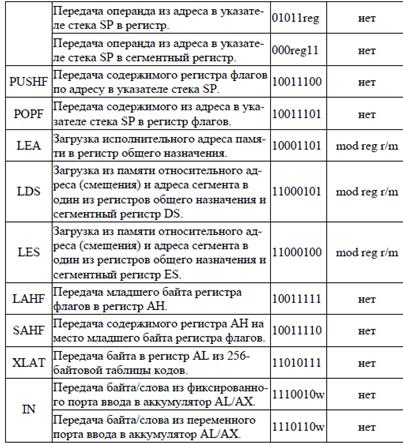

Команды передачи данных предназначены для пересылок данных между регистрами и памятью. Эту группу команд можно разделить на четыре подгруппы: команды пересылки данных общего назначения; команды, использующие аккумулятор; команды пересылки адресных объектов; команды пересылки флагов. Все команды этой группы не влияют на установку флагов, за исключением команд SAHF и POPF.

Пример: mov ax, bx

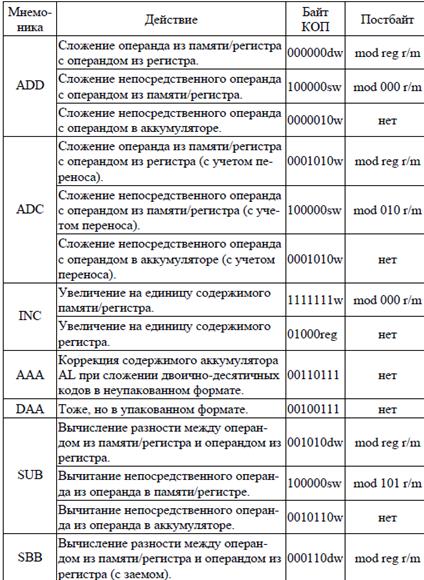

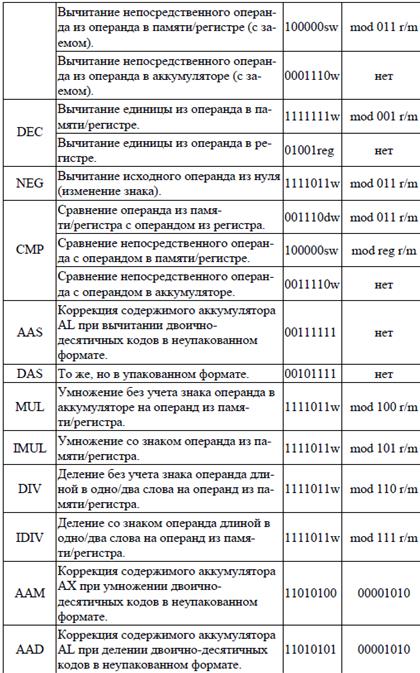

Арифметические команды предназначены для выполнения четырех основных видов арифметических действий над 8- и 16- разрядными операндами в знаковом и беззнаковом представлении. Кроме основных арифметических команд имеются операции коррекции арифметических результатов для их перевода в упакованную или неупакованную форму. Признаки полученного результата отображаются в 6 битах регистра Flags (CF, AF, SF, ZF, PF и OF).

Пример: add ax, bx

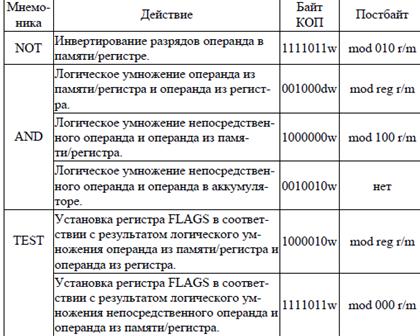

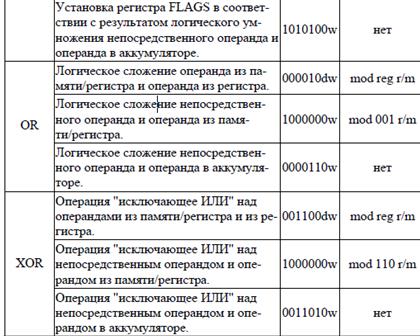

Логические команды предназначены для выполнения четырех логических действий над 8- и 16-битовыми логическими структурами: получение инверсного кода, логическое произведение, логическая сумма, сумма по модулю два. Команды AND, TEST, OR и XOR воздействуют на арифметические флаги следующим образом: флаги OF и CF всегда сбрасываются в нулевое состояние; состояния флагов SF, ZF, PF зависят от полученного результата и определяются по тем же правилам, что и в командах арифметических операций; состояние флага AF не определено. Команда NOT не влияет на состояние флагов.

Пример: not ax

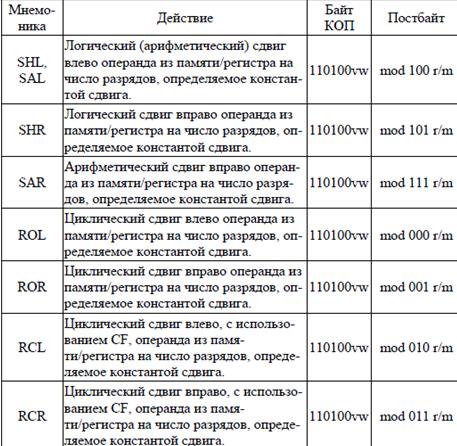

Команды сдвига предназначены для выполнения логических, арифметических и циклических сдвигов. Поле операнда имеет формат mem/reg, count. Здесь mem/reg адресует регистр или ячейку памяти, а count (счет или счетчик) определяет число сдвигов. Число сдвигов может быть указано как константа 1 (статический сдвиг) или как регистр CL. В первом случае осуществляется сдвиг на один байт, а во втором - число сдвигов определяется содержимым регистра CL, которое должно быть беззнаковым целым двоичным числом. Таким образом, число сдвигов можно задать переменной, вычисляемой во время выполнения программы (так называемый динамический сдвиг). При выполнении команд сдвигов флаги изменяются следующим образом:

Пример: shl ax, 1

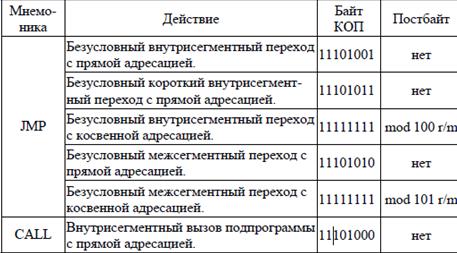

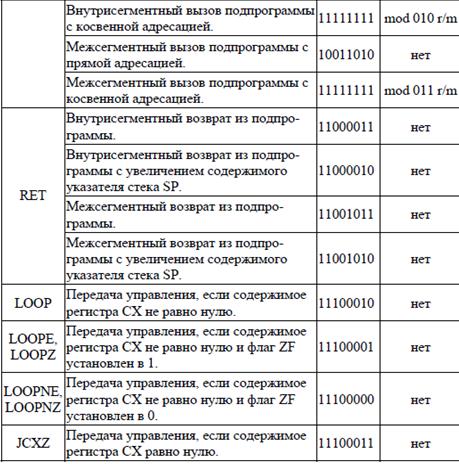

Команды передачи управления включают в себя безусловные переходы, команды обращения к подпрограммам и возврата из них, а также команды управления циклами. Выполнение этих команд приводит к изменению содержимого указателя команд IP и регистра CS. Команды безусловных переходов и обращений к подпрограммам обеспечивают как внутрисегментные, так и межсегментные переходы с прямой и косвенной адресацией. Команды управления циклами обеспечивают переход только в области текущего сегмента с коротким смещением.

Пример: jmp 110

Пример: call 110

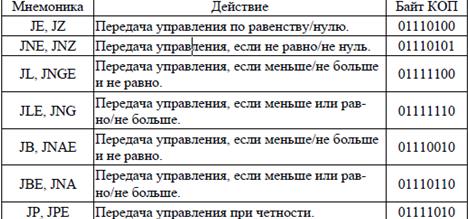

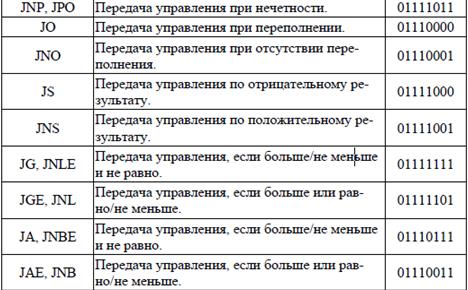

Команды условных переходов обеспечивают только внутрисегментные переходы.

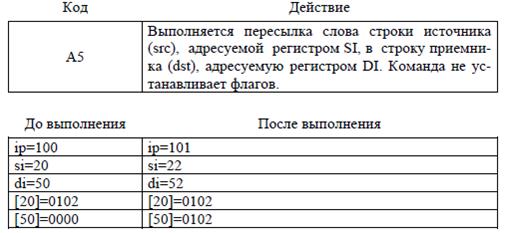

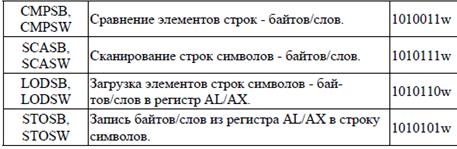

Команды обработки строк Все команды обработки строк символов имеют длину один байт. Бит 0 показывает операцию с байтом (бит 0=0) или словом (бит 0=1).

Пример: movsw

Пример: rep movsw

Типы данных.

Простые типы данных в ассемблере:

Синтаксис декларирования данных в ассемблере следующий: <имя> <директива> <выражение> <имя> - некоторое символическое имя метки или ячейки памяти в сегменте данных, используемое в программе; <директива> - зарезервированное слово для указания типа объявляемых данных; <выражение> - может содержать константу или «?» (неопределенное значение). Таким образом:

Определение последовательности повторяющихся данных: выражение1 DUP (выражение2)

ЕСЛИ выражение2 =? ТО это неинициализируемые данные

ДИРЕКТИВА ОПРЕДЕЛЕНИЯ БАЙТА (DB)

Из различных директив, определяющих элементы данных, наиболее полезной является DB (определить байт). Символьное выражение в диpективе DB может содержать строку символов любой длины, вплоть до конца строки. Числовое выражение в директиве DB может содержать одну или более однобайтовых констант. Один байт выражается двумя шестнадцатеричными цифpами. Наибольшее положительное шестнадцатеричное число в одном байте это 7f, все "большие" числа от 80 до ff представляют отрицательные значения. В десятичном исчислении эти пределы выражаются числами +127 и -128.

ДИРЕКТИВА ОПРЕДЕЛЕНИЯ СЛОВА (DW)

Директива DW определяет элементы, которые имеют длину в одно слово (два байта). Символьное выражение в DW ограничено двумя символами, которые ассемблер представляет в объектном коде так, что, например, 'pc' становится 'cp'. Для определения символьных строк директива DW имеет ограниченное применение. Числовое выражение в DW может содержать одно или более двухбайтовых констант. Два байта представляются четырьмя шестнадцатеричными цифрами. Наибольшее положительное шестнадцатеричное число в двух байтах это 7fff; все "большие" числа от 8000 до ffff представляют отрицательные значения. В десятичном исчислении эти пределы выражаются числами +32767 и -32768. Для форматов директив DW, DD и DQ ассемблер преобразует константы в шестнадцатеричный объектный код, но записывает его в обратной последовательности. Таким образом, десятичное значение 12345 преобразуется в шестнадцатеричное 3039, но записывается в объектном коде как 3930.

ДИРЕКТИВА ОПРЕДЕЛЕНИЯ ДВОЙНОГО СЛОВА (DD)

Директива DD определяет элементы, которые имеют длину в два cлова (четыре байта). Числовое выражение может содержать одну или более констант, каждая из которых имеет максимум четыре байта (восемь шестнадцатеричных цифр). Наибольшее положительное шестнадцатеричное число в четырех байтах это 7fffffff; все "большие" числа от 80000000 до ffffffff представляют отрицательные значения. В десятичном исчислении эти пределы выражаются числами +2147483647 и -2147483648. Ассемблер преобразует все числовые константы в директиве DD в шестнадцатеричное представление, но записывает объектный код в обратной последовательности. Таким образом, десятичное значение 12345 преобразуется в шестнадцатеричное 00003039, но записывается в oбъектном коде как 39300000. Символьное выражение директивы DD ограничено двумя символами. Ассемблер преобразует символы и выравнивает их слева в четырехбайтовом двойном слове в объектном коде.

ДИРЕКТИВА ОПРЕДЕЛЕНИЯ УЧЕТВЕРЕННОГО СЛОВА (DQ)

Директива DQ определяет элементы, имеющие длину четыре слова (восемь байт). Числовое выражение может содержать одну или более констант, каждая из которых имеет максимум восемь байт или 16 шестнадцатеричных цифр. Наибольшее положительное шестнадцатеричное число - это семерка и 15 цифр f. Для получения представления о величине этого числа, покажем, что шестнадцатеричное 1 и 15 нулей эквивалентен следующему десятичному числу: 1152921504606846976 Обработка ассемблером символьных строк в директиве DQ aналогично директивам DD и DW.

ДИРЕКТИВА ОПРЕДЕЛЕНИЯ ДЕСЯТИ БАЙТ (DT)

Директива DT определяет элементы данных, имеющие длину в десять байт. Назначение этой директивы связано с "упакованными десятичными" числовыми величинами. По директиве DT генерируются различные константы, в зависимости от версии ассемблера.

Константные выражения.

Символьные строки.

Символьная строка используются для описания данных, таких как, например, имена людей или заголовки страниц. Содержимое строки oтмечается одиночными кавычками, например, 'pc' или двойными кавычками - "pc". Ассемблер переводит символьные строки в объектный код в обычном формате ASCII. Символьная строка определяется только директивой DB, в котоpой указывается более двух символов в нормальной последовательности слева направо. Следовательно, директива DB представляет единственно возможный формат для определения символьных данных.

Целые числа: [ знак ] последовательность_цифр [ признак_системы_счисления ] Признак системы счисления (СС): 1. B -двоичная, 2. Q или O - восьмеричная, 3. D - десятичная, 4. H - шестнадцатеричная(если число начинается с цифр A..F, то впереди должна быть вставлена цифра 0). Например:

42q 00100010b 22h 34d 34 0A34h

По умолчанию в ASM86 считается обычно десятичная. В MACRO-11 - восьмеричная. Умалчиваемая система счисления может быть переопределена директивой .RADIX. Например: RADIX 8

Вообще, числовые константы используются для арифметических величин и для aдресов памяти. Для описания константы кавычки не ставятся. Ассемблер преобразует все числовые константы в шестнадцатеричные и записывает байты в объектном коде в обратной последовательности - справа налево. Ниже показаны различные числовые форматы.

Десятичный формат.

Десятичный формат допускает десятичные цифры от 0 до 9 и обозначается последней буквой d, которую можно не указывать, например, или 125d. Несмотря на то, что ассемблер позволяет кодирование в десятичном формате, он преобразует эти значения в шестнадцатеричный объектный код. Например, десятичное число 125 преобразуется в шестнадцатеричное 7d.

Шестнадцатиричный формат.

Шестнадцатиричный формат допускает шестнадцатеричные цифры от 0 до f и обозначается последней буквой h. Так как ассемблер полагает, что с буквы начинаются идентификаторы, то первой цифрой шестнадцатеричной константы должна быть цифра от 0 до 9. Например, 2eh или 0fffh, которые ассемблер преобразует соответственно в 2e и ff0f (байты во втором примере записываются в объектный код в обратной последовательности).

Двоичный формат.

Двоичный формат допускает двоичные цифры 0 и 1 и обозначается последней буквой b. Двоичный формат обычно используется для более четкого представления битовых значений в логических командах and, or, xor и test. Десятичное 12, шестнадцатеричное c и двоичное 1100b все генерируют один и тот же код: шестнадцатеричное 0c или двоичное 0000 1100 в зависимости от того, как вы рассматриваете содержимое байта.

Восьмеричный формат.

Восьмеричный формат допускает восьмеричные цифры от 0 до 7 и обозначается последней буквой q или o, например, 253q. На сегодня восьмеричный формат используется весьма редко. Организация ввода-вывода.

Работа с портами ввода/вывода в процессорах x86 возможна как с использованием специальных команд (IN, OUT), через отдельное адресное пространство ввода/вывода, так и по схеме с отображением регистров устройств на обычное адресное пространство. В последнем случае возможно использование обычных команд из системы команд процессора. Для адресации портов устройств в пространстве ввода/вывода, используется 16-разрядный адрес, обеспечивая доступ к 64K 8-битным портам с адресами от 0h до FFFFh. Адреса 0F8h – 0FFh– зарезервированы для системных целей. Порты с адресами 0h – 0FFh используются оборудованием системной платы ПК (таймер, контроллер прерываний и т.п.), адреса 0100h–03FFh используют различные контроллеры: дисков, видеомонитора, компьютерной сети. Команды IN и OUT работают с прямой адресацией (адрес порта находится в команде) для портов с адресами 0h - 0F7h и с косвенной адресацией (адрес порта находится в регистре DX) для любых портов: 0h - FFFFh. Обмен данными происходит только через регистр-аккумулятор (AX, AL), например, чтение из порта: in al,dx, запись в порт: out dx,ax

Организация прерываний.

Прерывания - приостановление основных вычислений в процессоре, для выполнения вспомогательных действий, технологических сервисных процедур – можно разделить на два класса: внешние и внутренние. Каждому прерыванию назначен четырехбайтный вектор с номером в диапазоне 0h - FFh. Векторы определяют адреса подпрограмм обслуживания прерывания (ISR, Interrupt Service Routine) и размещаются в младшем килобайте адресного пространства памяти в виде IP:CS (сегмент_ISR:смещение_ISR, смещение записывается по младшему адресу). Внешние прерывания вызываются сигналами на входах (см. рис. 9) запроса немаскируемого прерывания процессора (NMI) и маскируемого прерывания (INTR). Маскируемые прерывания игнорируются, если очищен флаг I.

Рисунок 9. Источники прерываний.

После завершения выполнения текущей команды процессор вырабатывает сигналы подтверждения (INTA), получает по шине данных номер прерывания от контроллера прерываний, сохраняет в стеке текущее содержимое Flags, CS, IP и приступает к выполнению ISR, загружая содержимое вектора в CS, IP. В начале выполнения ISR процессор очищает флаг I, запрещая дальнейшие прерывания. Если необходимо, в подпрограмме ISR можно разрешить дальнейшие прерывания, установив флаг I (с помощью команды STI). Подпрограмма ISR должна заканчиваться командой IRET, которая загружает старые значения IP, CS, Flags из стека и т.о. возобновляет работу прерванной программы. Запросы от различных устройств в ПК обрабатываются контроллером прерываний, который формирует сигнал INTR для процессора (рис. 9). Обычно это две микросхемы Intel8259, каждая из которых имеет 8 входов прерываний. Запросам прерываний IRQ0-IRQ7 ПК соответствуют векторы от 08h до 0Fh, а IRQ8-IRQ15 – векторы от 070h до 077h. Битовые маски, позволяющие запрещать (маскировать) отдельные входы запросов прерываний, находятся по адресам 021h и 0A1h для IRQ0-IRQ7 и IRQ8-IRQ15 соответственно. К внутренним прерываниям относятся т.н. исключения – различного рода ошибки, механизм для отлаживания программ, аварийные состояния и командные прерывания INT:

Вход для немаскируемых прерываний с вектором 2 используется для подачи сигналов о серьезных аварийных состояниях, требующих немедленного обслуживания, например, об отсутствии напряжения в сети. Раздел 2. Архитектура и системы команд современных ПЭВМ.

|

|||||||||

|

Последнее изменение этой страницы: 2021-06-14; просмотров: 212; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 52.15.63.145 (0.197 с.) |