Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Таблица 2.5.1. Основные типы триггеров. Конечные автоматы. Описание поведения цифрового автоматаСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

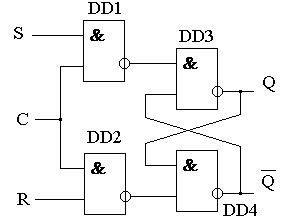

2. Прочерк в таблице переходов означает, что на данный информационный вход может быть подан произвольный логический сигнал (либо «0», либо «1»). Обычно все типы триггеров дополнительно снабжаются асинхронными входами R и S, которые воздействуют непосредственно на элемент памяти. Эти входы позволяют устанавливать или сбрасывать триггер вне зависимости от остальных информационных сигналов. На рис. 2.5.4 приведены логическая схема и обозначение синхронного RS -триггера с асинхронными установочными входами.

Т а б л и ц а 2.5.2. Варианты использования JK -триггера

Из приведенной таблицы следует, что кроме D -триггера, для получения остальных типов триггеров на входы JK -триггер просто необходимо подать соответствующие комбинации сигналов. Следует отметить, что при подаче одновременно активных сигналов на входы J и K, JK- триггер начинает работать как счетный. Это следствие наличие в его внутренней структуре дополнительных цепей обратной связи. 2.5.3. Конечные автоматы. Ранее отмечалось, что если блок обратной связи обобщенной структурной схемы (см. рис. 2.5.1) последовательностного устройства содержит элементы памяти, например триггеры, то полученная структура является конечным автоматом. Термин «конечный» означает, что число выходных сигналов, и, следовательно, состояний автомата, является ограниченным. Введем понятие состояние автомата. Это понятие уже вводилось ранее для одиночного триггера и под ним понимался выходной сигнал триггера. В общем случае, блок обратной связи автомата может содержать несколько триггеров. Поэтому под состоянием понимается сигнал, формируемый на выходе блока обратной связи. С учетом сказанного, обобщенную структурную схему конечного автомата можно представить в виде двух подсистем: комбинационной и триггерной или подсистемы памяти (рис. 2.5.5]. В отличие от ранее рассмотренной, приведенная структура предполагает наличие еще одного сигнала. Это сигнал синхронизации С, используемый для инициализации переключения элементов памяти (триггеров) подсистемы памяти. Таким образом, изменение выходного сигнала автомата Z [ m -1…0] возможно в двух случаях. При изменении входного сигнала

Граф переходов представляет графическую интерпретацию алгоритма работы цифрового автомата. Он наиболее удобен для начальной формализации алгоритма его работы. При построении графа переходов каждому состоянию автомата ставится в соответствие некоторая вершина графа, а переход из одного состояния в другое соответствует направленному ребру, соединяющему начальное и конечное состояния. Причем каждое ребро взвешено, т. е. над ним указывается дробь, числитель которой указывает значение входного сигнала, под действием которого осуществляется указанный переход, а знаменатель соответствует текущему значению выходного сигнала автомата Z [ m –1…0]. Таблица состояний включает G + 1 столбец и 2.5.5. Алгоритм синтеза цифрового автомата. 1. Исходя из условий функционирования, определяют число необходимых состояний и требуемый объем памяти цифрового автомата. Число необходимых для реализации состояний

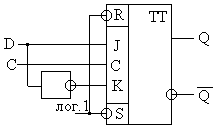

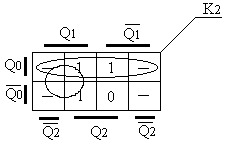

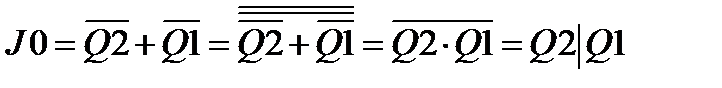

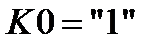

где функция CEIL означает округление до ближайшего большего целого. 2. Выполняют формальное описание алгоритма работы автомата; 3. Выбирают тип триггера для реализации подсистемы памяти. 4. Используя формальное описание алгоритма работы автомата и таблицу переходов выбранного типа триггеров, составляют расширенную таблицу истинности, характеризующую работу комбинационной подсистемы автомата. Число строк этой таблицы равно максимальному числу входных сигналов, действующих на входе комбинационной подсистемы. В столбцах таблицы записывается следующая информация: Х [ n -1…0] – входной сигнал, Sn [ q -1….0] – текущее состояние автомата, Sn +1[ q- 1…0] – последующее состояние автомата, Y [ k -1…0] – cигнал ПОС, Z [ m -1…0] – выходной сигнал автомата. 5. Используя расширенную таблицу истинности, минимизируют функции алгебры логики (ФАЛ), описывающие работу комбинационной подсистемы автомата; 6. Используя полученные ФАЛ, синтезируют схему цифрового автомата. Проиллюстрируем описание алгоритма работы автомата на примере. Пример 2.5.1. Спроектировать устройство, формирующее на выходе следующие последовательности выходных кодов: · при входном сигнале X = 1: 000, 001, 010, 100; · при входном сигнале Х = 0: 100, 010, 001, 000. Изменение входного сигнала должно приводить к изменению выходного кода в соответствие с заданными последовательностями сигналов. Причем это изменение должно происходить по фронту импульса внешнего сигнала синхронизации. 1. Из заданного алгоритма работы следует, что при одном значении входного сигнала Х на выходе автомата может формироваться 4 кода. Следовательно, число необходимых состояний автомата 2. Синтезируем граф переходов, описывающий заданный алгоритм работы устройства. Обозначим состояния автомата окружностями и обозначим их как S 0, S 1, S 2 и S 3 (рис. 2.5.6). Используя граф переходов, составим таблицу состояний автомата. В таблице состояний обозначено S 0 = 00, S 1 = 01, S 2 = 10, S 3 = 11 (табл. 2.5.1). 3. Для реализации триггерной подсистемы можно использовать любой тип синхронного триггера, изменяющего своё состояние по фронту импульса сигнала синхронизации. Используемый тип триггера определяет схему комбинационной подсистемы автомата. Можно сформулировать некоторые общие закономерности выбора типа используемого триггера. При выборе триггера, управляемого двумя информационными сигналами (RS- и JK- триггера) увеличивается разрядность сигнала ПОС, однако, как правило, упрощается схема комбинационной подсистемы.

4. Составим расширенную таблицу истинности (табл. 2.5.3). Т а б л и ц а 2.5.3. Расширенная таблица истинности заданного алгоритма устройства

Поясним составление расширенной таблицы истинности. В первых двух столбцах таблицы записаны все комбинации фактически возможных входных сигналов комбинационной подсистемы автомата. Это входные сигналы Х и сигналы Третий столбец таблицы содержит выходные сигналы (состояния) подсистемы памяти, которые должны формироваться после переключения триггеров:

Значения этих сигналов берутся либо из графа переходов автомата, либо из таблицы его состояний. Четвертый столбец содержит сигналы ПОС, которые должна формировать комбинационная подсистема для обеспечения заданного порядка переключения триггеров подсистемы памяти. Подсистема памяти в нашем случае состоит из двух Т -триггеров, поэтому сигнал Последний столбец таблицы 2.5.3 содержит значения выходных сигналов, которые, для известных

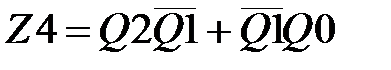

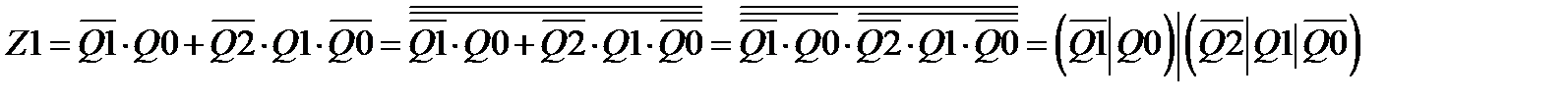

Используя полученные карты, запишем минимизированные ФАЛ для комбинационной подсистемы проектируемого устройства.

Преобразуем полученные выражения к базису элементов И-НЕ.

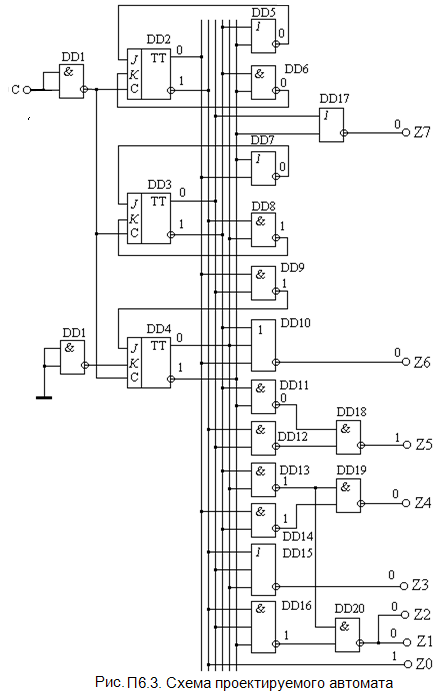

6. Используя полученные ФАЛ и выбранный тип триггеров для реализации блока памяти, синтезируем схему проектируемого устройства (рис. 2.5.8). На схеме автомата триггер DD1 формирует сигналы Элементы DD5, DD6 и DD13 формируют сигнал

Рис. 2.5.8. Схема синтезированного автомата

ПРИМЕР СИНТЕЗА ПОСЛЕДОВАТЕЛЬНОСТНОГО ЛОГИЧЕСКОГО УСТРОЙСТВА Рассмотрим пример синтеза последовательностного устройства, формирующего на выходе следующую последовательность кодов: 21, 97, 67, 21, 38, 96. 3.6.1. Определим необходимое число состояний и требуемый объем памяти автомата, формирующего на выходе заданную последовательность выходных кодов. Согласно заданию на выходе устройства должно быть сформировано 6 чисел. При этом число 21 повторяется 2 раза. Для автомата это два различных числа, так как после первого числа 21 идет число 97, а после второго – число 38. Поэтому на выходе формируется 6 различных чисел и 3.6.2. Для определения числа требуемых триггеров воспользуемся выражением:

Итак, для реализации подсистемы памяти необходимо 3 триггера. 3.6.3. Преобразуем заданные десятичные коды к виду двоично-десятичных кодов. Результаты преобразования сведены в таблицу 3.6. Таблица 3.6.1. Двоично-десятичное представление выходных кодов

П р и м е ч а н и е. В двоично-десятичном коде каждый разряд десятичного числа представляется четырехразрядным двоичным кодом, в котором используется только 10 первых значений. Коды с 10 по 15 не используются. Согласно полученной таблице для реализации заданной последовательности кодов необходимо использовать 8-разрядный код Z 7… Z 0.

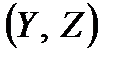

3.6.5. Синтезируем граф переходов проектируемого устройства. Отметим, что для работы устройства необходимо 6 состояний, в то время как при объеме памяти (3 триггера) возможно формирование 8 состояний. Следовательно, 2 возможных состояния являются лишними и необходимо обеспечить работоспособность устройства при появлении на выходе этих лишних состояний (аварийных режимов). Для этого надо предусмотреть принудительный выход из этих состояний. Допустим, что при попадании устройства в лишнее состояние автомат должен вернуться к началу последовательности, при этом на выходе должен сформироваться нулевой код. Отвечающий сказанному граф переходов показан на рис. 3.6.2. В этом графе, в виду отсутствия входного сигнала, в числителе дроби, записанной над ребром графа, стоит прочерк.

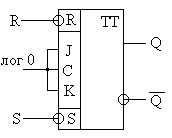

Рис. 3.6.2. Граф переходов проектируемого устройства Для реализации триггерной подсистемы выбираем JK -триггер. Запишем таблицу переходов триггера данного типа (табл. 3.6.2). Особенностью данной таблицы является наличие большого числа неопределенных сигналов, что, с большой степенью вероятности, позволит упростить реализацию комбинационной подсистемы автомата за счет получения не полностью определенной расширенной таблицы истинности. С выбором типа триггера заканчивается проектирование подсистемы памяти. Она состоит из 3-х JK -триггеров. Сигнал ПОС Y, соответствующий таблице переходов, является 6-разрядным: Таблица 3.6.2. Таблица переходов JK -триггера

3.6.6. Составим расширенную таблицу истинности, описывающую работу комбинационной подсистемы автомата (табл. 3.6.3). Для этого состояниям, указанным на графе переходам, присвоим следующие коды: S 0 = 000; S 1 = 001; S 2 = 010; S 3 = 011; S 4 = 100; S 5 = 101; S 6 = 110; S 7 = 111. Таблица 3.6.3. Расширенная таблица истинности комбинационной подсистемы автомата

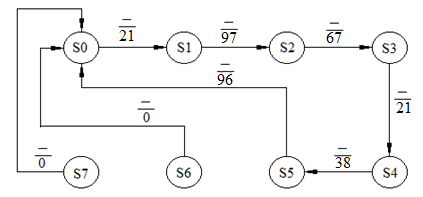

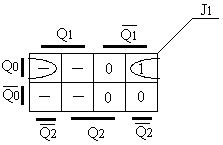

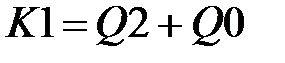

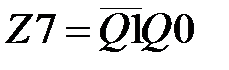

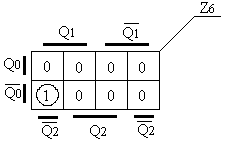

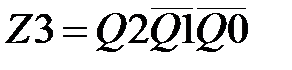

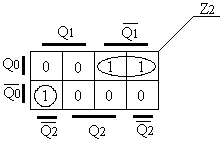

3.6.7. Минимизацию ФАЛ подсистемы выполнена с использованием карт Вейча (рис. 3.6.3).

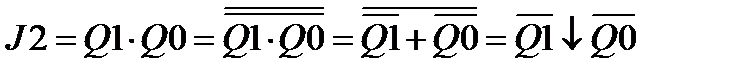

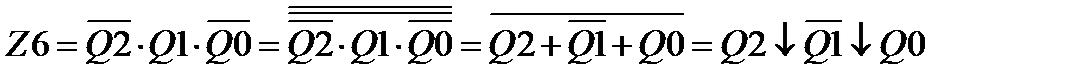

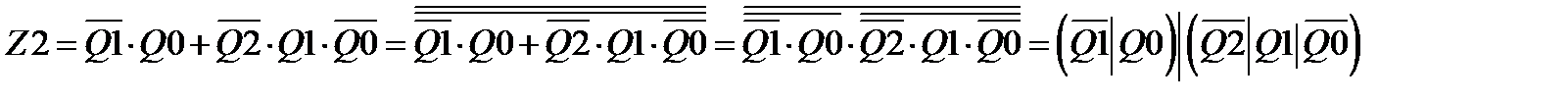

3.6.8. Приведем полученные выражения к базису элементов И-НЕ и ИЛИ-НЕ. При этом допустимое число входов элементов должно равняться 2, 3 или 4.

Основным критерием при выборе типа логического элемента было выбрано - получение наиболее простых выражений, что предполагает упрощение схемной реализации устройства. 3.6.9. Синтезированная по ФАЛ схема автомата, приведена на рис. 3.6.4. 3.6.10. Нарисуем временные диаграммы, поясняющие работу спроектированного устройства. Для этого на вход С подадим последовательность импульсов синхронизации, а на выходах триггеров подсистемы памяти зададим одно из возможных состояний S. В качестве примера, на рис. 3.6.4 на выходах триггеров задано исходное состояние автомата S = 000. Для этого случая на выходе комбинационной подсистемы формируются следующие сигналы: J 2= 0, K 2 = 0, J 1 = 0, K 1 = 1, J 0 = 1, K 0 = 1, Z = 00100001. Полученные сигналы подтверждают исходное задание, так как на выходе получено число 21, а следующим состоянием будет S = 001. При нахождении выходных сигналов комбинационной подсистемы удобно пользоваться введенным ранее для триггеров понятием активного логического уровня. Для элемента И-НЕ активным является сигнал «лог.0» так как появление на любом его входе этого сигнала выходной сигнал однозначно равен «лог.1». Для элемента ИЛИ-НЕ это сигнал «лог.1» формирующий на выходе сигнал «лог.0». Поэтому (см. рис. 3.6.4) нет необходимости искать сигнал на выходе элемента DD12, так как на выходе DD11 сформирован сигнал «лог.0» задающий на выходе элемента DD18 сигнал «лог.1». На рис. 3.6.5. приведены полученные таким образом временные диаграммы работы спроектированного автомата. Применение двухступенчатых триггеров привело к тому, что, фактически изменение выходного кода автомата происходит по срезу импульса синхронизации. Поэтому, для реализации переключения по фронту на входе устройства, сигнал синхронизации С необходимо инвертировать (см. элемент DD0, рис. 3.6.4).

СПИСОК ЛИТЕРАТУРЫ

1. Беневоленский С.Б., Марченко А.Л. Основы электротехники. Учебное пособие для втузов. – М.: Физматлит, 2007. – 568 с. 2. Марченко А.Л., Опадчий Ю.Ф.Электротехника и электроника. Учебник для вузов. В 2-х кн. Кн. 1. Электротехника. – М.: НИЦ Инфра-М, 2015. – 574 с. 3. Беневоленский С.Б., Марченко А.Л. Основы электротехники. Компакт-диск (660 Мб). – М.: Дискарт, 2007. 4. Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника (Полный курс): Учебник для вузов. Под ред. О.П. Глудкина. - М.: Голячая линия. Телеком, 2007. – 768 с. 5..Марченко А.Л. Основы электроники. Учебное пособие для вузов. – М.: ДМК Пресс. 2009. – 296 с. 6. Новожилов О.П. Основы цифровой техники. Учебное пособие. - М.: РадиоСофт, 2004. – 528 с.

ОГЛАВЛЕНИЕ

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-21; просмотров: 539; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.15 (0.018 с.) |

и при изменении состояния автомата S [ p -1…0], происходящего в момент переключения триггеров его подсистемы памяти. Последнее определяется сигналом синхронизации С.

и при изменении состояния автомата S [ p -1…0], происходящего в момент переключения триггеров его подсистемы памяти. Последнее определяется сигналом синхронизации С. строк, где G – число различных комбинаций входных сигналов Х [ n -1…0], которые могут присутствовать на входе автомата. В первом столбце перечисляются все возможные состояния автомата (состояния Sn). Остальные столбцы соответствуют возможным входным сигналам. На пересечении i -ой строки, соответствующей текущему состоянию автомата (соcтояние Si) и j -го столбца, соответствующего текущему значению входного сигнала (сигнал Х(j)) записывается дробь, числитель которой показывает следующее состояние автомата (Sn +1), а знаменатель – текущее значение выходного сигнала Z. Различные способы описания алгоритма работы автомата приведены в примере 2.5.1

строк, где G – число различных комбинаций входных сигналов Х [ n -1…0], которые могут присутствовать на входе автомата. В первом столбце перечисляются все возможные состояния автомата (состояния Sn). Остальные столбцы соответствуют возможным входным сигналам. На пересечении i -ой строки, соответствующей текущему состоянию автомата (соcтояние Si) и j -го столбца, соответствующего текущему значению входного сигнала (сигнал Х(j)) записывается дробь, числитель которой показывает следующее состояние автомата (Sn +1), а знаменатель – текущее значение выходного сигнала Z. Различные способы описания алгоритма работы автомата приведены в примере 2.5.1 определяется как наибольшее значение выходных кодов устройства, формируемых при одном значении входного сигнала. Объем памяти триггерной подсистемы

определяется как наибольшее значение выходных кодов устройства, формируемых при одном значении входного сигнала. Объем памяти триггерной подсистемы  определяется из условия, что n разрядный двоичный код может принимать

определяется из условия, что n разрядный двоичный код может принимать  различных значений. Тогда требуемый объем памяти, т.е. число необходимых триггеров подсистемы памяти, опделяется из условия:

различных значений. Тогда требуемый объем памяти, т.е. число необходимых триггеров подсистемы памяти, опделяется из условия:

. Для реализации такого числа состояний достаточно двух триггеров

. Для реализации такого числа состояний достаточно двух триггеров  .

.

, формируемые подсистемой памяти в данный момент времени. Очевидно, сигнал Sn определяется комбинацией выходных сигналов триггеров подсистемы памяти, т.е.

, формируемые подсистемой памяти в данный момент времени. Очевидно, сигнал Sn определяется комбинацией выходных сигналов триггеров подсистемы памяти, т.е.  , где

, где  и

и  - выходные сигналы триггеров под номерами 1 и 0.

- выходные сигналы триггеров под номерами 1 и 0. .

. - 2-разрядный код, где

- 2-разрядный код, где  и

и  соответственно информационные сигналы первого и нулевого триггеров подсистемы памяти. Значения этих сигналов можно получить из таблицы переходов выбранного типа триггера (см. табл. 2.5.2). Например, для первой строки расширенной таблицы истинности имеем

соответственно информационные сигналы первого и нулевого триггеров подсистемы памяти. Значения этих сигналов можно получить из таблицы переходов выбранного типа триггера (см. табл. 2.5.2). Например, для первой строки расширенной таблицы истинности имеем  и

и  т.е. оба триггера должны переключиться. Аализ таблицы 2.5.2 показывает, что для перехода триггера из сброшенного состояния

т.е. оба триггера должны переключиться. Аализ таблицы 2.5.2 показывает, что для перехода триггера из сброшенного состояния  в состояние установки

в состояние установки  на его информационный вход необходимо подать управляющий сигнал

на его информационный вход необходимо подать управляющий сигнал  . Поэтому сигнал (код) Y для этой строки равен 11.

. Поэтому сигнал (код) Y для этой строки равен 11. , выбираются либо из графа переходов, либо из расширенной таблицы истинности.

, выбираются либо из графа переходов, либо из расширенной таблицы истинности.

и выходных

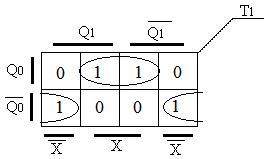

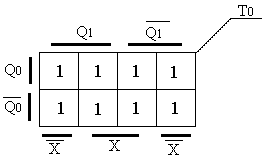

и выходных  сигналах подсистемы. Проведем минимизацию этих ФАЛ с использованием карт Вейча. На рис. 2.5.7 приведены соответствующие карты Вейча.

сигналах подсистемы. Проведем минимизацию этих ФАЛ с использованием карт Вейча. На рис. 2.5.7 приведены соответствующие карты Вейча. ,

,  ,

,  ,

,  ,

, .

. ,

,  ,

, ,

,  .

. и

и  . Триггер DD2 формирует сигналы

. Триггер DD2 формирует сигналы  и

и  . Для получения сигнала «лог. 1» используется логический элемент DD3 (2И-НЕ), на вход которого подаются два сигнала нулевого потенциала, который принято считать сигналом «лог. 0». Элемент DD4 используется как инвертор для формирования сигнала

. Для получения сигнала «лог. 1» используется логический элемент DD3 (2И-НЕ), на вход которого подаются два сигнала нулевого потенциала, который принято считать сигналом «лог. 0». Элемент DD4 используется как инвертор для формирования сигнала  .

. , управляющий работой триггера DD1. Элементы DD7…DD12 и DD14…DD16 формируют выходные сигналы Z автомата.

, управляющий работой триггера DD1. Элементы DD7…DD12 и DD14…DD16 формируют выходные сигналы Z автомата.

.

.

, по два управляющих сигнала на каждый триггер. Сигнал

, по два управляющих сигнала на каждый триггер. Сигнал  3-разрядный.

3-разрядный.

или

или

,

, ,

, ,

, ,

, ,

, ,

, ,

, ,

, ,

, ,

, ,

, ,

,  ,

, .

.