Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Анализ и синтез типовых электронных устройствСтр 1 из 8Следующая ⇒

Курсовая работа КР2 Задание 2.1 РАСЧЕТ И ПОСТРОЕНИЕ ЛОГАРИФМИЧЕСКОЙ АМПЛИТУДНО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ ПРЕОБРАЗОВАТЕЛЯ СИГНАЛОВ НА ОПЕРАЦИОННОМ УСИЛИТЕЛЕ

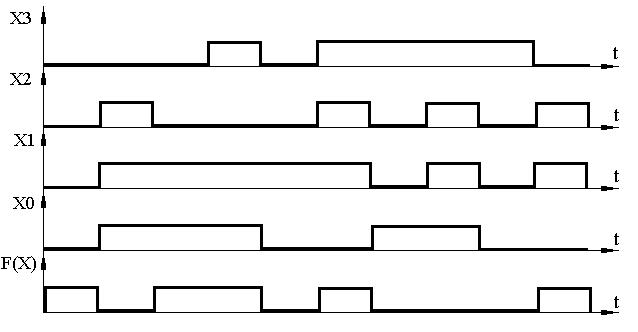

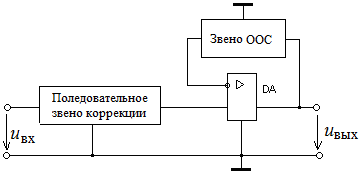

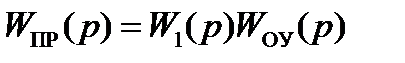

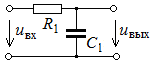

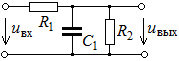

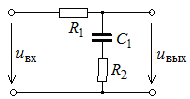

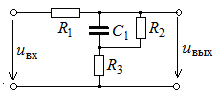

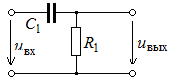

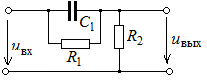

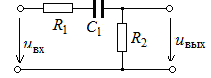

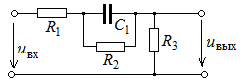

. Рис. 2.1. Обобщенная схема преобразователя аналоговых сигналов на основе операционного усилителя DA Для этого согласно варианту (см. табл. 2.1) необходимо: 2.1.1. Вычертить в соответствии с ГОСТ расчётную принципиальную электрическую схему преобразователя аналоговых сигналов, руководствуясь заданными в таблице 2.1 номерами Х = 1, 2, …, 8: последовательного звена коррекции ЭЦ-Х, звена ЭЦ-Х отрицательной обратной связи (ООС), их схемами, представленными в таблице 2.2, а также типом операционного усилителя ДА (табл. 2.4). 2.1.2. Пронумеровать сначала элементы последовательной цепи коррекции ЭЦ-Х, а затем – элементы цепи ЭЦ-Х ООС усилителя. Нумерацию элементов цепей выполнять слева направо (см. рис. 2.2.2). 2.1.3. Из таблицы 2.3 выписать заданные параметры звеньев преобразователя (выписываются параметры только тех элементов, которые присутствуют в полученной схеме замещения преобразователя), а из таблицы 2.4 – тип и коэффициент усиления К 0 используемого операционного усилителя ДА. 2.1.4. Записать в общем виде передаточную функцию преобразователя. 2.1.5. Получить передаточные функции 2.1.6. Получить передаточную функцию операционного усилителя 2.1.7. С учетом полученных передаточных функций звеньев записать передаточную функцию преобразователя 2.1.8. Вычислить численные значения параметров К и t, входящих в передаточную функцию преобразователя сигналов. 2.1.9. Вычислить частоты сопряжения асимптот ЛАЧХ (диаграммы Боде) анализируемого устройства и значения коэффициентов передачи для этих частот.

2.1.10. Используя полученные значения, построить диаграмму Боде преобразователя сигналов, определить его коэффициент передачи и полосу пропускания. 2.1.11. Сформулировать выводы по результатам выполненного задания. Т а б л и ц а 2.1. Варианты задания 2.1 курсовой работы КР2

Т а б л и ц а 2.2. Типовые звенья преобразователя

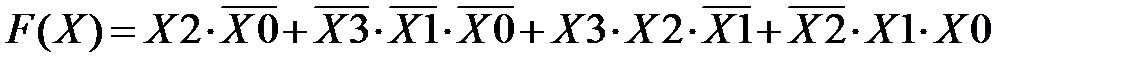

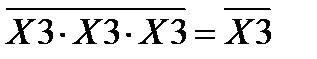

ПРИМЕР ПОСТРОЕНИЯ ЛАЧХ Выводы по заданию КР2-1 Исследуемый преобразователь аналоговых сигналов фактически является фильтром нижних частот, обеспечивающий передачу сигналов в диапазоне частот 0…w1, и ослабление сигналов на уровне -6,14 дБ в диапазоне частот w2…w3. После частоты w3 ЛАЧХ имеет постоянный наклон -20 дБ/дек. Задание 2.2 БАЗИСЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ По заданным параметрам синтезировать схему комбинационного устройства в заданном базисе логических элементов. Для этого согласно варианту (см. табл. 2.5 и табл. 2.6) необходимо: 2.2.1. По исходным данным составить таблицу истинности устройства. 2.2. Записать совершенную дизъюнктивную (СДНФ) и совершенную конъюнктивную (CКНФ) функции алгебры логики (ФАЛ), описывающие поведение устройства. 2.2.3. Минимизировать ФАЛ устройства. 2.2.4. Привести минимизированную ФАЛ к базису заданных логических элементов (см. табл. 2.7). 2.2.5. Синтезировать схему устройства в заданном базисе логических элементов. 2.2.6. Нарисовать временные диаграммы, поясняющие работу синтезированного устройства при подаче на его вход заданной последовательности проверочных входных кодов (см. табл. 2.8).

2.2.7. Сформулировать выводы по результатам выполненного задания. Т а б л и ц а 2.5. Варианты задания 2.2 курсовой работы КР2

ПРИМЕР СИНТЕЗА КОМБИНАЦИОННОГО ЛОГИЧЕСКОГО

УСТРОЙСТВА В БАЗИСЕ 3И-НЕ Рассмотрим выполнение задания со следующими параметрами: вар. 1 (табл. 2.6), вар. 3 (табл. 2.7), вар. 6 (табл. 2.8). Согласно заданию из таблиц 2.6, 2.7 и 2.8 выбираем: · последовательность конституент единицы: 0, 3, 4, 6, 11, 12, 13, 14; · базис логических элементов: 3И-НЕ; · последовательность проверочных кодов: 0, 7, 3, 11, 2, 14, 9, 15, 8, 6. 1. По заданным конституентам единицы составим таблицу истинности. Так как максимальная из заданных конституент равна 14, то для отображения входного кода проектируемого устройства достаточно четырех входных переменных (четырехразрядного входного кода). Т а б л и ц а 2.4.1. Таблица истинности работы устройства

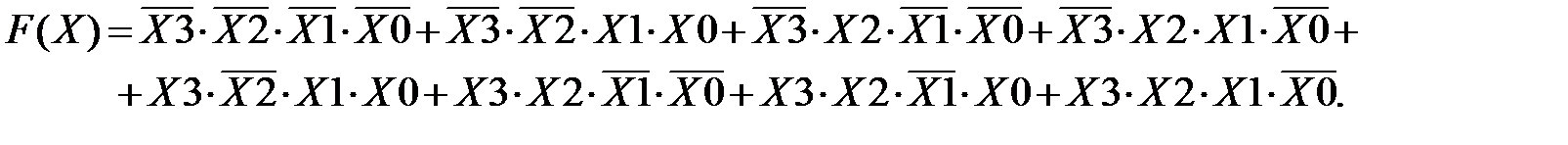

2. Используя составленную таблицу истинности, запишем СДНФ и CКНФ синтезируемого устройства. СДНФ:

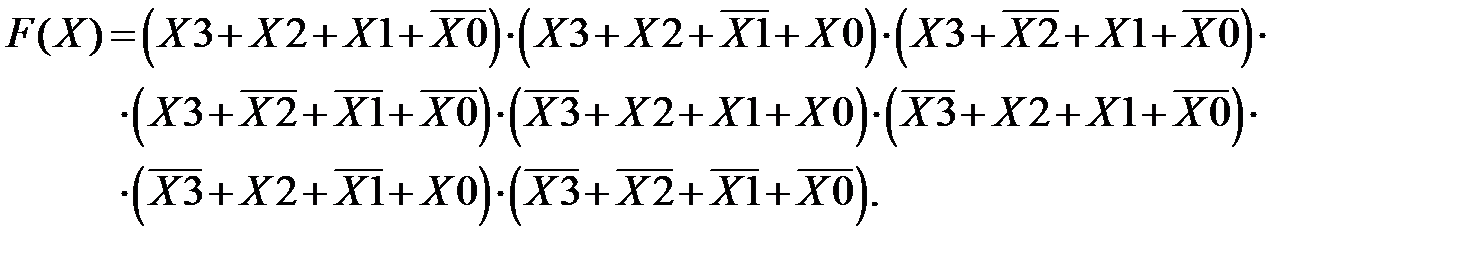

СКНФ:

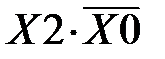

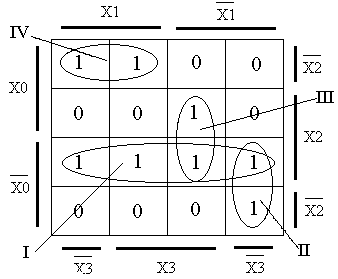

3. Минимальную дизъюнктивную форму ФАЛ получим с использованием карты Вейча. На карте Вейча (см. рис. 2.4.1) можно выделить 4 области, охватывающие все единичные значения функции. Первая область состоит из четырех элементов, описываемая произведением неизменных переменных Вторая область – из двух элементов, описываемая произведением неизменных переменных

Третья область – из двух элементов, описываемая произведением неизменных переменных Четвертая область – из двух элементов, описываемая произведением неизменных переменных Окончательно получим минимизированную ФАЛ вида

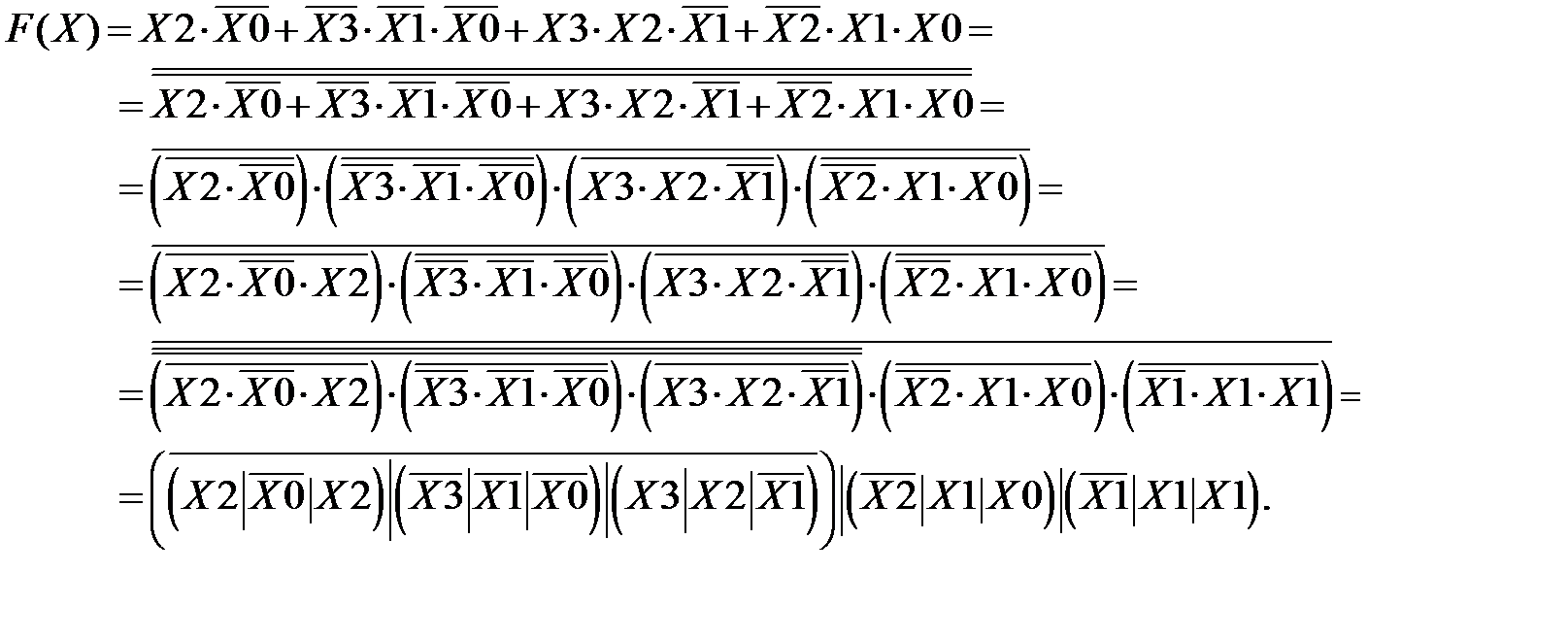

4. Приведем полученную ФАЛ к базису элементов 3И-НЕ

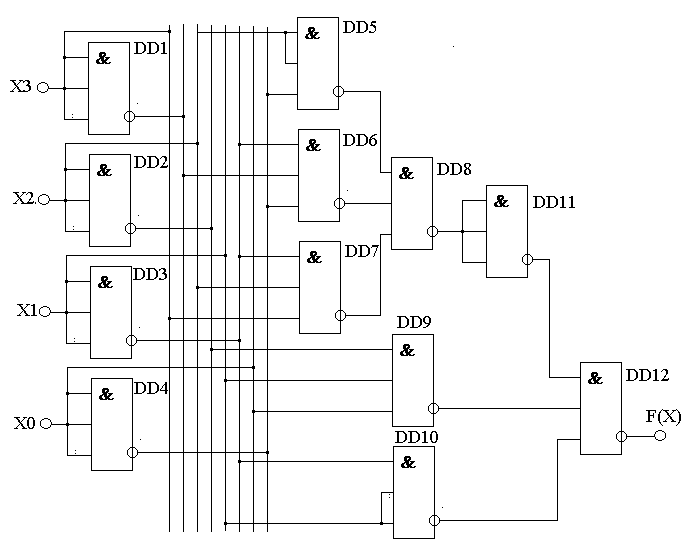

Следует отметить, что последний член выражения 5. По полученному выражению синтезируем схему логического устройства в заданном базисе 3И-НЕ (рис. 2.4.2). Для этого элементы, реализующие операцию функции Шеффера, располагают от входа к выходу согласно их месту в ФАЛ.

Для получения сигналов, инверсных входным ( 6. Для получения временных диаграмм коды, заданные в таблице 7.8, последовательно подаются на входы спроектированного устройства и прослеживается сигнал, проходящий по всем элементам схемы. Эту проверку можно выполнить либо вручную, подставляя значения заданных переменных на входы устройства, либо с помощью соответствующего программного обеспечения, например, программы Multisim, использующейся при выполнении лабораторных работ. На рис. 2.4.3. приведены полученные в результате проверки временные диаграммы, поясняющие работу спроектированного устройства. Выводы по заданию 3.2 7. Выводы по заданию 2 должны содержать основные результаты, полученные при выполнении работы. Например: «В результате выполнения работы получены ФАЛ, формально описывающие заданный алгоритм функционирования устройства. Выполнена минимизация СДНФ, в результате которой найдена минимальная дизъюнктивная формы (МДФ) записи ФАЛ. Минимизация выполнена с использованием карт Вейча. МДНФ ФАЛ приведена к виду, предполагающему ее реализацию

на элементах 3И-НЕ. Синтезирована схема устройства в заданном базисе логических элементов, и, с использованием заданных проверочных кодов, проверена правильность ее функционирования. Результат проверки свидетельствует, что функционирование разработанной схемы соответствует исходному заданию».

Задание 2.3 ЦИФРОВОГО УСТРОЙСТВА), РЕАЛИЗУЮЩЕГО ЗАДАННЫЙ АЛГОРИТМ ФУНКЦИОНИРОВАНИЯ По известным параметрам синтезировать схему последовательностного устройства, формирующего на выходе заданную последовательность двоично-десятичных кодов. Для этого согласно варианту (см. табл. 2.9) необходимо: 2.3.1. Определить число необходимых состояний и объем памяти цифрового автомата. 2.3.2. Преобразовать заданную последовательность выходных чисел к виду двоично-десятичного кода. 2.3.3. Определить разрядность выходного кода устройства. 2.3.4. Нарисовать обобщенную структурную схему проектируемого устройства. 2.3.5. Составить граф переходов цифрового автомата. 2.3.6. Выбрать тип триггера для реализации триггерной подсистемы цифрового автомата и записать его таблицу переходов. 2.3.7. Составить расширенную таблицу истинности, описывающую поведение проектируемого цифрового автомата. 2.3.8. Записать минимизированные ФАЛ, описывающие алгоритм работы комбинационной подсистемы устройства. 2.3.9. Привести полученные ФАЛ к стандартному базису логических элементов. 2.3.10. Составить схему цифрового автомата. 2.3.11. Нарисовать временные диаграммы, поясняющие работу разработанного устройства. 3.12. Сформулировать выводы по работе. Т а б л и ц а 7.9. Варианты задания 2.3 курсовой работы КР2

ЦИФРОВЫХ УСТРОЙСТВ 2.5.1 Основные определения. Последовательностными устройствами или автоматами с памятью называют логические устройства, выходной сигнал которых определяется не только действующей в настоящий момент на входе комбинацией переменных, но и всей последовательностью входных и выходных переменных, действовавших в предыдущие моменты времени. Реализация такого алгоритма работы предполагает, что на входе некоторого логического устройства действует не только комбинация внешних входных сигналов, но и некоторые сигналы, отображающие предысторию работы устройства. Такие сигналы могут вырабатываться в самом комбинационном устройстве и совместно с внешними подаваться на его вход. Очевидно, что, по сути, в последовательностном устройстве существует канал передачи информации с его выхода на вход, причем эта информация суммируется с внешней. Следовательно, такой канал передачи является цепью положительной обратной связи (ПОС), охватывающей исходное комбинационное устройство. На рис. 2.5.1 приведена обобщенная структурная схема, реализующая описанный алгоритм работы устройства.

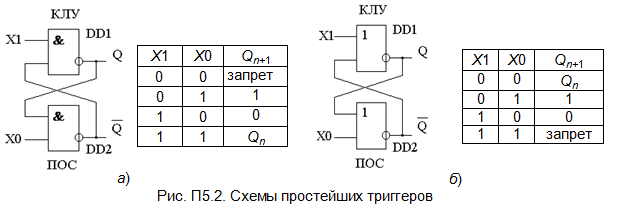

Представленная на рис. 2.5.1 структура является конечным автоматом, известным как автомат Мили. Если в схеме отсутствует входной сигнал X [ n -1…0], то получим структуру, известную как автомат Мура. В зависимости от выполнения блока ПОС, данная структура порождает два класса устройств. Если в качестве блока обратной связи используется комбинационное устройство, получаем класс устройств называемых триггерами. Эти устройства являются элементарными ячейками памяти, способными хранить один бит информации. Если блок обратной связи сам выполнен как последовательностное устройство, например триггер, то получаем более сложное устройство, которое и является конечным автоматом. Рассмотрим особенности работы обоих классов последовательностных устройств. 2.5.2. Триггеры. Триггером называется устройство, способное формировать два устойчивых значения выходного сигнала и скачкообразно изменять эти значения под действием внешнего управляющего сигнала. Простейший триггер может быть построен, если в качестве комбинационного логического устройства использовать простейший элемент 2И-НЕ или 2ИЛИ-НЕ. Так как эти элементы содержат инвертор, то для формирования сигнала ПОС выходной сигнал элемента необходимо дополнительно инвертировать. С этой целью можно использовать второй такой же элемент. На рис. 2.5.2 приведены два варианта построения простейшего триггера. Он снабжен двумя информационными входами

Из таблиц следует, что существует три разновидности комбинаций входных сигналов Х 1 и Х 0. Первая - это комбинация при которой значение выходного сигнала остается неизменным. Вторая – комбинация, которая однозначно определяет выходной сигнал устройства. И третья - это запрещенная комбинация, при которой не выполняется определение триггера (сигнал  ), т.е. устройство теряет способность хранить информацию, так как после снятия этой комбинации значение выходного сигнала невозможно прогнозировать. ), т.е. устройство теряет способность хранить информацию, так как после снятия этой комбинации значение выходного сигнала невозможно прогнозировать.

Реальные схемы триггеров содержат одну или несколько из приведенных ячеек памяти и некоторую комбинационную схему, предназначенную для формирования информационных сигналов Х 1 и Х 0.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-21; просмотров: 325; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.189.180.76 (0.062 с.) |

последовательного звена коррекции и звена цепи ООС

последовательного звена коррекции и звена цепи ООС  преобразователя.

преобразователя. с заданным звеном в цепи ООС усилителя.

с заданным звеном в цепи ООС усилителя. . Полученную передаточную функцию преобразовать к виду, содержащему стандартные сомножители из перечисленных: К, t р,1/(t p), t р + 1, 1/(t р + 1), где К =

. Полученную передаточную функцию преобразовать к виду, содержащему стандартные сомножители из перечисленных: К, t р,1/(t p), t р + 1, 1/(t р + 1), где К =  - постоянный коэффициент, t - постоянная времени звена, р – оператор Лапласа. Значения К и t определяются параметрами элементов звеньев, входящих в заданное устройство.

- постоянный коэффициент, t - постоянная времени звена, р – оператор Лапласа. Значения К и t определяются параметрами элементов звеньев, входящих в заданное устройство.

.

. .

. Рис. 2.4.1. Карта Вейча для заданного алгоритма

Рис. 2.4.1. Карта Вейча для заданного алгоритма

.

. .

. .

.

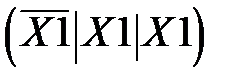

моделирует формирование логической константы, равной логической единицы (при любых значениях Х 1 данное выражение равно «лог.1»). Возможны и другие способы задания логической константы. Например заданием на всех входах элемента 3И-НЕ логического нуля:

моделирует формирование логической константы, равной логической единицы (при любых значениях Х 1 данное выражение равно «лог.1»). Возможны и другие способы задания логической константы. Например заданием на всех входах элемента 3И-НЕ логического нуля:  .

. ,

,  ,

,  ,

,  ), на входе устройства используются дополнительные элементы DD1…DD4, выполняющие роль инверторов. Например, выходной сигнал элемента DD1 определяется выражением

), на входе устройства используются дополнительные элементы DD1…DD4, выполняющие роль инверторов. Например, выходной сигнал элемента DD1 определяется выражением  , т.е. элемент выполняет функцию инвертора.

, т.е. элемент выполняет функцию инвертора. и

и  и двумя выходами

и двумя выходами  и

и  , сигналы которых связанны операцией инверсии. Рядом со схемами приведены таблицы истинности, поясняющие работу этих устройств. В таблицах под Qn понимается исходное значение выходного сигнала триггера, а под Qn +1 - значение выходного сигнала после воздействия входных переменных.

, сигналы которых связанны операцией инверсии. Рядом со схемами приведены таблицы истинности, поясняющие работу этих устройств. В таблицах под Qn понимается исходное значение выходного сигнала триггера, а под Qn +1 - значение выходного сигнала после воздействия входных переменных.