Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Вопрос 2. Триггеры. Счетчики. Регистры.

Триггер представляет собой устройство с двумя устойчивыми состояниями. Устойчивым называется состояние, в котором устройство в отсутствии внешних воздействий может прибывать сколь угодно долго. В общем случае триггер имеет два выхода: прямой и инверсный. Состояние триггера принято определять по значению потенциала на прямом выходе. Если на прямом выходе имеется В основу классификации триггеров положены два основных признака: функциональный и способ записи информации в триггер. Функциональная классификация является наиболее общей и представляет собой классификацию триггеров по виду логического уравнения, характеризующего состояния входов и выходов триггера в момент времени до его срабатывания Классификация по способу записи информации характеризует временную диаграмму работы триггера, т.е. определяет ход процесса записи информации в триггер. По этой классификации триггеры подразделяются на асинхронные и тактируемые. Отличительной особенностью асинхронных триггеров является то, что запись информации в них осуществляется непосредственно с поступлением информационного сигнала на его вход. Запись информации в тактируемый триггер, имеющий информационные и тактовые входы, осуществляется только при подаче разрешающего или тактирующего импульса. Среди тактируемых триггеров различают триггеры, срабатывающие по уровню (в момент прихода тактирующего сигнала или, что одно и то же, по его переднему фронту), и триггеры с внутренней задержкой, срабатывающие после окончания тактирующего сигнала (по заднему фронту). Такое управление тактируемыми триггерами называется динамическим. Кроме того, тактируемые триггеры подразделяются на однотактные и многотактные в зависимости от числа тактирующих сигналов, необходимых для перевода триггера из одного состояния в другое. При проектировании устройств с применением триггеров кроме значения функции, выполняемой триггером, необходимо знать его основные схемотехнические параметры:

· минимальная длительность входного сигнала – определяет минимально допустимую длительность входного сигнала, при которой еще происходит переключение триггера из одного состояния в другое. · максимальная частота переключения триггера определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности. Закон функционирования триггера удобно отображать с помощью, так называемых таблиц переходов, в которых даются состояния входов и выходов триггера в момент времени до его срабатывания 0 – триггер находится в состоянии 1 – триггер находится в состоянии

Перейдем к рассмотрению триггеров различных типов. RS-триггер. Триггером RS -типа является логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при Вход S называется единичным, а R – нулевым. Принцип работы RS -триггера можно задать таблицей переходов (таблице 18.1), где Таблица 18.1

Для того чтобы найти логическое уравнение RS -триггера, преобразуем таблицу переходов к виду, в котором состояние Таблица 18.2

Логическое уравнение RS -триггера: Полученное уравнение задает работу асинхронного RS -триггера. Состояние такого триггера определяется только значениями сигналов

Для реализации триггера на элементах ИЛИ – НЕ проведем отрицание обеих частей полученного уравнения

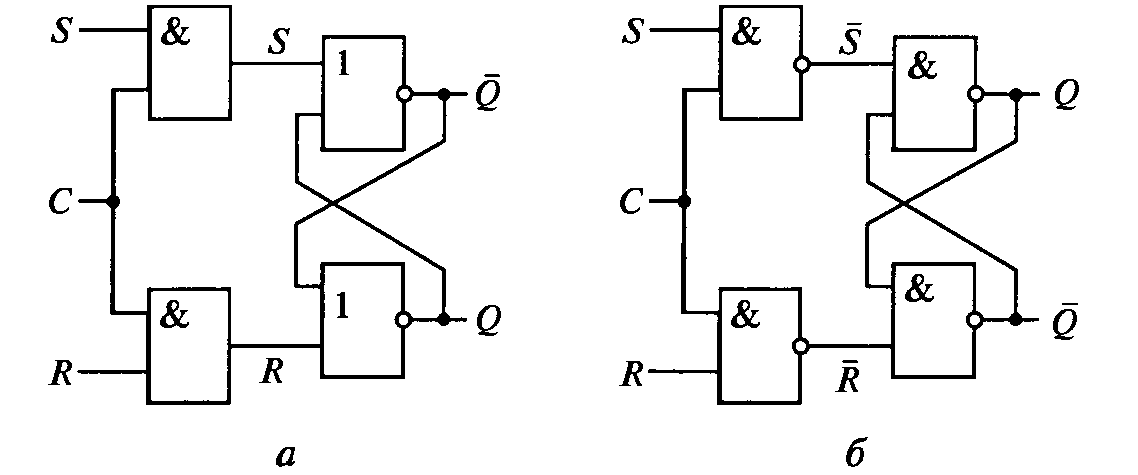

Таким образом, сигнал на инвертирующем выходе RS -триггера – это сигнал на выходе элемента ИЛИ-НЕ, на один вход которого подан сигнал S, а на второй – сигнал с выхода другого элемента ИЛИ-НЕ (рисунок 18.2 а).

Рисунок 18.2 – Асинхронный RS -триггер: а – структурная схема на базе элементов ИЛИ-НЕ; б – структурная схема на базе элементов И-НЕ; в – условное графическое обозначение. Из рисунка 18.2 в видно, что на вход триггера на элементах И-НЕ сигналы R и S необходимо подавать в инверсном виде. В качестве самостоятельных устройств асинхронные RS -триггеры находят ограниченное применение, но являются базовыми схемами для более сложных триггерных устройств. В устройствах цифровой обработки находят применение тактируемые RS -триггеры, которые называются еще синхронными. Эти триггеры кроме входов установки R и S имеют вход разрешения записи C. Срабатывание синхронного триггера происходит только при наличии активного сигнала на этом входе. Структурные схемы синхронных RS-триггеров приведены на рисунке 18.3. Часто синхронные триггеры любых типов имеют дополнительные входы асинхронной установки в нуль или единицу.

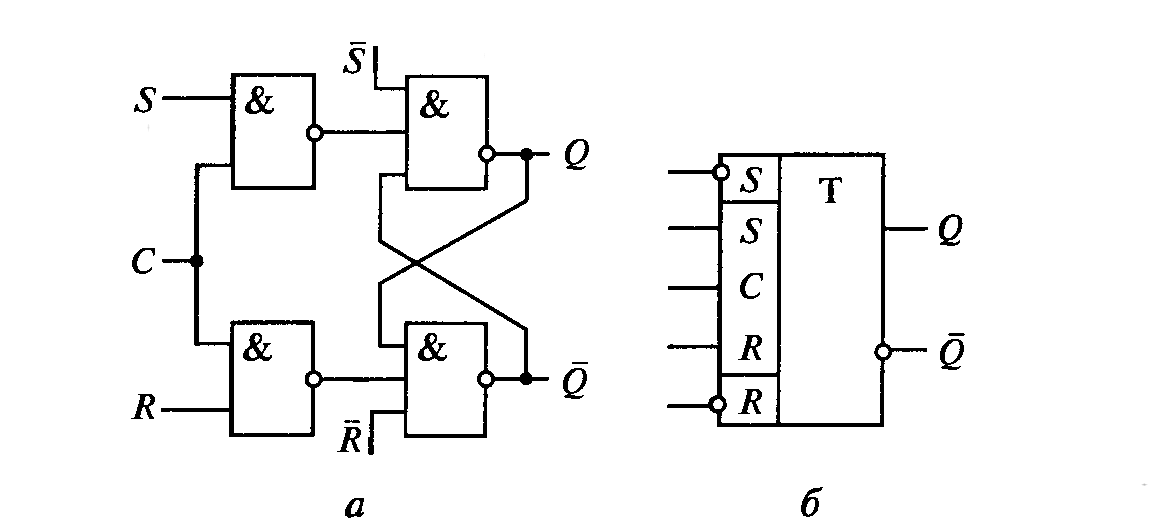

Рисунок 18.3 – Варианты структурных схем синхронных RS -триггеров: а – на элементах ИЛИ-НЕ; б – на элементах И-НЕ Структурная схема такого синхронного RS -триггера приведена на рисунке 18.4 а,а его условное графическое обозначение – на рисунке 18.4 б.

Рисунок 18.4 – Структурная схема синхронного RS -триггера с входами асинхронной установки (а) и его условное графическое обозначение (б) Поскольку триггер, изображенный на структурной схеме, реализован на элементах И-НЕ, то сигналы асинхронной установки R и S должны иметь инверсные активные уровни. Поскольку сигналы асинхронной установки подаются непосредственно на выходной каскад (асинхронный RS -триггер), то они имеют больший приоритет перед остальными сигналами триггера. D-триггер относится к одновходовым триггерам. Асинхронный D -триггер имеет один вход D, прямой и инверсный выходы Таблица 18.3

Структурная схема синхронного D -триггера и его УГО представлены на рисунке 18.5.

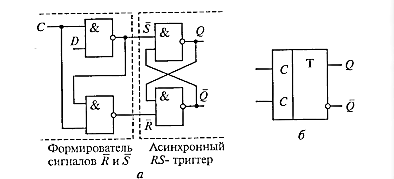

Рисунок 18.5 – Структурная схема синхронного D -триггера на элементах И-НЕ (а) и его УГО (б) Синхронный D -триггер осуществляет запись информационного разряда по активному уровню сигнала С с последующим его хранением, поэтому синхронный D -триггер имеет другое название: триггер-защелка. D -триггер на базе элементов И-НЕ представлен совокупностью двух каскадов. Первый выполняет функцию формирования сигналов S и R, а второй – асинхронного RS- триггера.

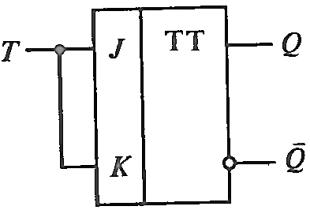

Т-триггер является одновходовым устройством с двумя устойчивыми состояниями, изменяющимися каждый раз на противоположные при подаче на вход Т управляющего сигнала. Характерной его особенностью является то, что частота изменения потенциала на его выходах в два раза меньше частоты сигналов на входе T (рисунок 18.6).

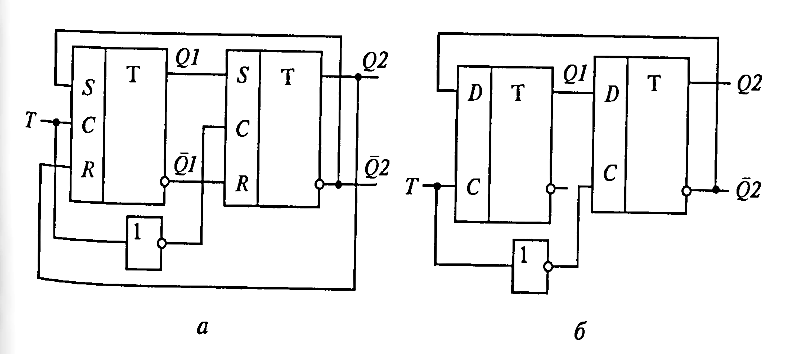

Рисунок 18.6 – Диаграммы входного и выходного потенциалов T -триггера Это свойство используется при построении двоичных счетчиков. Отсюда второе название T -триггера – счетный триггер. Для устойчивой работы T -триггера необходимо разделить во времени функции приема тактирующего сигнала T и фиксации на входах R, S или D сигналов с соответствующих выходов Пример двухступенчатого Т -триггера на базе двух синхронных RS -триггеров приведен на рисунке 18.7 а, а на базе двух синхронных D -триггеров – на рисунке 18.7 б.

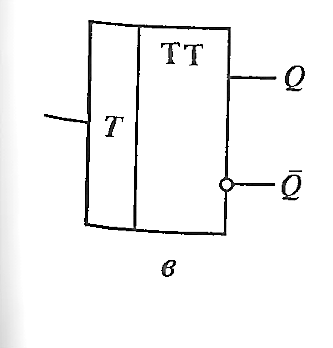

Рисунок 18.7 – Двухступенчатый T -триггер на базе синхронных RS -триггеров (а) и синхронных D -триггеров (б) его УГО (в) Из рисунка 18.7 видно, что, когда на синхронизирующем входе первого триггера в двухступенчатой структуре действует нулевой уровень тактирующего сигнала Т, он хранит свое состояние

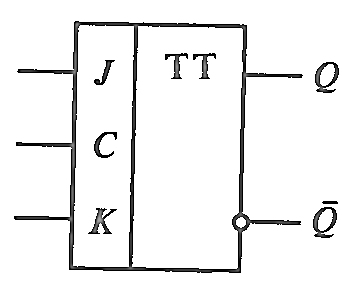

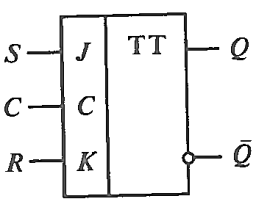

JK-триггер. JK -триггер относится к двухвходовым устройствам и функционирует по правилам, похожим на правила функционирования RS -триггера. Отличие состоит в том, что в JK -триггере все состояния являются определенными. Можно провести аналогию входов JK - и RS -триггеров: вход K JK -триггера выполняет функцию входа R RS -триггера, а вход J JK -триггера – функцию входа S RS -триггера. При этом, если в RS -триггере комбинация единичных значений входов R и S является запрещенной, в случае аналогичной комбинации J - и K -входов JK -триггер меняет свое состояние на противоположное. Условное графическое обозначение синхронного двухступенчатого JK -триггера приведено на рисунке 18.8

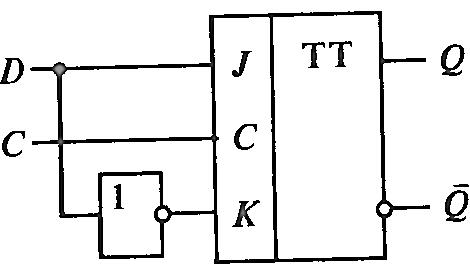

Рисунке 18.8 – УГО синхронного двухступенчатого JK -триггера Триггер JK -типа относится к разряду универсальных, поскольку на его основе можно получить схемы, выполняющие функции RS-, D- и Т -триггеров (рисунок 18.9).

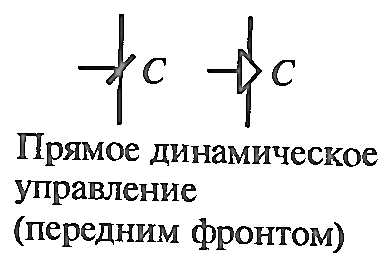

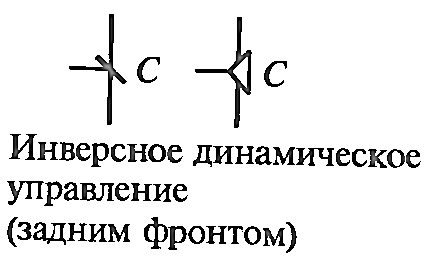

а б в г Рисунок 18.9 – Реализация триггеров различных типов на базе JK- триггера: а – RS -триггера; б – D- триггера; в, г – Т -триггера Рассмотренные ранее способы подачи входных сигналов характеризуются тем, что их активными уровнями являются статические состояния, т.е. сами уровни напряжения логического нуля или логической единицы. Такая форма управления цифровым устройством называется статической. Для тактируемых устройств эта форма управления большинстве случаев является неудобной, поскольку в течение всего времени действия импульса сигнала синхронизации устройство будет реагировать на любые изменения входных информационных сигналов. Таким образом, необходимо, чтобы информационные сигналы оставались неизменными на протяжении действия импульса синхронизации. Это значительно усложняет схему устройства, а в некоторых случаях и вовсе является не решаемой задачей, поскольку информационные сигналы могут носить характер случайной последовательности импульсов. Для устранения указанного недостатка используется принцип динамического управления. Согласно этому принципу активным считается не статический уровень напряжения логической единицы или логического нуля, а процесс перехода из одного уровня в другой. Этот процесс представляет собой передний или задний фронт тактирующего импульса и, следовательно, характеризуется малым временным промежутком. Поэтому задача синхронизации значительно упрощается и представляет собой фиксацию входных информационных сигналов в строго определенный момент подачи или снятия импульса синхронизации. На рисунке 18.10 показаны условные обозначения входов микросхем с динамическим управлением. В качестве сигнала выбран управляющий сигнал синхронизации С.

а б Рисунок 18.10 – Обозначение входов динамического управления: а – прямое динамическое управление или управление передним фронтом; б – инверсное динамическое управление или управление задним фронтом Счетчики. Счетчики представляют собой последовательностные цифровые устройства и предназначены для выполнения операций счета и хранения кода числа подсчитанных импульсов. Существуют различные схемы счетчиков, отличающихся назначением, типом используемых триггеров, организацией связи между ними, порядком смены состояний. По порядку изменения состояний счетчики бывают с естественным и произвольным порядком счета. В первых значение кода каждого последующего состояния счетчика отличается на единицу от кода предыдущего состояния. В счетчиках с произвольным порядком счета значения кодов соседних состояний могут отличаться более чем на единицу. Счетчики также подразделяются на простые и реверсивные. Простые счетчики подразделяют на суммирующие и вычитающие. В суммирующих счетчиках код последующего состояния имеет большее значение, чем код предыдущего состояния, а в вычитающих – меньшее значение. Реверсивные счетчики могут работать как в режиме суммирования, так и в режиме вычитания.

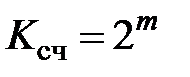

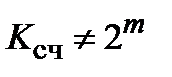

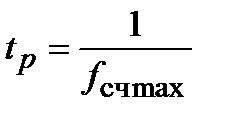

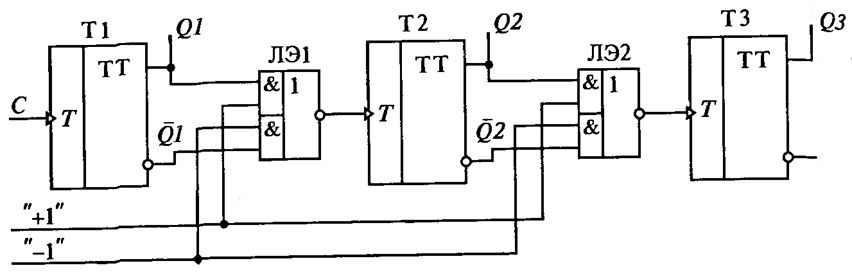

Основными параметрами счетчика являются: модуль счета, или коэффициент пересчета Модуль счета Быстродействие счетчика, в свою очередь, определяется двумя величинами: разрешающей способностью Поскольку счетчики представляют собой класс ПЦУ, то и синтез их целесообразно выполнять на основе базовых элементов ПЦУ, т.е. триггерах. Двоичные счетчики. Для их построения можно использовать различные типы триггеров. Наиболее удобным является триггер Т -типа (счетный триггер), который осуществляет подсчет импульсов по модулю 2. Такой триггер, по сути, является простейшим счетчиком с Структурная схема трехразрядного двоичного реверсивного счетчика приведена на рисунке 18.11. Элементы ЛЭ1 и ЛЭ2 выполняют роль коммутаторов выходных сигналов с триггеров

Рисунок 18.11 – Структурная схема трехразрядного двоичного реверсивного счетчика Таким образом, осуществляется инверсия сигналов В приведенном счетчике срабатывание триггеров последовательно. Такие счетчики называются асинхронными. Их недостаток состоит в том, что увеличивается общее время установления На рисунке 18.12 приведена структурная схема четырехразрядного суммирующего счетчика с параллельным переносом.

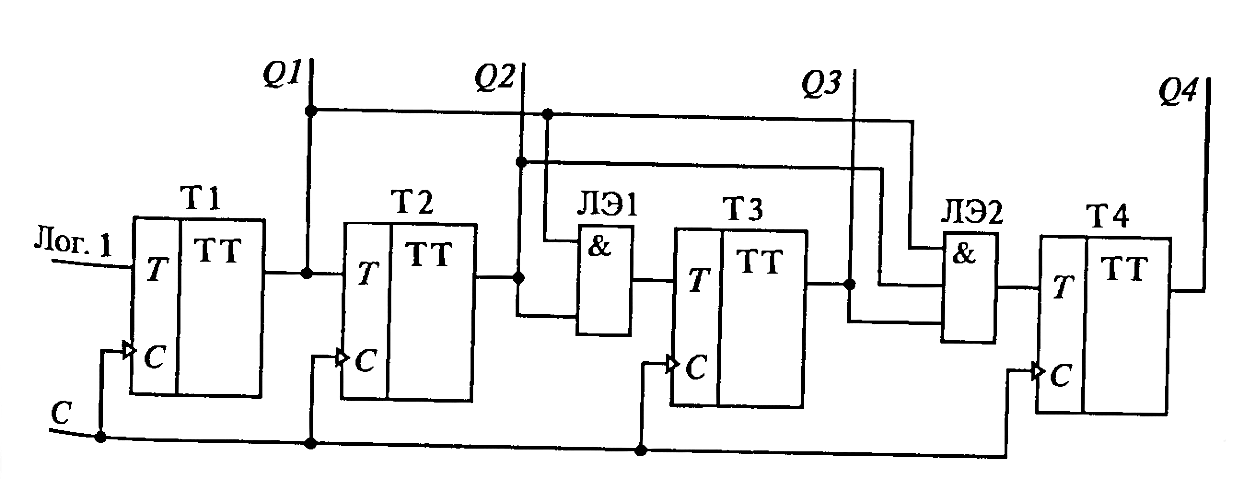

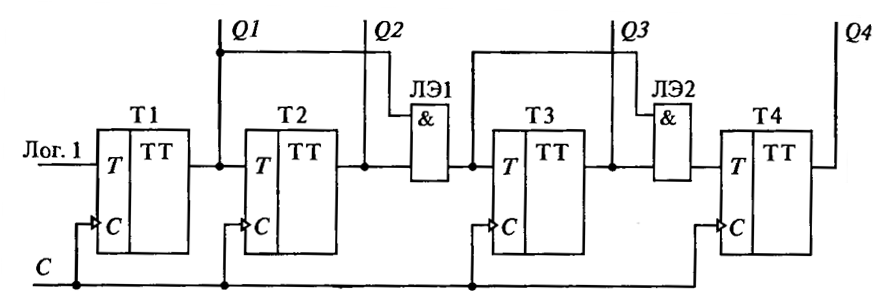

Рисунок 18.12 – Структурная схема четырехразрядного суммирующего счетчика с параллельным переносом Срабатывание всех триггеров происходит одновременно по общему сигналу синхронизации Чтобы синтезировать схему вычитающего счетчика, необходимо использовать не прямые, а инверсные выходы триггеров. Таким образом, в исходном состоянии все триггеры будут иметь на инверсных выходах логические единицы. С началом счета выходные коды будут уменьшаться (декрементироваться). Используя принцип коммутации прямых или инверсных выходов триггеров, можно также реализовать реверсивный счетчик с параллельным переносом. Недостатком счетчиков с параллельным переносом является необходимость использования в случае увеличения разрядности счетчика элементов И с большим числом входов. При этом выходы триггеров должны обладать высокой нагрузочной способностью. Поэтому многоразрядные счетчики строят по групповому принципу. Согласно этому принципу весь счетчик структурно реализуется путем соединения отдельных групп небольшой разрядности с параллельным переносом внутри этих групп. Сигнал переноса из очередной группы формируется элементом И, объединяющим выходы всех триггеров данной группы. Сформированный сигнал переноса предыдущей группы подается на счетный вход последующей группы. Общая задержка такого счетчика определяется суммой задержек каждой группы. Другой вариант структуры синхронного счетчика – это структура со сквозным переносом. Согласно этой структуре перенос формируется только из единичных результатов соседних разрядов. Для этих целей достаточно использовать только двухвходовые элементы И при любой разрядности счетчика (рисунок 18.13).

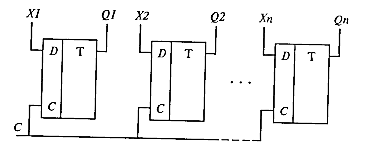

Рисунок 18.13 – Структурная схема четырехразрядного суммирующего счетчика со сквозным переносом Перенос между разрядами осуществляется через каждый элемент И (ЛЭ1 и ЛЭ2) в их последовательной структуре. Отсюда следует, что общее время срабатывания всего счетчика определяется временем срабатывания одного триггера и суммарным временем задержки последовательной цепи логических элементов И. Выигрыш по быстродействию в такой структуре осуществляется за счет меньшего времени срабатывания одного логического элемента по сравнению со временем срабатывания одного триггера. При достаточно большой разрядности счетчика время задержки во всех элементах И может оказаться значительным и сравняться с временем срабатывания одного триггера. Недвоичные счетчики. Недвоичные счетчики имеют Регистры. Регистрами называются последовательностные цифровые устройства, выполняющие функции приема, хранения и передачи информации. Информация в регистре хранится в виде двоичного кода. Каждому разряду кода, записанному в регистр, соответствует свой разряд регистра, как правило, на основе триггеров RS-, D- или JK- типа. Основным классификационным признаком, по которому различают регистры, является способ записи информации или кода числа в регистр. По этому признаку можно выделить регистры следующих типов: параллельные; последовательные; последовательно-параллельные. По способу представления вводимой информации различают регистры однофазного и парафазного типа. В однофазных регистрах информация вводится по одному каналу (прямому или инверсному). Информация на выходе представлена в прямом или в обратном коде. В парафазных регистрах ввод информации осуществляется по двум каналам одновременно (прямому и инверсному), т.е. информация представлена одновременно в прямом и обратном кодах. Информация на выходе, как правило, также представляется в прямом и инверсном кодах. Параллельные регистры. Параллельный регистр используется для кратковременного хранения чисел, представленных в параллельном двоичном коде. Поэтому параллельные регистры называются еще регистрами памяти. Время ввода числа в регистр параллельного типа равно времени ввода одного разряда. Рассмотрим способы построения регистров памяти на При реализации регистров на основе RS -триггеров требуется подача разрядов исходного числа в прямом и инверсном коде либо предварительное обнуление всех триггеров, что не всегда является удобным. В этом отношении удобны регистры на

Рисунок 18.14 – Структурная схема параллельного регистра на Последовательные регистр предназначен для кратковременного хранения информации, но в отличие от параллельного регистра в нем осуществляется логическая операция сдвига кода хранимого числа на любое число разрядов. Время ввода числа в регистр последовательного типа равно

Рисунок 18.15 – Структурная схема последовательного регистра Из рисунка 18.15 видно, что информация с первым тактирующим импульсом с входа V передается на выход первого и вход второго триггеров. С приходом второго тактирующего импульса информация из первого триггера перепишется на выход второго триггера. На выход первого триггера запишется новое значение с входа Для построения последовательного реверсивного регистра, в котором код числа может сдвигаться как влево, так и вправо, необходимо между триггерами регистра включить устройства управления направлением сдвига. Эти устройства в зависимости от значения управляющих сигналов «сдвиг вправо» и «сдвиг влево» должны переключать входы каждого триггера регистра либо к выходам предыдущего, либо к выходам последующего триггера. Последовательные регистры находят ограниченное применение. Последовательно-параллельные регистры. Эти регистры получили широкое распространение. На их базе строятся преобразователи кодов из последовательного в параллельный и из параллельного в последовательный. Для реализации параллельного вывода информации в последовательном регистре достаточно использовать выходы

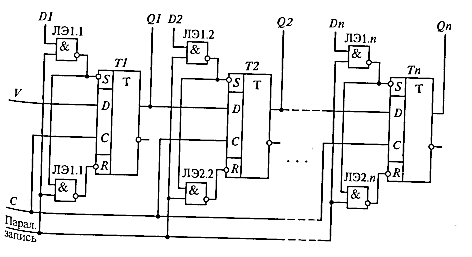

Рисунок 18.16 – Структурная схема последовательно-параллельного регистра Как и в последовательном регистре, ввод информации в последовательном коде осуществляется по входу V. Для тактирования сдвига синхровходы всех триггеров объединены. При этом для возможности введения кода числа в параллельном виде используются элементы И-НЕ Если выход последнего триггера соединить с входом первого, то получится кольцевой регистр сдвига. Записанная в его разряды информация под воздействием сдвигающих импульсов будет циркулировать по замкнутому кольцу. Кольцевой регистр иначе называется кольцевым счетчиком. Его коэффициент пересчета равен числу разрядов

Контрольные вопросы 1 Поясните принципы организации ПЦУ. 2 В чем состоит отличие синхронного 3 В каких типовых ПЦУ используются в качестве элементной базы 4 Что такое входы асинхронной установки в нуль и единицу? 5 Приведите схемы реализации триггеров

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 1451; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.139.238.76 (0.085 с.) |

потенциал, равный логической единице, то триггер находится в единичном состоянии. В противном случае триггер находится в нулевом состоянии.

потенциал, равный логической единице, то триггер находится в единичном состоянии. В противном случае триггер находится в нулевом состоянии. и после

и после  . В соответствии с функциональной классификацией различают RS -, D -, T -, JK - триггеры.

. В соответствии с функциональной классификацией различают RS -, D -, T -, JK - триггеры. и после

и после  ,при этом выходное состояние может обозначаться следующим образом:

,при этом выходное состояние может обозначаться следующим образом: ;

; ;

; – состояние триггера не изменяется при изменении информации на входе;

– состояние триггера не изменяется при изменении информации на входе; – состояние триггера изменяется на противоположное при изменении информации на входе;

– состояние триггера изменяется на противоположное при изменении информации на входе; – неопределенное состояние триггера характеризуется тем, что в процессе действия информационного сигнала на входе логические уровни выходов триггера одинаковы (

– неопределенное состояние триггера характеризуется тем, что в процессе действия информационного сигнала на входе логические уровни выходов триггера одинаковы ( или

или  ) а после окончания действия информационного сигнала триггер может оказаться в состояние

) а после окончания действия информационного сигнала триггер может оказаться в состояние  или

или  с равной вероятностью.

с равной вероятностью. и

и  триггер принимает единичное состояние

триггер принимает единичное состояние  , а при

, а при  и

и  – нулевое

– нулевое  .

. – исходное состояние триггера.

– исходное состояние триггера.

определим конкретными значениями и представим его в виде входной переменной (табл. 18.2).

определим конкретными значениями и представим его в виде входной переменной (табл. 18.2).

.

. и

и  . Асинхронный RS -триггер можно построить на логических элементах И-НЕ, ИЛИ-НЕ. Преобразуем логическое уравнение асинхронного-триггера, используя законы отрицания алгебры логики:

. Асинхронный RS -триггер можно построить на логических элементах И-НЕ, ИЛИ-НЕ. Преобразуем логическое уравнение асинхронного-триггера, используя законы отрицания алгебры логики:

.

.

и

и  . Асинхронный D -триггер – триггер задержки не имеет практического применения, поскольку его функцию может выполнять схема из последовательного соединения двух инверторов. Наибольший интерес представляет тактируемый (синхронный) D -триггер, работа которого описывается таблицей переходов (таблица 18.3):

. Асинхронный D -триггер – триггер задержки не имеет практического применения, поскольку его функцию может выполнять схема из последовательного соединения двух инверторов. Наибольший интерес представляет тактируемый (синхронный) D -триггер, работа которого описывается таблицей переходов (таблица 18.3):

и

и  . Для этого в структуру T -триггера вводится дополнительный второй запоминающий элемент на базе RS- или D -триггера. На синхронизирующий вход этого элемента тактовый сигнал подается в инверсном виде по отношению к тактовому сигналу первого запоминающего элемента. Подобная организация структур триггерных устройств называется двухступенчатой.

. Для этого в структуру T -триггера вводится дополнительный второй запоминающий элемент на базе RS- или D -триггера. На синхронизирующий вход этого элемента тактовый сигнал подается в инверсном виде по отношению к тактовому сигналу первого запоминающего элемента. Подобная организация структур триггерных устройств называется двухступенчатой.

, и

, и  . В это время на синхронизирующий вход второго триггера поступает инвертированный сигнал Т, т.е. имеющий уровень логической единицы. В результате второй триггер принимает состояние первого, т.е.

. В это время на синхронизирующий вход второго триггера поступает инвертированный сигнал Т, т.е. имеющий уровень логической единицы. В результате второй триггер принимает состояние первого, т.е.  и

и  . Запись в первый триггер при этом запрещена. Как только тактирующий сигнал Т примет уровень логической единицы, произойдет запись информации из второго триггера в первый. В результате состояние первого триггера изменится на противоположное. При этом запись во второй триггер производиться не будет, поскольку на его входе будет действовать нулевой уровень сигнала разрешения записи. Процесс будет повторяться с приходом каждого тактирующего импульса, что обеспечит устойчивую работу устройства. В условных графических обозначениях всех двухступенчатых триггеров принято в обозначении функции элемента указывать два символа «ТТ». Вход Т Т -триггера принято называть счетным.

. Запись в первый триггер при этом запрещена. Как только тактирующий сигнал Т примет уровень логической единицы, произойдет запись информации из второго триггера в первый. В результате состояние первого триггера изменится на противоположное. При этом запись во второй триггер производиться не будет, поскольку на его входе будет действовать нулевой уровень сигнала разрешения записи. Процесс будет повторяться с приходом каждого тактирующего импульса, что обеспечит устойчивую работу устройства. В условных графических обозначениях всех двухступенчатых триггеров принято в обозначении функции элемента указывать два символа «ТТ». Вход Т Т -триггера принято называть счетным.

; быстродействие счетчика.

; быстродействие счетчика. характеризует число устойчивых состояний счетчика, т.е. предельное число импульсов, которое может быть им сосчитано. После поступления

характеризует число устойчивых состояний счетчика, т.е. предельное число импульсов, которое может быть им сосчитано. После поступления  , и недвоичные, у которых

, и недвоичные, у которых  , где m – положительное целое число.

, где m – положительное целое число. т.е. минимальным допустимым интервалом времени между подачей двух входных импульсов, при котором не происходит потеря счета; временем установки

т.е. минимальным допустимым интервалом времени между подачей двух входных импульсов, при котором не происходит потеря счета; временем установки  кода счетчика, т.е. интервалом времени между моментом поступления входного сигнала и моментом завершения перехода счетчика в новое устойчивое состояние. При этом должно выполняться условие

кода счетчика, т.е. интервалом времени между моментом поступления входного сигнала и моментом завершения перехода счетчика в новое устойчивое состояние. При этом должно выполняться условие  .

. . Соединив несколько счетных триггеров определенным образом, можно получить схему многоразрядного счетчика.

. Соединив несколько счетных триггеров определенным образом, можно получить схему многоразрядного счетчика. и

и  .При подаче логического нуля на вход «-1» и логической единицы на вход «+1» на выходе верхней структуры И элементов ЛЭ1 и ЛЭ2 формируется результат с выходов

.При подаче логического нуля на вход «-1» и логической единицы на вход «+1» на выходе верхней структуры И элементов ЛЭ1 и ЛЭ2 формируется результат с выходов  и

и  соответствующих триггеров. На выходе нижней структуры И присутствует логический нуль, в результате чего выходы

соответствующих триггеров. На выходе нижней структуры И присутствует логический нуль, в результате чего выходы  и

и  не влияют на работу схемы. Структура ИЛИ–НЕ элементов ЛЭ1 и ЛЭ2 инвертирует значения соответствующих коммутируемых выходов.

не влияют на работу схемы. Структура ИЛИ–НЕ элементов ЛЭ1 и ЛЭ2 инвертирует значения соответствующих коммутируемых выходов.

и

и  , которые подаются на прямые динамические тактовые входы триггеров

, которые подаются на прямые динамические тактовые входы триггеров  и

и  . Счетчик работает в режиме суммирования. При подаче логического нуля на вход «+1» и логической единицы на вход «-1» режим работы меняется. На практике для упрощения процесса управления обычно вместо двух входов «+1» и «-1» используется только один из этих входов. Сигнал второго входа формируется через инвертор.

. Счетчик работает в режиме суммирования. При подаче логического нуля на вход «+1» и логической единицы на вход «-1» режим работы меняется. На практике для упрощения процесса управления обычно вместо двух входов «+1» и «-1» используется только один из этих входов. Сигнал второго входа формируется через инвертор. с увеличением числа триггеров. Для устранения этого недостатка используются счетчики, у которых все триггеры срабатывают одновременно. Такие счетчики получили название синхронных счетчиков. Идея синхронного счетчика заключается в построении внешней комбинационной схемы, формирующейсигналы, согласно которым будет происходить одновременное переключение только части триггеров в зависимости от текущего выходного кода. Причем эти сигналы должны быть сформированы до поступления очередного счетного импульса. Счетный импульс должен поступать на все триггеры одновременно. Для этих целейнеобходимо использовать тактируемые Т -триггеры, входы, синхронизации которых объединяются в общую шину. На тактовые Т -входы каждого триггера подаются заранее сформированные сигналы переноса с комбинационной схемы.

с увеличением числа триггеров. Для устранения этого недостатка используются счетчики, у которых все триггеры срабатывают одновременно. Такие счетчики получили название синхронных счетчиков. Идея синхронного счетчика заключается в построении внешней комбинационной схемы, формирующейсигналы, согласно которым будет происходить одновременное переключение только части триггеров в зависимости от текущего выходного кода. Причем эти сигналы должны быть сформированы до поступления очередного счетного импульса. Счетный импульс должен поступать на все триггеры одновременно. Для этих целейнеобходимо использовать тактируемые Т -триггеры, входы, синхронизации которых объединяются в общую шину. На тактовые Т -входы каждого триггера подаются заранее сформированные сигналы переноса с комбинационной схемы.

, который является счетным импульсом для всего счетчика. В исходном состоянии на выходах всех триггеров присутствуют логические нули. С поступлением каждого счетного импульса выходные коды начинают увеличиваться на единицу (инкрементироваться). Задержка в такой схеме равна времени срабатывания одного триггера.

, который является счетным импульсом для всего счетчика. В исходном состоянии на выходах всех триггеров присутствуют логические нули. С поступлением каждого счетного импульса выходные коды начинают увеличиваться на единицу (инкрементироваться). Задержка в такой схеме равна времени срабатывания одного триггера.

. Принцип их построения заключается в исключении некоторых устойчивых состояний обычного двоичного счетчика. Наибольший интерес среди недвоичных счетчиков представляют двоично-десятичные счетчики, с

. Принцип их построения заключается в исключении некоторых устойчивых состояний обычного двоичного счетчика. Наибольший интерес среди недвоичных счетчиков представляют двоично-десятичные счетчики, с  , которые строятся на основе четырех счетных триггеров. Важность этого класса счетчиков заключается в том, что с их помощью легко может быть осуществлен вывод содержимого счетчика в десятичном коде. Действительно каждый двоично-десятичный счетчик имеет десять устойчивых состояний и соответствует одному разряду десятичной системы счисления.

, которые строятся на основе четырех счетных триггеров. Важность этого класса счетчиков заключается в том, что с их помощью легко может быть осуществлен вывод содержимого счетчика в десятичном коде. Действительно каждый двоично-десятичный счетчик имеет десять устойчивых состояний и соответствует одному разряду десятичной системы счисления. -триггерах. Каждый триггер служит для хранения одного разряда числа, значит, для хранения

-триггерах. Каждый триггер служит для хранения одного разряда числа, значит, для хранения  – разрядного двоичного числа необходимо иметь

– разрядного двоичного числа необходимо иметь

-триггеров. Полученный регистр будет парафазным, причем вход

-триггеров. Полученный регистр будет парафазным, причем вход  – прямой, а вход

– прямой, а вход  – инверсный.

– инверсный. -триггерах. В них информация может быть установлена по одному входу и без предварительной установки в нуль (рисунок 18.14).

-триггерах. В них информация может быть установлена по одному входу и без предварительной установки в нуль (рисунок 18.14).

– триггерах

– триггерах , где

, где  – число разрядов вводимого числа, а

– число разрядов вводимого числа, а  – период следования тактирующих сигналов, осуществляющих ввод (вывод) информации. Ввод информации в последовательный регистр осуществляется по одному последовательному каналу

– период следования тактирующих сигналов, осуществляющих ввод (вывод) информации. Ввод информации в последовательный регистр осуществляется по одному последовательному каналу  . Сдвиг кода числа происходит с помощью синхронизирующих импульсов

. Сдвиг кода числа происходит с помощью синхронизирующих импульсов  , в результате подачи которых осуществляется сдвиг всех разрядов кода числа со входа к выходу или наоборот. Как и в случае параллельных регистров, последовательный регистр может быть синтезирован на базе триггеров RS -типа ( JK – типа), но наиболее удобным для этих целей является использование

, в результате подачи которых осуществляется сдвиг всех разрядов кода числа со входа к выходу или наоборот. Как и в случае параллельных регистров, последовательный регистр может быть синтезирован на базе триггеров RS -типа ( JK – типа), но наиболее удобным для этих целей является использование  -триггеров (рисунок 18.15).

-триггеров (рисунок 18.15).

. Таким образом, будет осуществляться сдвиг исходного кода вправо. Отсюда последовательные регистры называются еще регистрами сдвига. Информация выводится из триггера по одному выходу

. Таким образом, будет осуществляться сдвиг исходного кода вправо. Отсюда последовательные регистры называются еще регистрами сдвига. Информация выводится из триггера по одному выходу  .

. , всех триггеров. Чтобы реализовать ввод информации как в последовательном, так и в параллельном виде, можно использовать

, всех триггеров. Чтобы реализовать ввод информации как в последовательном, так и в параллельном виде, можно использовать  -триггеры с асинхронной установкой в нуль или единицу. Пример такой структуры приведен на рисунке 18.16.

-триггеры с асинхронной установкой в нуль или единицу. Пример такой структуры приведен на рисунке 18.16.

, и

, и  , в своих разрядах. Элемент

, в своих разрядах. Элемент  , осуществляет функцию стробирования и инвертирования разряда

, осуществляет функцию стробирования и инвертирования разряда  , при единичном уровне управляющего сигнала «параллельная запись». В результате на вход S установки в единицу триггера

, при единичном уровне управляющего сигнала «параллельная запись». В результате на вход S установки в единицу триггера  , проходит инверсное значение разряда

, проходит инверсное значение разряда  , параллельного кода числа только в том случае, если сигнал разрешения на линии «параллельная запись» имеет единичное значение. Элемент

, параллельного кода числа только в том случае, если сигнал разрешения на линии «параллельная запись» имеет единичное значение. Элемент  , выполняет функцию инвертирования сигнала с элемента

, выполняет функцию инвертирования сигнала с элемента  , и передачи его на вход

, и передачи его на вход  сброса триггера

сброса триггера  , также по активному уровню сигнала разрешения параллельной записи. В результате парафазный код всех разрядов параллельного кода проходит на соответствующий триггер только при активном уровне сигнала разрешения параллельной записи. Поскольку элементы

, также по активному уровню сигнала разрешения параллельной записи. В результате парафазный код всех разрядов параллельного кода проходит на соответствующий триггер только при активном уровне сигнала разрешения параллельной записи. Поскольку элементы  , имеют инверсные выходы, то триггеры

, имеют инверсные выходы, то триггеры  , должны иметь инверсные входы

, должны иметь инверсные входы  и

и  .

. последовательного кода. Единица, записанная в один из разрядов, периодически будет появляется в нем после того, как будут поданы

последовательного кода. Единица, записанная в один из разрядов, периодически будет появляется в нем после того, как будут поданы  сдвигающих импульсов.

сдвигающих импульсов. -триггера от синхронного

-триггера от синхронного  -триггера?

-триггера? - и

- и  - триггеры?

- триггеры? -,

-,  - и

- и  - типов на базе синхронных

- типов на базе синхронных  -триггеров.

-триггеров.