Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Сумматоры. Дешифраторы и шифраторы. Мультиплексоры и демультиплексоры. Цифровые компараторы.

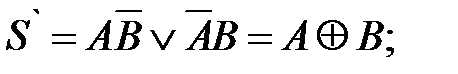

Сумматоры – это класс КЦУ, выполняющих операцию арифметического сложения двух двоичных n – разрядных чисел. Сумматоры бывают неполными и полными. Неполный сумматор (полусумматор) – представляет собой комбинационное устройство с двумя входами и двумя выходами, выполняющее операцию сложения двух одноразрядных чисел в соответствии с таблицей истинности (таблица 17.1), где А и В – входные одноразрядные числа; S ` – выход суммы; Р ` – выход переноса в старший разряд. Таблица 17.1

Записанные по таблице истинности ФАЛ для переменных S ` и Р ` имеют вид Первое уравнение для S ` обозначает операцию исключающее ИЛИ (сложение по модулю два), а второе уравнение для P ` – операцию логической конъюнкции. Поскольку во всех сериях микросхем имеются элементы Исключающие ИЛИ, то структурную схему полусумматора удобно синтезировать на основе именно этого элемента и элемента И (рисунок 17.2 а). Условное графическое обозначение полусумматора приведено на рисунке 17.2 б. Полный одноразрядный сумматор выполняет операцию арифметического сложения двух одноразрядных чисел А и В с учетом переноса из младшего разряда

а б Рисунок 17.2 – Структурная схема (а) и УГО (б) полусумматора

Таблица 17.2

Структура полного одноразрядного сумматора представлена на рисунке 17.3 а, а его УГО – на рисунке 17.3 б.

а б Рисунок 17.3 – Структурная схема (а) и УГО (б) полного однозарядного сумматора При суммировании многоразрядных двоичных чисел с помощью одноразрядных сумматоров их необходимо соединить в последовательные структуры. Выходы переноса Р микросхем младших разрядов подключаются к входам переноса

При необходимости реализации быстродействующих сумматоров для сложения двоичных чисел большей разрядности используют два подхода. Первый заключается в использовании полных сумматоров с параллельным переносом и в объединении их в общую последовательную структуру. Сумматоры, реализованные по такой структуре, называются сумматорами с цепным переносом. Второй подход также основан на использовании набора сумматоров с параллельным переносом. Но их объединение в общую структуру основано на принципе параллельной передачи переноса. В этом случае требуется дополнительная комбинационная схема, реализующая параллельный перенос между параллельными сумматорами. Сумматоры с такой структурой называются параллельно-параллельными. Они имеют максимальное быстродействие, но их реализация требует дополнительных аппаратных затрат. Дешифратор – это устройство, предназначенное для преобразования двоичного кода в напряжение логической единицы (логического нуля) на том выходе, номер которого совпадает со значением двоичного кода на входе. При п входах в полном дешифраторе имеется Таблица 17.3

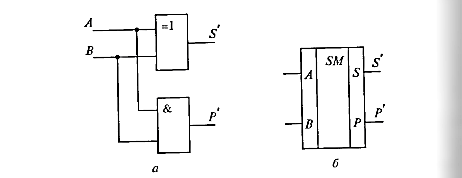

Соответствующие таблице истинности ФАЛ имеют вид

Структурная схема трехразрядного дешифратора, синтезированная на основании полученных ФАЛ, приведена на рисунке 17.4 а, а его УГО – на рисунке 17.4 б.

а б Рисунок 17.4 – Структурная схема (а)и УГО (б) трехзарядного дешифратора Построенные по полученным формулам дешифраторы называются линейными. К преимуществу линейных дешифраторов можно отнести высокое быстродействие, поскольку входные переменные одновременно поступают на все элементы И. Одновременно без дополнительных задержек формируется и результат на выходах этих элементов. Очевидно, что для реализации линейного дешифратора n- разрядного числа необходимо иметь Указанного недостатка лишены пирамидальные дешифраторы. Принцип построения этих дешифраторов состоит в том, что сначала строят линейный дешифратор для двухразрядного числа X1, X2, для чего необходимы Характерным отличием пирамидальных дешифраторов от линейных является использование только двухвходовых логических элементов вне зависимости от разрядности дешифрируемого числа. Шифраторы выполняют задачу обратную той, которую выполняют дешифраторы: появление логической единицы (логического нуля) на определенном входе приводит к появлению соответствующей кодовой комбинации на выходе. Так же, как и дешифраторы, шифраторы бывают полными и неполными. Структурная схема шифратора представлена на рисунке 17.5 а, а его УГО – на рисунке 17.5 б.

а б Рисунок 17.5 – Структурная схема (а) и УГО (б) восьмивходового шифратора Мультиплексор – комбинационное цифровое устройство, которое обеспечивает передачу на единственный выход F одного из нескольких входных сигналов

Таблица 17.4

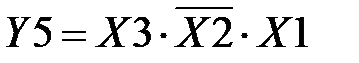

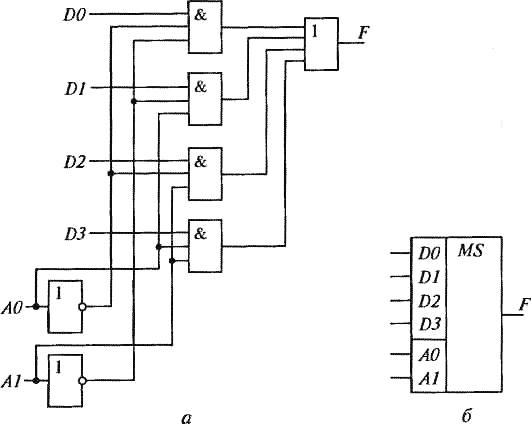

Логическое выражение для выходной функции, заданной таблице 17.4 можно записать в виде

В соответствии с полученной формулой для реализации мультиплексора можно использовать логические элементы И, ИЛИ, НЕ. Синтезированная структурная схема мультиплексора показала на рисунке 17.6 а, а его УГО – на рисунке 17.6 б.

а б Рисунок 17.6 – Структурная схема (а) и УГО (б) мультиплексора «из 4 в 1» Мультиплексирование при большом числе входов можно выполнить пирамидальным каскадированием мультиплексоров. Мультиплексор можно реализовать, используя дешифратор и схемы И и ИЛИ (рисунок 17.7).

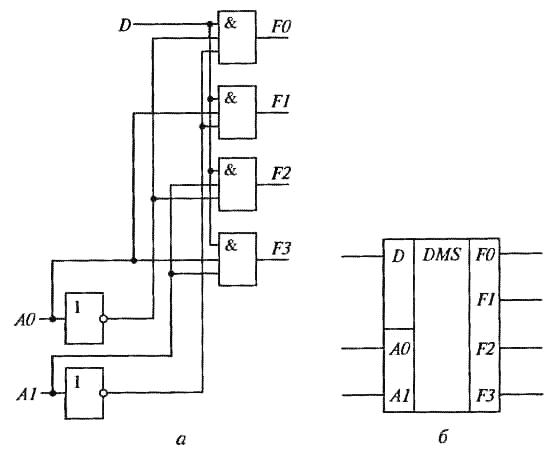

Рисунок 17.7 – Реализация мультиплексора на базе дешифратора Демультиплексор выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Структурная схема, реализующая демультиплексор «из 1 в 4», приведена на рисунке 17.8 а, а его УГО – на рисунке 17.8 б.

а б Рисунок 17.8 – Структурная схема (а) и УГО (б) демультиплексора «из 1 в 4» Как и в случае мультиплексора, схему демультиплексора можно реализовать с помощью дешифратора (рисунок 17.9). Мультиплексоры и демультиплексоры часто называют еще цифровыми коммутаторами.

Рисунок 17.9 – Реализация демультиплексора на базе дешифратора Цифровой компаратор предназначен для сравнения двух п- разрядных двоичных чисел Структурная схема компаратора двух четырехразрядных чисел представлена на рисунке 17.10.

Рисунок 17.10 – Структурная схема компаратора двух четырехразрядных чисел Выпускаемые промышленностью цифровые компараторы устанавливают обычно не просто факт равенства или неравенства чисел А и В, но и определяют большее из них, т.е. устанавливают следующие соотношения чисел А и В:

Контрольные вопросы 1 Как можно увеличить число входов при использовании микросхем базовых логических элементов И-НЕ и ИЛИ-НЕ, число входов которых недостаточно?

2 Что такое высокоимпедансное состояние? 3 Перечислите основные этапы синтеза КЦУ. 4 Изобразите схему последовательного четырехразрядного двоичного сумматора, используя одноразрядные полные сумматоры с прямыми входами А и В, прямым входом переноса 5 В чем заключается особенность построения параллельных сумматоров? 6 Каковы преимущества и недостатки линейного и пирамидального дешифраторов? 7 Составьте таблицу истинности и структурную схему для четырехвходового шифратора. 8 Как реализовать схемы мультиплексора «из 8 в 1» и демультиплексора «из 1 в 8» на базе дешифратора? 10 Каким образом реализуется функция равенства значений одного разряда в цифровых компараторах? Лекция 18

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 971; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.19.29.89 (0.039 с.) |

Он имеет три входа и два выхода. Работа полного одноразрядного сумматора задается таблицей истинности (таблицей 17.2).

Он имеет три входа и два выхода. Работа полного одноразрядного сумматора задается таблицей истинности (таблицей 17.2).

микросхем старших разрядов. Отдельные разряды слагаемых подаются на входы А и В микросхем соответствующих разрядов, а с их выходов S снимаются разряды результата суммирования. Выход переноса Р микросхемы самого старшего разряда является выходом переноса результата суммирования всего n -разрядного числа. Такой способ наращивания разрядности сумматоров путем последовательного объединения нескольких полных сумматоров меньшей разрядности достаточно прост в схемной реализации, но имеет существенный недостаток – низкое быстродействие. Распространение переноса в таких структурах осуществляется последовательно от микросхемы к микросхеме. Этого недостатка лишены сумматоры с параллельным переносом.

микросхем старших разрядов. Отдельные разряды слагаемых подаются на входы А и В микросхем соответствующих разрядов, а с их выходов S снимаются разряды результата суммирования. Выход переноса Р микросхемы самого старшего разряда является выходом переноса результата суммирования всего n -разрядного числа. Такой способ наращивания разрядности сумматоров путем последовательного объединения нескольких полных сумматоров меньшей разрядности достаточно прост в схемной реализации, но имеет существенный недостаток – низкое быстродействие. Распространение переноса в таких структурах осуществляется последовательно от микросхемы к микросхеме. Этого недостатка лишены сумматоры с параллельным переносом. выходов, т.е. для каждой комбинации входных сигналов имеется соответствующий выход. Дешифратор, у которого при п входах число выходов меньше

выходов, т.е. для каждой комбинации входных сигналов имеется соответствующий выход. Дешифратор, у которого при п входах число выходов меньше  , называется неполным. Принцип работы полного трехразрядного дешифратора рассмотрим на примере его таблицы истинности (таблица 17.3).

, называется неполным. Принцип работы полного трехразрядного дешифратора рассмотрим на примере его таблицы истинности (таблица 17.3). ;

; ;

; ;

; ;

; ;

; ;

; ;

; .

.

логических элементов И с n -входами. В существующих микросхемах логических элементов количество входов ограничено. Следовательно, ограничена и разрядность реализуемых на их основе линейных дешифраторов, что является недостатком. Кроме того, недостатком является и то, что предыдущие элементы, работающие на входы дешифратора, должны иметь высокую нагрузочную способность, т.е. должны быть рассчитаны на подключение большого числа логических элементов И. Каждый из входов дешифратора подключен к

логических элементов И с n -входами. В существующих микросхемах логических элементов количество входов ограничено. Следовательно, ограничена и разрядность реализуемых на их основе линейных дешифраторов, что является недостатком. Кроме того, недостатком является и то, что предыдущие элементы, работающие на входы дешифратора, должны иметь высокую нагрузочную способность, т.е. должны быть рассчитаны на подключение большого числа логических элементов И. Каждый из входов дешифратора подключен к  логическим элементам И. Поскольку нагрузочная способность базовых логических элементов ИС не превышает величины N = 10...20, то максимальная разрядность дешифрируемых чисел для линейных дешифраторов n = 4...5.

логическим элементам И. Поскольку нагрузочная способность базовых логических элементов ИС не превышает величины N = 10...20, то максимальная разрядность дешифрируемых чисел для линейных дешифраторов n = 4...5. двухвходовые схемы И. Далее каждая полученная конъюнкция логически умножается на входную переменную X3 в прямой и инверсной форме. Полученная конъюнкция снова умножается на входную переменную X4 в прямой и инверсной форме и т.д. Наращивая таким образом структуру, можно построить пирамидальный дешифратор на произвольное число входов.

двухвходовые схемы И. Далее каждая полученная конъюнкция логически умножается на входную переменную X3 в прямой и инверсной форме. Полученная конъюнкция снова умножается на входную переменную X4 в прямой и инверсной форме и т.д. Наращивая таким образом структуру, можно построить пирамидальный дешифратор на произвольное число входов.

в соответствии с поступающим адресным кодом

в соответствии с поступающим адресным кодом  . При наличии п адресных входов можно реализовать

. При наличии п адресных входов можно реализовать  комбинаций адресных сигналов, каждая из которых обеспечивает выбор одного из М входов. Чаще всего используются мультиплексоры «из 4 в 1» (п = 2, М= 4), «из 8 в 1» (п = 3, М= 8), «из 16 в 1» (п = 4, М= 16). Правило работы мультиплексора «из 4 в 1» Можно задать таблицей истинности (таблица 17.4).

комбинаций адресных сигналов, каждая из которых обеспечивает выбор одного из М входов. Чаще всего используются мультиплексоры «из 4 в 1» (п = 2, М= 4), «из 8 в 1» (п = 3, М= 8), «из 16 в 1» (п = 4, М= 16). Правило работы мультиплексора «из 4 в 1» Можно задать таблицей истинности (таблица 17.4).

направляет информацию с единственного входа D на один из М выходов

направляет информацию с единственного входа D на один из М выходов  . При этом на остальных выходах будут логические нули (единицы).

. При этом на остальных выходах будут логические нули (единицы).

и

и  . В результате сравнения требуется установить либо факт равенства

. В результате сравнения требуется установить либо факт равенства  для всех i в диапазоне от 1 до n, т. е.

для всех i в диапазоне от 1 до n, т. е.  либо факт неравенства

либо факт неравенства  , если хотя бы в одном разряде

, если хотя бы в одном разряде  .

.

из предыдущего разряда и инверсным выходом переноса

из предыдущего разряда и инверсным выходом переноса  в старший разряд.

в старший разряд.