Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Динамические запоминающие устройства повышенного быстродействия

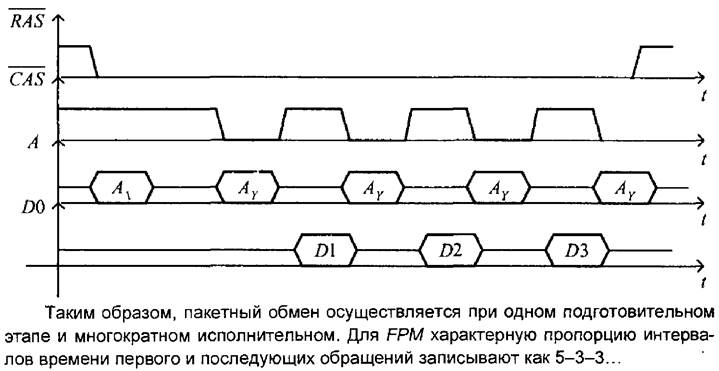

Динамические ЗУ повышенного быстродействия функционируют на основе предположения, что адреса текущего и следующего обращения к памяти с большой вероятностью расположены рядом (совокупность адресов). Это позволяет уменьшить длительность исполнительного и подготовительного этапов обмена данными Рассмотрим кратко основные структуры в развитии DRAM. Считается, что память условно разбивается на страницы, адреса которых подаются старшей частью Ах адресного кода (записывается по стробу RAS). Слова в странице адресуются младшей частью Ау адресного кода (записывается по стробу CAS). Например, для адреса длиной к = 20 имеем 1024 страницы и 1024 слова в странице. Структура FPM (Fast Page Mode) обеспечивает быстрый пакетный доступ к строке (страницы) и слова в нем. В данной памяти адрес строки Ах подается только один раз по стробу RAS. В дальнейшем изменяется только адрес столбца по стробу CAS

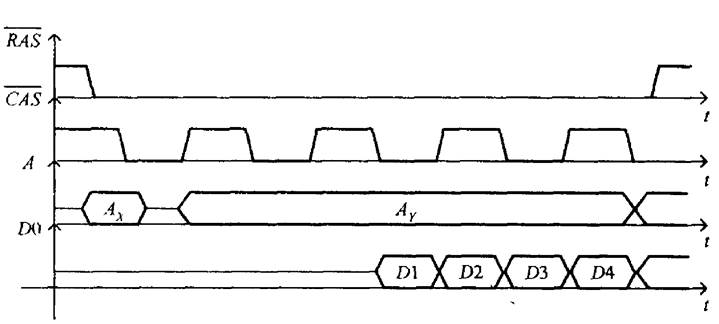

Структура с расширенным выводом данных EDORAM (Extended Data Out RAM) отличается от FPM модификацией процесса считывания данных. В этой памяти по окончанию строба CAS схемы УРЕГ не обнуляются. Они образуют как бы статический регистр, обеспечивающий дальнейшее быстрое считывание в пределах данной строки. Как и раньше, используется только один сигнал CAS, однако его длительность сокращается. Это повышает быстродействие ЗУ. Для памяти EDORAM характерную пропорцию интервалов времени между первым и последующими обращениями представляют как 5-2-2... Разработанные EDORAM обеспечивают работу до В структуре с пакетным расширенным доступом BEDORAM (Burs EDORAM) имеется дополнительный счетчик адресов столбцов. При обращении к пакету (группе слов) адрес столбца формируется только в начале пакетного цикла. В дальнейшем адреса столбцов образуются инкрементом содержания счетчика

Для BEDORAM характерную пропорцию интервалов времени между первым и последующими обращениями представляют как 5-1-1-1, однако и сами интервалы существенно сокращаются. MDRAM В многобанковых структурах MDRAM (Multibank DRAM) память разбита на банки (части). Обращение к банкам осуществляется по очереди. Пока идет обмен с одним банком, в остальных заканчиваются переходные процессы. Эффект ускорения работы такой памяти достигается уже при ее делении на два банка — с четными и нечетными адресами. Банки типа MDRAM могут строиться на обычных микросхемах динамической памяти без каких-либо изменений.

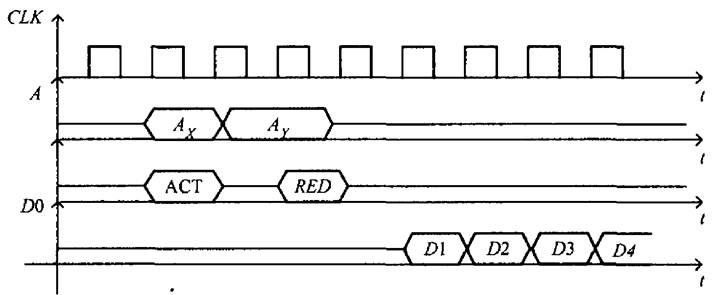

SDRAM Синхронная память типа SDRAM (Sinchronous DRAM) — это быстродействующая динамическая память, которая работает на частоте системной шины без тактов ожидания в середине пакетного цикла. От обычной асинхронной динамической памяти, в которой все внутренние процессы инициируются только сигналами RAS, CAS, W/R, память SDRAM отличается использованием сигналов тактовой частоты системной шины. Это позволяет создать внутри микросхемы высокопроизводительный конвейер с использованием обычных динамических ЭП с временем доступа 50-70 не. Синхронный интерфейс обеспечивает трехкратный выигрыш в продуктивности в сравнении с обычными микросхемами DRAM с таким же быстродействием. Синхронная память типа SDRAM была предложена в 1994 г. как двухбанковая система с трехступенчатым конвейером. Она обеспечивала пропускную способность 250 Мбайт/с и работала на частоте 125 МГц. В целом микросхема SDRAM — это устройство с программируемыми параметрами, внутренней организацией чередования банков и собственным набором команд, в том числе: • MRS— программирование параметров пакетного цикла; • ACIT— активизация верхнего Гили нижнего В банка и ввод адреса строки; • DEAC — предварительный заряд шин; • WRT, RED — запись или чтение и ввод адреса столбца; • REFR — автоматическая регенерация (рефреш) с периодом 15,6 мкс. Возможно задать рефреш с большим периодом; • SLER — самогенерация без внешних сигналов, при этом чтение и запись запрещены; • PDE — режим хранения с пониженным энергопотреблением (питание внешних буферов отключается).

RDRAM Микросхемы RDRAM (Rambus DRAM) — это байт-последовательная память, в которой синхронизация осуществляется двумя фронтами тактовых импульсов и применяется новый интерфейс Rambus Channel (имя фирмы-разработчика). В первой разработке при частоте тактирования 250 МГц темп передачи байта составляет 500 МГц, затем частота стала больше еще в 1,5-3 раза. Интерфейс Rambus Channel имеет всего 13 сигнальных линий без специализированных линий адреса. Вместо обычной адресации по интерфейсу посылаются вначале пакеты команд, затем следует пакет подтверждения, а далее — пакет данных. Первый доступ к данным сильно запаздывает: в первых разработках — до 128 не.

Память типа RDRAM эффективна при пакетном обмене: например, для 256 байт в пакете частота обмена равна 400 МГц, а для 64 байт — 250 МГц и т.д. Такая память идеально подходит для графических и мультимедийных применений с типовым для них процессом — быстрой выдачей последовательности слов при формировании изображения на экране или для других подобных задач. DRDRAM Память типа DRDRAM (Direct RDRAM) в сравнении с RDRAM имеет меньшее запаздывание при первом доступе к данным. В DRDRAM пропускная способность в середине пакета составляет 1,6 Гбайт/с. Это превышает частотные возможности современных системных шин. CDRAM В кэшированных структурах CDRAM (Cached DRAM) на одном кристалле с DRAM размещена также статическая кэш-память уровня L1. При этом кэш обеспечивает быстрый обмен с процессором при наличии информации в кэше, а также быстрое обновление своего содержимого. Это объясняется тем, что связи между обоими выводами на кристалле являются внутренними. При этом разрядность шин может быть большой и обмен может осуществляться большими блоками данных. Например, в CDRAM фирмы Ramtron применяется 2048-разрядная шина для обновления содержимого кэша.

|

|||||||||

|

Последнее изменение этой страницы: 2016-08-06; просмотров: 752; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.128.199.162 (0.005 с.) |