Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Представлення оа в вигляді структуриСтр 1 из 3Следующая ⇒

ПРЕДСТАВЛЕННЯ ОА В ВИГЛЯДІ СТРУКТУРИ Сегментація

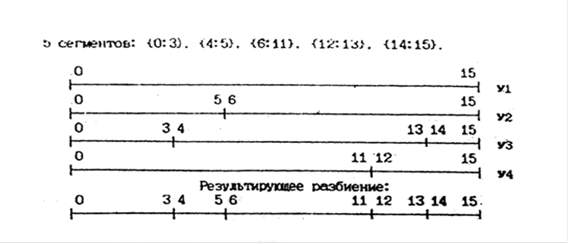

Для фізичної реалізації деякого сегмента достатньо роздивитися синтез тільки одного розряду сегмента (надалі обраний розряд будем називати представником сегмента): для інших розрядів рішення тиражируются. Аналогічно надходять і з іншими сегментами. Методика розбивки на сегменти, тобто сегментація, заснована на том. що по черзі розглядається кожна МО, виконувана БФР або шиною, при цьому виявляються розряди регістра (шини), що виконують ту саму функцію. Потім розглядається вся сукупність МО (при синтезі КС1 =У1, КС2 =У2,) і проводиться перетинання вихідних сегментів: при цьому утворяться нові сегменти, що також складають розрядне поле БФР або шини. Сегменти для однієї МО звичайно виділяються знаками конкатенации. Нехай, наприклад, для МО у1 та у2 маємо: У1: Рг:=Рг V А, У2: Рг (О:15):=(Рг)(0:5)) & А(0:5).А(6:15). У першому випадку кожний розряд БФР виконує ту саму функцію - диз'юнкцію значень розрядів з однаковим номером слова, що зберігається в регістрі, і вхідного слова, тобто всі розряди БФР складають один сегмент (поле, оскільки цей сегмент іменований). Аналогічно виконуються МО кон`юнкції, додавання за модулем 2 і інші двомісні логічні операції (операнди повинні мати однакове число розрядів!). В другому випадку старші 6 розрядів БФР виконують функцію порозрядної кон`юнкції вхідного слова і слова, що зберігається в регістрі, а інші його 10 розрядів повторюють значення частини вхідного слова. Отже, поле БФР можна розбити на два сегменти: {0:5} і {6:15}. Відзначимо, що в кожному конкретному випадку необхідно проаналізувати опис мікрооперації із метою виявлення сегментів, у розрядах яких виконуються ті самі функції. Потім установлюються загальні для сукупності МО сегменти як перетинання сегментів окремих МО. Приклад. Нехай для деякої 16-бітової перемінної з пам'яттю R множина МО складає У1={У1, У2, УЗ, У4), де У1, У2 - МО, аналогічні розглянутим вище (змінну Рг варто замінити на змінну R), а МО у3, у4 описані слідуючим чином. У3: R(0:15):= ((А(0:3).А(4:13): У4: R(0:15): = ЯКЩО R(0), ТО R (0:15) ІНАКШЕ (R(0:11) А (0:11)). А (12:15) Зрозуміло, що для МО у3 необхідно розбієння поля R (0:15) на сегменти (0:3), (4:13) та (4:15), а для МО у4 - на сегменти (0:11) та (12%15), оскільки дані сегменти оброблюється різними засобами.

На рис. 4 представлені сегменти для кожної МО множини У1 відміченні на відрізках, що відображають розрядку сітку змінної R, а також результативне розклад такого відзрізка. Видно, що змінна R на множині У1 має

Рис. 4. Приклад сегментації

Таблиця 1 Сводна оборотна таблиця переходів для тригерів D-, T-, RS-, JK- типів

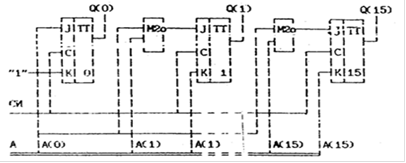

Як очевидно з рис. 5, вибір вихідних перемінних того або іншого обчислювача здійснюється за допомогою комутатора під впливом відповідного керуючого сигналу. При цьому має значення кількість входів тригера (особливий випадок - наявність керуючих входів у тригера!): кількість виходів комутатора дорівнює кількості входів тригера. Зокрема, якщо в тригера два інформаційних входи (для RS або JK- тригера), то комутатор реалізує такі логічні функції: Ф1і= Fl 11у1+Fl 12у2+….. Fl gуg+Fl g+1у1у2…уg (2) Ф2і= Fl 21у1+Fl 22у2+….. Fl 2gуg+Fl 2g+1у1у2…уg (3) де Fl 11.Fl 21 – вихідні змінні обчислювачів Fl j = 1, g+1 F1, F2 - вихідні змінні додаткового обчислювача Ф1i, Ф2i - функції збудження i-го тригера. Якщо ж кількість інформаційних входів дорівнює i (D- або Т- тригер), то для опису функціонування комутатора достатньо одного рівняння (2) або (З). Відомі також тригерні пристрої, які мають три і більш інформаційних входи. Проте ці входи несуть різноманітне функціональне навантаження: як правило частина з них є синхронизуємимі, а інші - входи примусової установки тригера, тобто асинхронні входи; сигнали на асинхронні входи надходять від інших операційних пристроїв. Для БФР, побудованого на базі асинхронного регістра, його функціональна схема (рис.5).змінюється мало - відсутній вхід синхронізації, але тепер сигнал МО У повинний нести подвійне навантаження: він визначає і що повинний робити БФР. і коли це робити. Останнє означає, що ускладнюється керуючий автомат даного ОУ. Роздивимося особливий випадок регістра, що мав загальний вхід керування V. Ясно, що на нього може бути поданий сигнал узагальненої мікрооперації

У=у1+у2+….уа (4)

при цьому потреба в обчислювачі F відпадає, тому що при у1=у2=……уа=0 та V =0, тобто регістр буде берегти попередню інформацію.

Таблиця 3

Таблиця 4

СИНТЕЗ ШИНИ ТА КОМУТАТОРА Шина - це пристрій, що подає собою сукупності ліній зв'язку і комбінаційної схеми, що формує визначені значення сигналів, що діє на цих лініях, під керуванням тієї або інший МО. Шина інтепретує перемінну без пам'яті В, яка у загальному випадку описуються в такий спосіб:

У1: В:= Ф (А1, А2…. Ак, R) (7) де А1. А2, Ак - вхідні для БФР перемінні; R – вихідна перемінна з пам'яттю, що інтерпретується регістром, значення якої не змінюється протягом такту, коли діє МО у1: Ф - Функція, що Формує значення розрядів змінної для передачі їх у зовнішню щодо даного БФР середовище. Відзначимо розходження вхідних і вихідних перемінних без пам'яті: перші є зовнішніми щодо даного БФР і тому ' при його побудові інтепретуються тільки лініями зв'язку, а другі є внутрішніми для БФР і інтепретуються шиною. МО у1 входить у підмножину У2, що визначає роботу КС2 (рис.3). Очевидно, структура КС2 подібна структурі КС1 поданої на рис.5 одним розрядом: КС2 також складається із обчислювачів (Фа+1…..Фм) і комутатора, керованого сигналами Уа+1...Ум. Відмінність КС2 від КС1 визначаються відсутністю залежності перемінної У від її значень у попередній момент часу. КС2 не має особливостей КС1, тобто вузла пам'яті і додаткового обчислювача: у тої ж час варто мати на увазі, що при роботі БФР на магістраль на виході КС2 необхідно застосувати буферний каскад. При синтезі КС2 у загальному випадку також необхідна сегментація, але вже щодо розрядності перемінної В. Синтез КС2 декілька відрізняться від. синтезу КС1, що визначається розходженням вихідних перемінних цих схем: крім того, результат перетворення вхідних перемінних у КС1 виявляється на слідуючем такті, а в КС2 - у даному такті. Відповідно до цього і заповнюється табл. 5. Відзначимо тільки, що стовпчик "В" заповнюється построчно значеннями, обчисленими по (7) для представника j-го сегмента (деякого i-го розряду) для даної МО иэ підмножини У2: Відмітемо також, що номера розрядів для вхідних перемінних А не обов'язково збігаються з i-м. Аналогічно (6) можуть бути описані КС обчислювачів, що вироблюють функції порушення Fі. і для інших МО.

Рис.6. Фрагмент схеми обчислювача

Для реалізації КС обчислювачів може бути використаний досить широкий арсенал засобів [2-7]: найпростійші логічні элементи I-НІ (АБО-НІ), мультіплексори (МП), дешифратори (ДШ), арифметико-логічні пристрої (АЛП), логічні матриці, що програмуються (ПЛМ), постійні пристрої, що запам'ятовують (ПЗУ), причому ДШ, ПЛМ, ПЗУ дозволяють реалізувати систему рівнянь виду (6) тобто будувати декілька обчислювачів. Об'єднання функцій збудження здійснюється відповідно до формул виду (2) для тригера з одним інформаційним входом, або виду (2) та (.3) - для тригера з двома інформаційними входами. Фізично ці формули реалізуються відповідно одною або двома схемами І-АБО: конкретна реалізація схеми визначається її складністю і заданим критерієм оптимальності.

Таким чином проводиться синтез обчислювачів для КС1, що відносно коммунікатора для КС1, то його синтез проводиться так. Таблиця 5

Очевидно, табл. 5 являє собою таблицю істинності, і подальший синтез по ній здійснюється звичайними засобами [2-7]. Аналогічно заповнюються таблиці і для інших МО з У2 і синтезуються відповідні обчислювачі 1-го розряду. Потім ці рішення тиражуются на всі розряди.3--го сегмента. Роздивимося синтез комутатора. Вище було відзначено, що обидві комбінаційні схеми, КС1 і КС2, мають у своєму складі комутатор. Комутатор реалізує логічну функцію І-АБО, причому Функція І дозволяє вибрати одну з множини вихідних перемінних обчислювачів, а АБО - об'єднати результати вибору. Технічна реалізація функції І-АБО може бути здійснена декількома засобами: - за допомогою мультиплексора; - на двох'ярусній схемі І - НІ: - на схемах І (І-НІ) із відкритим колектором: - на схемах І (І-НІ) із трьома станами. Перші два засоби припускають явну реалізацію комутатора, причому на мультиплексор (на його адресні входи) повинні надходити сигнали МО в двоїчно кодованому виді.. При третьому і четвертому засобах комутатор реалізується неявно - він "убудовується" в обчислювач, що досягається введенням у схему обчислювача керуючого сигналу (МО у1) і монтажним об'єднанням виходів обчислювачів. При третьому засобі сигнал, що управляв, у1 вводиться в елементи І-НІ першого ярусу обчислювача, а елементи І-НІ другого ярусу схем обчислювачів є схемами з відкритим колектором. При четвертому засобі сигнал У1 управляє станом "Включений /Виключений" елементів І-НІ другого ярусу схем обчислювачів. Відзначимо, що в більшості випадків вхід керування станом елемента є інверсним. У випадку невеличкого числа простих. обчислювачів можливо ще більше спрощення схем КС1 - монтажне об'єднання виходів елементів першого ярусу усередині обчислювачів із подальшим монтажем об'єднанням виходів обчислювачів.

Вибір регістру

Тип регістра вибирається в залежності від наявності в списку МО реалізованих БФР мікрооперації, зсуву. Регістр повинний бути тактуємим, мати входи початкової установки. Варто мати на увазі, що якщо регістр побудований на D-триггерах, то для зберігання інформації при відсутності МО необхідно організувати подачу на входи регістра сигналів із його виходів. У деяких випадках доцільно пропускати вхідної сінхросигнал через елемент І, керований сигналом відповідним відсутності МО.

Вибір схеми комутатора

Комутатор є одним із важливих компонентів БФР і його проектуванню мало приділити пильну увагу. У разд. 3 показані можливі реалізації комунатора, аж до "розчинення" комутатору у схемах обчислювачів. Кращим варіантом буде той, який задовольняє критерію якості схеми. Варто мати на увазі, що вихідний комутатор, що працює на магістраль, може входити до складу шини, і тоді він повинний володіти трьома станами.

Вибір буферних устроїв

У якості буфера можуть бути обрані шинні формировачі з прямим (інверсним) виходом або двунаправленний підсилювачем із великою навантажувальною спроможністю. І в тому й в іншому випадку, необхідно наявність третього стана.

Вибір часових параметрів.

У завданні приводиться значення тактової частоти надходження синхроімпульсів. Це не обов'язково меандр, і оскільки частіше усього затримка в схемі КС1 більше затримки в КС2, то тривалість імпульсу більше тривалості паузи. Протягом такту надходять, дві МО: одна призначена для опрацювання вхідної інформації і запису її в регістр, а друга - для додаткового опрацювання і видача результату в магістраль. Таким чином, при проектуванні БФР необхідно домогтися того, щоб сумарна затримка від моменту надходження даних із магістралі до моменту видачі результату в магістраль не перевищувала тривалість такту.

4.6. Побудова другого варіанта БФР (реалізація КС на ПЗП або ПЛМ) у багатьох випадках дозволяє істотно спростити його комбінаційну частину, при цьому критерієм якості схеми є мінімум корпусів мікросхем (МС). Для реалізації схеми на ПЛМ (ПЗП) необхідно вибирати достатньо складні функції. У випадку, якщо для реалізації функції можна використовувати декілька логічних елементів, доцільно обійтися без ПЛМ (ПЗП) При виборі типу ПЛМ (ПЗП) необхідно враховувати додатково такі чинники, як навантажувальна спроможність, швидкодія, споживана потужність і співвідносити їх із такими ж показниками іншої частини БФР. При синтезі КС на базі ПЛМ виду мхnхp (м- число входів, n- число виходів, р- число кон’юнкцій) доцільно сукупність булевих функцій, які необхідно реалізувати, та поданих у виді ДНФ. розбити на групи не більш ніж по р функцій, для яких кількість перемінних не перевищує m, а кількість конъюнкций у дизъюнктивной формі - n. Получена кількість груп і визначає число мікросхем ПЛМ. Необхідно відзначити, що булеві функції повинні бути промінімізовані, причому бажано виконати спільну мінімізацію функцій. У разі потреби функцію f з числом перемінних більш, чим m, розбивають на декілька частин так, щоб в кожній кількість перемінних не перевищувала m. Кожну таку частину збирають на окремих мікросхемах ПЛМ, що відповідні виходи якіх об'єднуються безпосередньо (якщо вони з відкритим колекторам) або з допомогою елементів АБО.

У якості ПЛМ рекомендується використовувати мікросхеми серії К556. При синтезі комбінаційної частини БФР на базі ПЗП необхідно мати на увазі, що мінімізація функцій, котрі реалізуються на ПЗП, не потрібна: навпаки, усі функції потрібно розгорнути до СДНФ. ПЗП необхідно вибирати з тих розумінь, щоб кількість адресних входів була не менше, чим число змінних у булевих функціях. Тут, як і для ПЛМ, треба сукупність функцій, реалізованих на ПЗП, розбити на групи функцій із загальною кількістю змінних не більш m (m,n - кількість виходів і входів ПЗG відповідно). Кількість груп визначає кількість мікросхем ПЗУ. У випадку, коли кількість змінних функції перевищує число адресних входів ПЗУ, функцію потрібно уявити у виді декількох функцій (звичайно двох), кожна з який містить не більш, чим n змінних і реалізується на однієї МС. Відповідні виходи МС об'єднуються за допомогою елементів АБО, або безпосередньо (монтажне АБО), якщо в МС передбачений третій стан, або за схемою монтажного АБО з використанням додаткового резистора, якщо виходи МС із відкритим колектором. Рекомендується в якості ПЗУ використовувати МС серії К573,..

5. ЗМІСТ ТА ПОРЯДОК ВИКОНАННЯ КУРСОВОГО ПРОЕКТУ

5.1 Зміст курсового проекту

Тема курсового проекту: " Багатофукціональний регістр". Ціль курсового проекту - придбання навичок проектування багатофункціонального регістра як основного вузла операційного автомата з використанням системи автоматизованого проектування. Ця ціль досягається шляхом самостійної розробки студентом комбінаційних схем обчислювачів і комутаторів по відомій структурі регістра на сучасній елементної базі, а також моделюванням динаміки (процесу переключень) схеми регістра. Варіанти курсового проекту утворяться шляхом завдання визначеного набору мікрооперацій і елементної бази. Варіанти завдань на курсове проектування приведені в табл. 6: конкретний вид МО вибирається зі списку табл. 7.

ПРЕДСТАВЛЕННЯ ОА В ВИГЛЯДІ СТРУКТУРИ

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-07-11; просмотров: 39; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.224.70.238 (0.04 с.) |