Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Этапы установки модели в системе ModelSim

Для уверенного использования данного приложения следует ознакомиться с основными пунктами меню: File - стандартный пункт главного меню для работы с файлами, в свою очередь содержащий следующие пункты: Derictory... - установка текущей рабочей директории. Execute Macro... - загрузка готовых сценариев моделирования четко установленного устройства. Compile VHDL.... - компиляция и установка файла описания устройств на языке VHDL для моделирования их поведения. Compile Verilog... - компиляция модулей HDL описаний устройств. Simulate... - непосредственно моделирование. Пункт активен при условии, если загружен или создан проект и скомпилирован исходный VHDL файл. Restart... - возвращение устройства моделирования к исходному состоянию. Под исходным состоянием понимается начальный момент времени моделирования. Пункт активен при условии процесса моделирования. Select Source File... - загрузка, если уже был произведен запуск системы на моделирование. End Simulate... - окончание VHDL файла с исходным описанием устройства. Пункт активен при окн Source является в данный момент активным.Exit ModelSim... - выход из программы. Process - окно со списком всех процессов, имеющихся в исходном VHDL описании. Wave - окно с временными диаграммами необходимых сигналов или портов ввода/вывода моделируемого устройства. Возможен ограниченный вывод числа диаграмм при условии использования окна Signals и одноименного пункта главного меню. DataFlow - окно со схематическим изображением потоков данных в моделируемом устройстве. Возмжно конкретизация некоторых сигналов или портов ввда/вывода с помощью мыши при нажатии на необходимое имя сигнала (порта иотеками. Содержит следующие пункты: Mapping... - установка и редактирование списка и расположения стандартного набора библиотек, входящего в пакет поставки типичной версии ModelSim. с проектами. Имеются следующие функциональные пункты: New... - создание нового проекта моделирования устройства. Change... - загрузка уже суествующего списке перечислены загруженные, но не активизированные проекты. Основной функцией списка является оперативный переход от В частности указываются используемые стандартные пакеты одного проекта к другому.

Run... - контроль за временной дискретностью при процессе моделирования. Пункты данного меню активны в случае работы режима моделирования. Содержит следующие пункты: Run.... [ t ] - запуск моделирования на установленный промежуток времени t. Установка дискретности производится в параметрах моделирования. Run Forever... - запуск моделирования на период, ограниченный внутренними свойствами моделируемого устройства, т.е. временем активности генератора или самого устройства. Step... - запуск моделирования на период времени равный, активности одной итерации в пошаговом режиме функционирования модели. Step Over... - моделирования с текущей итерации вплоть до точки остнова или до окончания функционирования модели устройства. Cont... - продолжение мделирования с текущей итерации. Break... - остановка процесса моделирования на текущей итерации. Основные пункты меню дублируются в виде кнопок на панели. Кроме главного меню, система имеет главное окно Transcript. Данное окно информирует обо всех процессах, протекающих в системе, кроме этого сообщает об ошибках или некорректных ситуациях при моделировании или компиляции файлов. В нижней части окна существует командная строка - для диалогового режима работы системы (рис. 11).

Рис. 11. Окно Transcript.

Теперь необходимо перейти непосредственно к этапам подключения модели: 1. Создать проект: - в главном меню Project выбрать пункт New...; - ввести имя проекта. 2. Добавить к проекту исходный файл с VHDL описанием моделируемого активного устройства: - в главном меню File активизировать пункт Compile VHDL; - появится панель выбора файла (рис. 12);

Рис. 12. Панель выбора подключаемого VHDL файла

- откомпилировать файл нажатием кнопки Compile. При этом если файл содержит ошибки или неточности, то информация об этих ситуация будет выведена отдельно в окне Transcript; -если отсутствуют ошибки, подтвердить выбор файла кнопкой Done. Замечание: при наличии ошибок или неточностей файл подключен не будет.

3. Начать моделирование проекта: - выбрать пункт Simulate главного меню File;

- появиться панель установок модели - Simulate Design (рисунок 13);

Рис. 13. Панель выбора устройства моделирования Simulate Design

- на вкладке Design в поле design unit с помощью мыши выбрать название устройства (объекта); - если подключаемый файл имеет реализацию функций данного устройства (основную конструкцию VHDL - архитектуру), то в самом нижнем поле появится ее название; необходимо с помощью курсора мыши указать название варианта реализации, который нужно промоделировать; - подтвердить выбор модели кнопкой Add; подтверждением правильных действий в данном случае будет появление в поле Simulate имени архитектуры устройства; - далее по мере необходимости нужно выбрать степень дискретизации времени с помощью выпадающего списка в поле Simulate Resolution; - подтвердить установки процесса моделирования нажатием кнопки Ok. Удачный ввод установок модели будет проинформирован в окне Transcript. После корректной установки устройства моделирования. Возможны любые действия, необходимые для анализа функционирования проектируемого устройства. В следующем пункте будут описаны некоторые из них..NKHLLLLTTYEYOMMIUMNUIPNPUINY8UB

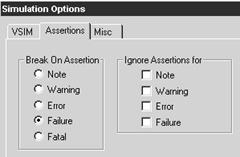

Моделирования в ModelSim При отсутствии ошибок на этапах подключения файла с исходным активным устройством для моделирования можно начать сам процесс моделирования. В зависимости от целей моделирования в системе ModelSim предусмотрены: коноль за временной дискретизацией моделирования, а также возможность непосредственного наблюдения практически за всеми ключевыми процессами, происходящими устройстве (последнее будет рассмотрено в следующей лабораторной работе). Рассмотрим средства контроля за моделированием. В этом смысле для полноценного контроля за процессом моделирования необходимы: главное меню Run и Options. В меню Run для контроля предназначены все пункты, а в меню Options - пункт Simulate Options (установка частных параметров моделирования). При активизации пункта Simulate Options появляется панель ввода параметров моделирования(рисунок 14). В данной панели содержится три вкладки: VSIM - непосредственно параметры моделирования. Здесь устанавливаются следующие параметры: Default Run length - установка минимальной временной дискретизации процесса моделирования.

Suppress Warnings - отключение/включение реакции системы на предупреждения, связанные с различного рода неточностями. Default Force Kind - установка возможности управления процесса моделирования (Freeze (отсутствие контроля)/ Drive (управление)/ Deposit (полностью под контролем)). Default Radix - вид сигнала по умолчанию (Symbolic (символьный) /binary (двоичный) / octal (восьмеричный) /decimal(десятичный)/hex(шестнадцатеричный)).

Рисунок 14 - панель Simulate Options

Ase ащитный действия системы на различного рода ошибки (рис. 15): rtion - Break On моделирования. (Note (комментарий) /warning (ошибка)). Ignore Assertions for - установка границ пренебрежения системой защиты. (Note (комментарий)/ warning (неточность)/ error(- установки параметров вывода исходного файла в окне Source ошибка)/ failure ("провал")). действий системы Misс.

4. Ход работы

4.1. С помощью любого текстового редактора набрать описание цифрового устройства в соответствии с вашим вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd.

4.2. Создать проект в системе моделирования ModelSim и подключить к нему набранный и отлаженный в FPGA Express файл. 4.3. После корректного подключения файла описания осуществить установку системы для тестирования вашего устройства.

- 5. Указания - теоретическую часть; - описание последовательности действий при установкие описания устройства для моделирования; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе

1. В чём заключается необходимость использования систем моделирования подобных ModelSim. 2. Каковы недостатки системы, если таковые присутствуют? 3. Какова на ваш взгляд область применения системы ModelSim?

Лабораторная работа № 4

СИМУЛЯТОР MODELSIM

1. Общее описание работы

1.1. Цель работы – получение навыков для моделирования проектируемых устройств в системе ModelSim.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в повторении принципов работы с симулятором ModelSim, освоенных в предыдущей лабораторной работе. Лабораторное задание состоит в подключении вашего варианта примера программы, написанной на VHDL, и в проведении полноценного моделирования и анализа проектируемого устройства с помощью ModelSim.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

Повторить материал, освоенный на предыдущих занятиях.

3. Теоретическая часть

и вывода) / Internal Signals (внутренние сигналы)). Для этого в ModelSim была создана система информационных и функционально-информационных окон (главное меню View). Главным условием работы всех окон является корректно подключенный исходный файл с VHDL описанием моделируемого устройства. Рассмотрим принципы работы с ним: 1. Source - окно с содержанием исходного VHDL - файла (рис. 16). Позволяет устанавливать точки останова (для этого необходимо двойное нажатие левой кнопкой мыши на номере строки). Для изменения содержимого окна нужно активизировать пункт Select Source File... главного меню File (поменять исходный файл можно только на файл, подключенный к проекту), либо двойное нажатие левой кнопкой мыши в окне по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; используемое оборудование;Structure на названии необходимого файла. Замечание: окно не позволяет редактировать исходные файлы.

Рис.16. Окно Source

2. Structure - окно содержащее структуру и подчиненность файлов проекта (рис. 17). Несет вспомогательную функцию для окна Source. Рис. 17. Окно Structure

4. Signals – окно, содержащее список и значения всех портов ввода/вывода и сигналов (рис. 19). Окно фиксирует любые изменения содержимого всех портов ввода/вывода и сигналов. Существует возможность удаления, добавления или установки ограниченного числа сигналов или портов в данном окне в зависимости

Кроме этого важным свойством окна Signals в совокупности с пунктом Force Signal главного

Рис. 20. Окно View Signals.

К параметрам изменений относятся следующие: Signal - название сигнала (обычно указывается в виде подчиненности. Например: устройство CODER содержит порт ввода/вывода X4, тогда соответственно полное имя сигнала CODER.X4).

Рис. 21. Окно Force Signal

Delay - время задержки текущего значения сигнала (масштаб значения указывается справа от поля ввода). Second Value значение - следующего состояния данного сигнала или порта ввода/вывода. : для вводить именно тот тип задержки перед изменением текущкомендуется значения, который Примечание предупреждения ошибок, связанных с моделированием устройства, ре Delay for second Value - значение предусмотрен для проектируемого устройства. его состояния на последующее (Second Value). Примечание: значение данного поля должно быть обязательно обоех задержек сигналов.

Примечание: значение данного поля должно быть обязательно больше значения в поле Delay for second Value, поскольку начальная точка временного отсчета процесса моделирования является общей для всех задержек сигналов. Kind - установка степени автономности производимых изменений. (Freeze (система автономно управляет изменениями) / Drive (возможность управления) / Deposit (бесконтрольное управление проектировщиком)). Для подтверждения введенных параметров изменений сигнала или порта ввода/вывода следует нажать кнопку Apply.

Для установки параметров изменений другого сигнала, его предварительно необходимо выбрать в окне Signals.

5. List – окно, содержащее дискретный по времени список сигналов и их значения (своего рода таблица истинности по всем сигналам или портам ввода/вывода в Рис. 22. Окно List.

Примечание. Mинимальный шаг регистрации изменений значений сигналов устанавливается в параметрах процесса моделирования (Options.../ Simulate Options...). В окне предусмотрены различные опции связанные с фиксированием изменений сигналов и сохранения полученной таблицы в отдельном файле. 6. Process – окно, содержащее название и состояние VHDL -процессов текущего моделируемого устройства (рис. 23). Имеется возможность ограниченного вывода процессов при использовании пункта Processes в главном меню Options (возможно вывести все активные процессы (View Active Processes) или активные процессы на текущем шаге (итерации) моделирования).

Рис. 23. Окно Process

7. Wave – окно, необходимое для вывода временных диаграмм определенного набора сигналов или портов ввода/вывода (рис. 24).

Рис. 24. Окно Wave

Окно обладает всеми свойствами гибкого средства наблюдения за изменениями сигналов во временных рамках самого процесса моделирования. В совокупности с окном Signals и пунктом Add to Waveform главного меню Signals данное окно имеет возможность определения ограниченного списка сигналов подпункт Selected Signals (установка в рабочий список сигналов, выделенных в окне Signals), подпункт Signals in Region (наблюдение за активными сигналами на текущей итерации моделирования), подпункт Signals in Design (установка всех сигналов проекта), подпункт Signals from DataFlow (установка сигналов, участвующих в выбранном информационном потоке, из окна DataFlow)). Как и все функциональные окна, это окно имеет возможности для работы со списком выводимых сигналов (меню окна Cursor и Edit), позволяет управлять выводом временных диаграмм (меню окна Zoom и Options). Дополнительным вспомогательным средством является бегунок (устанавливается в любой точке на диаграмме с помощью мыши), фиксирующий время моделирования в текущем положении. Кроме этого при изменении положения бегунка, если в следующем положении меняются значения какого-либо из сигналов, соответствующие изменения регистрируются в списке изображаемых сигналов (слева от диаграмм, как это показано на рис. 24). 8. DataFlow – окно, выводящее организацию всех информационных потоков, присутствующих в моделируемом устройстве (рис. 25).

Рис. 25. Окно DataFlow

Как и большинство функциональных окон, это окно работает в совокупности с другими окнами: Signals (данное окно позволяет выбрать рассматриваемый(ые) сигнал(ы) для дальнейшей визуализации связанных с ним(ними) информационных потоков в окне DataFlow). Process (с помощью этого окна можно выбрать процесс для дальнейшей демонстрации его информационных потоков).

4. Ход работы

4.1. С помощью любого текстового редактора набрать описание цифрового устройства в соответствии с вашим вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd. 4.2. Создать проект в системе моделирования ModelSim и подключить к нему набранный и отлаженный в FPGA Express файл. 4.3. После корректного подключения файла описания осуществить установку системы для тестирования вашего устройства. 4.4. Провести тестирование и полный анализ вашего цифрового устройства в соответствии с вашим вариантом.

5. Указания по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; - используемое оборудование; - теоретическую часть; - описание последовательности действий при процессе анализа и моделирования вашего варианта; - распечатку всех состояний, всех сигналов; - распечатку вашего исходного файла; - распечатку временных диаграмм и процессов; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе

1. Каковы основные функции окон Signals и Wave? 2. Насколько важна визуализация структуры информационных потоков в устройстве при проектировании?

Лабораторная работа № 5

ЗНАКОМСТВО С ЯЗЫКОМ VHDL

1. Общее описание работы

1.1. Цель работы – изучение основных типов данных и конструкций в языке VHDL.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в повторении ранее изученного материала и самостоятельном освоении наиболее простых типов данных, описанных в учебном пособии. Лабораторное задание заключается в создании простейшего устройства на основе объекта и его архитектуры для дальнейшей проверки с помощью отладчика FPGA EXPRESS, моделирования и тестирования его функциональных свойств с помощью ModelSm.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

По методическому руководству и учебному пособию ознакомиться со всеми типами данных и конструкциями, используемыми при описании цифровых устройств на языке VHDL.

3. Теоретическая часть

VHDL делит объекты на внешние, или видимые (обладающие именами и связями), и внутренние, или невидимые (алгоритмы и исполнение). После того как определён внешний интерфейс с объектом, другие объекты могут использовать его по мере собственного создания. Такая концепция внутреннего и внешнего взглядов является центральной при рассмотрении системных проектов VHDL. Объект определяется своим поведением и связями. Вы можете исследовать альтернативные исполнения (архитектуры) объекта без изменения остальной части проекта. После того как создаётся объект в одном из проектов, можно использовать его по мере необходимости в других проектах. Кроме того, допускается создавать библиотеки объектов для применения во многих проектах или семействах проектов. Аппаратная модель VHDL показана на рис. 26.

Рис. 26. Аппаратная модель VHDL Объект VHDL (проект) имеет один или более входов, выходов или портов ввода-вывода, которые соединяются с соседними системами. Объект сам по себе состоит из совокупности соединенных между собой объектов, процессов и компонентов, которые работают совместно. Каждый объект определяется частной архитектурой, которая составлена из конструкций VHDL, таких как арифметические, сигнальные или компонентные реализации. В VHDL независимые процессы моделируют поведение последовательных (тактируемых) схем, использующих триггера и защелки, и комбинаторных (нетактируемых) схем, использующих только логические элементы. Процессы могут определяться и называться подпрограммами (подпроектами). Процессы соединяются друг с другом с помощью сигналов (проводников). Сигнал имеет источник (формирователь), один или более приемников и определяемый пользователем тип, например, «цвет» или «числа от 0 до 15». VHDL обеспечивает широкий набор конструкций. С помощью VHDL можно описать дискретные электронные системы различной сложности (системы, платы, чипы, модули) с различными уровнями абстракции. Конструкции языка VHDL подразделяются на три категории в зависимости от уровня абстрагирования: поведенческую, поток данных и структурную. Эти категории можно описать следующим образом: поведенческая (behavioral). Функциональные или алгоритмические аспекты проекта, выраженные в виде последовательного процесса VHDL. поток данных (dataflow). Просмотр прохождения данных через весь проект, от входа к выходу. Работа в данном случае определяется в терминах набора преобразований данных, выраженных в виде параллельных утверждений. структурная (structural). Просмотр, наиболее приближенный к аппаратному обеспечению; модель, в которой связаны все компоненты проекта. Такой просмотр выражается в виде компонентных реализаций.

Описание проектов Каждый проект цифрового устройства подразумевает работу с единицами информации, которые представлены в VHDL, как и в языках высокого уровня, различными типами данных.

Объявления типов Объявления типов определяют имя и характеристики типа. Тип - это именованный набор значений, таких, как набор целых или набор (red, green, blue). Объект данного типа, такой сигнал, может принимать любые имеющиеся в нем значения. В примере 1 показано объявление типа NEW_BIT, а также некоторых функций и переменных этого типа. Объявления типов разрешены в архитектурах, блоках объявлений, объектах, блоках, процессах и подпрограммах. Объявления подтипов Объявления подтипов используют для обозначения имени и характеристик ограниченного подмножества другого типа или подтипа. Подтип является полностью совместимым с родительским типом, но только в определенном диапазоне. В следующем объявлении подтипа (NEW_LOGIC) определяется поддиапазон типа, объявленного в примере 1.

Пример 1 ... subtype NEW_LOGIC is NEW_BIT range ’0’ to ’1’; ...

Объявления подтипов разрешены там же, где и объявления типов: в архитектурах, блоках объявлений, объектах, блоках, процессах и подпрограммах. Объявления констант Объявления констант создают именованные значения данного типа. Значение константы может быть прочитано, но не изменено. Объявления констант разрешены в архитектурах, блоках объявлений, объектах, блоках, процессах и подпрограммах. В примере 2 показаны некоторые объявления констант. Пример 2. Объявления констант

... constant WIDTH: INTEGER:= 8; constant X: NEW_BIT:= ’X’; ... Объявления сигналов Объявления сигналов создают новые именованные сигналы (проводники) данного типа. Сигналам могут быть присвоены начальные значения (по умолчанию). Однако эти начальные значения не используются для синтеза. Сигналы с несколькими источниками (сигналы, управляемые присоединенной логикой) могут иметь соответствующие функции разрешения. В примере 3 показано два объявления сигналов.

Пример 3. Объявления сигналов ... signal A, B: BIT; signal INIT: INTEGER:= -1; ...

Примечание. Порты также являются сигналами, у которых есть ограничения: выходные порты не могут быть прочитаны, а входным не может быть присвоено значение. Сигналы создаются либо через объявления портов, либо через объявления сигналов. Порты создаются только через объявления портов. Допускается объявлять сигналы в архитектурах, объектах и блоках, а также использовать их в процессах и подпрограммах. Процессы и подпрограммы не могут объявлять сигналы для внутреннего использования. Можно использовать сигналы в выражениях. Значения назначаются сигналам с помощью операторов присвоения.

Объявления переменных

Пример 4. Объявления переменных ... variable A, B: BIT; variable INIT: NEW_BIT; ... Примечание. Переменные объявляются и используются только в процессах и подпрограммах, т.к. процессы и подпрограммы не могут объявлять сигналы для внутреннего использования.

Объекты VHDL Проекты, которые описываются в VHDL, состоят из объектов. Объект представляет собой один уровень иерархии проекта и может содержать полный проект, существующие аппаратные компоненты или VHDL-определенный объект. Каждый проект состоит из двух частей: спецификации объектов и архитектуры. Спецификация объекта является его внешним интерфейсом. Архитектура объекта - его внутреннее исполнение. У проекта есть только одна объектная спецификация (интерфейс), однако, он может иметь несколько архитектур (исполнений). Когда объект компилируется в аппаратный проект, то конфигурация определяет используемую архитектуру. Объектная спецификация и архитектура могут содержаться в различных исходных файлах VHDL или в одном файле. В примере 5 показана объектная спецификация простого логического элемента (2-входовой И-НЕ).

Пример 5. Объектная спецификация VHDL ... entity NAND2 is port(A, B: in BIT; -- Два входа, A и B Z: out BIT); -- Один выход, Z = (A and B)’ end NAND2; Примечание. В описаниях VHDL комментарии предваряются двумя дефисами (--). Все символы после этих дефисов до конца строки игнорируются FPGA Express. Единственным исключением из этого правила являются комментарии, которые начинаются с -- pragma или -- synopsys; эти комментарии - директивы FPGA Express. Ключевое слово entity объявляет объектную спецификацию, этот объект может использоваться другими объектами проекта. Внутренняя архитектура объекта определяет его функцию. В примерах 6, 7 и 8 показаны три различных архитектуры для объекта NAND2. Три примера определяют эквивалентное исполнение NAND2. После оптимизации и синтеза каждое исполнение приводит к одинаковой схеме, вероятно, к 2-входовому элементу И-НЕ выбранной технологии. Стиль описания архитектуры, используемый для данного объекта, зависит только от собственного предпочтения. В примере 6 показано, как объект NAND2 может быть выполнен с помощью двух компонентов из технологической библиотеки. Входы объекта A и B соединяются с элементом И U0, что дает промежуточный сигнал I. Сигнал I затем соединяется с инвертором U1, обеспечивая выход объекта Z.

Пример 6. Структурная архитектура для объекта NAND2 ... architecture STRUCTURAL of NAND2 is signal I: BIT;

component AND_2 -- Из технологии library port(I1, I2: in BIT; O1: out BIT); end component;

component INVERT -- Из технологии library port(I1: in BIT; O1: out BIT); end component; begin U0: AND_2 port map (I1 => A, I2 => B, O1 => I);

end STRUCTURAL; ... В примере 7 показано, как определить объект NAND2 с помощью его логической функции.

Пример 7. Архитектура потока данных для объекта NAND2 ... architecture DATAFLOW of NAND2 is begin Z <= A nand B; end DATAFLOW; ... Пример 8. RTL архитектура для объекта NAND2 ... architecture RTL of NAND2 is begin process(A, B) begin if (A = ’1’) and (B = ’1’) then Z <= ’0’; else Z <= ’1’; end if; end process; end RTL; ... Конструкции VHDL Высокоуровневые конструкции VHDL совместно работают для описания проекта. Описание состоит из: Объектов. Интерфейсы с другими проектами. Архитектур. Исполнения объектов проекта. Архитектуры могут определять связи с другими объектами через реализацию. Конфигураций. Привязки объектов к архитектурам. Процессов. Наборы последовательно выполняемых команд. Процессы объявляются внутри архитектур. Подпрограмм. Алгоритмы, которые могут быть использованы более чем в одной архитектуре. Блоков объявлений. Наборы объявлений, используемые одним или более проектами.

Определение проектов Высокоуровневые конструкции включают в себя: объектные спецификации (интерфейсы); объектные архитектуры (исполнения); подпрограммы.

Объектные спецификации Объектная спецификация определяет характеристики объекта, которые должны быть известны до того, как этот объект будет связан с другими объектами и компонентами. Например, перед тем, как соединить счетчик с другими объектами, нужно определить количество и типы его входов и выходов. Объектная спецификация определяет порты (входы и выходы) объекта и имеет следующий синтаксис:

entity entity_name is [ generic(generic_declarations); ] [ port(port_declarations); ] end [ entity_name ];

Другие объявления не поддерживаются в объектной спецификации.

Спецификации портов объекта Синтаксис объявлений port_declarations следующий:

port( [ port_name: mode port_type {; port_name: mode port_type}] ); где port_name - имя порта; mode - in, out, inout или buffer; a port_type - ранее определенный тип данных. Существуют четыре режима работы порта: in может осуществлять только чтение. Out может только присваивать значение. inout может осуществлять чтение и присваивать значение. Читаемое значение - это то, которое приходит на порт, а не то, которое ему назначается (если таковое имеется). buffer аналогичен режиму out, но может быть прочитан. Читаемое значение равно назначенному. Имеет только один источник (драйвер). В примере 9а показана объектная спецификация для 2-входового N-битового компаратора с битовой шириной по умолчанию, равной 8.

Пример 9а. Интерфейс для N-битового компаратора. -- Определяем объект (проект), называемый COMP, -- который имеет два N-битовых входа и один выход. ... entity COMP is generic(N: NTEGER:= 8);-- по умолчанию 8 бит port(X, Y: in BIT_VECTOR (0 to N-1); EQUAL: out BOOLEAN); end COMP; ...

Объектные архитектуры Каждая объектная архитектура определяет одно исполнение функции объекта. Архитектуру можно классифицировать в диапазоне от алгоритма (набор последовательных операторов внутри процесса) до структурного списка цепей (набор компонентных реализаций). Архитектура имеет следующий синтаксис:

architecture architecture_name of entity_name is { block_declarative_item } begin { concurrent_statement } end [ architecture_name ];

где architecture_name - имя архитектуры, а entity_name - имя реализуемого объекта. Элемент block_declarative_item может быть любым из следующих: предложение use; объявление подпрограммы; тело подпрограммы; объявление типа; объявление подтипа; объявление константы; объявление сигнала; объявление компонента. В примере 9б показано завершенное описание схемы трехбитового счетчика, объектная спецификация (COUNTER3) и архитектура (MY_ARCH). Этот пример также включает результирующую синтезированную схему.

Пример 9б. Реализация трехбитового счетчика library IEEE; -- обязательная часть, т.к. library synopsys; -- здесь описываются все use IEEE.std_logic_1164.all; -- используемые библиотеки use synopsys.attributes.all;

entity COUNTER3 is port (CLK: in bit; RESET: in bit; COUNT: out integer range 0 to 7); end COUNTER3;

architecture MY_ARCH of COUNTER3 is signal COUNT_tmp: integer range 0 to 7; begin process begin wait until (CLK’event and CLK = ’1’); -- ожидаем синхроимпульс if RESET = ’1’ or COUNT_tmp = 7 then -- Ck. для сброса или макс. числа COUNT_tmp <= 0; else COUNT_tmp <= COUNT_tmp + 1; -- продолжаем считать end if; end process; COUNT <= COUNT_tmp; end MY_ARCH; 4. Ход работы

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-26; просмотров: 297; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.223.106.232 (0.393 с.) |