Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Раздел 4. Логические устройства

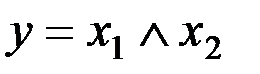

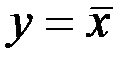

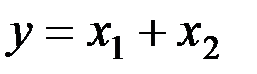

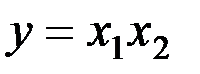

Тема 4.1. Логические элементы цифровой техники Двоичные логические элементы.

Тема 4.2. Комбинацион ные цифровые устройства Сумматоры. Сумматором называется комбинационное логическое устройство, предназначенное для выполнения операции арифметического сложения чисел, представленных в виде двоичных кодов. Сумматор является одним из основных узлов арифметико-логического устройства. Классификация сумматоров. Полусумматором называется устройство, предназначенное для сложения двух одноразрядных кодов, имеющее два входа и два выхода и формирующее из сигналов входных слагаемых сигналы суммы и переноса в старший разряд. Одноразрядным сумматором называется устройство, предназначенное для сложения двух одноразрядных кодов, имеющее три входа и два выхода, и формирующее из сигналов входных слагаемых и сигнала переноса из младших разрядов сигналы сумы и переноса в старший разряд. Многоразрядным сумматором называется устройство, предназначенное для сложения двух многоразрядных кодов, формирующее на выходе код суммы и сигнал переноса в случае, если результат сложения не может быть представлен кодом, разрядность которого совпадает с разрядностью кодов слагаемых. В свою очередь многоразрядные сумматоры подразделяются на последовательные и параллельные. В последовательных сумматорах операция сложения выполняется последовательно разряд за разрядом, начиная с младшего. В параллельных все разряды входных кодов суммируются одновременно.

Обозначение одноразрядного сумматора.

Ai,Bi – цифры слагаемых; Рi – перенос; Si – сумма; Рi+1 – перенос в следующий разряд. Таблица функционирования

Выходы | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Аi | Bi | Pi | Si | Pi+1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 0 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 0 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 0 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Дешифраторы и шифраторы являются комбинационными элементами: потенциалы на их выходах зависят от сиюминутного состояния входов, с их изменением меняется и ситуация на выходах; такие элементы не сохраняют предыдущее состояние после смены потенциалов на входах, т. е. не обладают памятью. Преимущественно дешифраторы используют для выбора того или иного компонента из их множества. Различают дешифраторы полные и неполные. Полные дешифраторы реагируют на все входные коды, неполные — на коды, величина которых не превосходит некоторого заранее установленного значения. Выходы дешифраторов бывают прямые и инверсные. На выходах шифратора устанавливается код, соответствующий номеру возбужденного входа. Промышленность производит приоритетные и неприоритетные шифраторы. В приоритетных шифраторах входы имеют разный приоритет. Возбужденный вход с большим приоритетом подавляет действие прежде возбужденного и устанавливает на выходах код, соответствующий своему значению.

Классификация дешифраторов и шифраторов

Дешифратор (decoder) — это комбинационное устройство, позволяющее распознавать числа, представленные позиционным n-разрядным кодом. Если на входе дешифратора n-разрядный двоичный код, то на его выходе код «1 из N». В кодовой комбинации этого кода только одна позиция занята единицей, а все остальные — нулевые. Например, код «1 из N», содержащий четыре кодовые комбинации, будет представлен следующим образом:

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

Такой код называют унитарным, поэтому дешифратор является преобразователем позиционного двоичного кода в унитарный. Так как возможное количество чисел, закодированных n-разрядным двоичным кодом, равно количеству наборов из n аргументов (N=2n), то дешифратор, имеющий n входов, должен иметь 2n выходов. Такой дешифратор называют полным. Если часть входных наборов не используется, то дешифратор называют неполным, и у него число выходов меньше 2n. Таким образом, в зависимости от входного двоичного кода на выходе дешифратора возбуждается только одна из выходных цепей, по номеру которой можно распознать входное число. Дешифратор выбирают так, чтобы число его входов соответствовало разрядности поступающих двоичных кодов. Число его выходов равно количеству различных кодов этой разрядности. Каждому цифровому коду на входах дешифратора (рис.2, а,б) соответствует лог.1 (или лог.0) на соответствующем выходе. Иными словами, каждый входной код адресует соответствующий выход, который при этом возбуждается. Поэтому входы дешифратора часто называют адресными. Стоящие возле входов цифры (1,2,4,...) показывают как соотносятся «веса» разрядов поступающего двоичного числа. Выходы дешифратора оцифрованы десятичными числами. Возбуждается тот выход, номер которого равен «весу» входного кода, разряды которого имеют обозначенные «веса», т.е. дешифратор расшифровывает (дешифрирует) число, записанное в двоичном коде, представляя его лог. 1 (лог. 0) на соответствующем выходе. Так, выход 5 возбуждается при входном коде 101, выход 6 - при входном коде 110 и т.д. Удобно представлять, что выход дешифратора отображает возбудивший его входной код.

|

|

Дешифратор с инверсным входом V

Вход V является входом разрешения работы. Если он инверсный (обозначен кружком как на рис.), то для функционирования дешифратора на нем должен быть лог. 0 (достаточно этот вход соединить с общим проводом — землей). Прямой вход V через резистор соединяется с источником питания. Наличие входа разрешения расширяет функциональные возможности микросхемы.

Неполный дешифратор выбирают, когда некоторые значения адресных кодов не отражают физической реальности. Так, например, дешифратор, предназначенный для фиксации двоичных кодов десятичного разряда (в нем могут быть цифры 0, 1, 2... 9), должен иметь четыре входа (910 отображается как 10012). Однако комбинации, большие 10012 отображают не цифру, а число, и поэтому (хотя и могут появляться на входах) не должны фиксироваться на выходах, число которых может не превышать десяти.

Основу структуры дешифратора могут составлять элементы И; выход каждого из них является выходом дешифратора. Если этот выход должен быть возбужден, то на входах элемента И должны собираться лог.1. При этом разряды входного кода, в которых присутствуют единицы, должны поступать на входы элемента И непосредственно, а нулевые разряды должны инвертироваться.

Дешифраторы применяют для расшифровки адресов ячеек запоминающих устройств, высвечивания букв и цифр на мониторах, индикаторах и других устройствах. Чаще всего они являются встроенными в БИС, как, например, в полупроводниковых запоминающих устройствах, однако они выпускаются и в виде ИС среднего уровня интеграции.

или

или

и

и