Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Устройство, назначение и принцип действия Т – триггера.

Т-триггер называется триггером со счётным входом, т.к. переключается в противоположное состояние только при поступлении на информационный вход сигнала “1” (т.е. считает логические “1”). Т-триггер является тактируемым триггером, информационным входом которого является вход С. Выход Т-триггера переключается при каждом поступлении синхронизирующего сигнала СВС. Частота сигнала на выходе в два раза меньше, чем входная. Т-триггер строится на основе JK-триггера, на входах J и К которого поддерживается логический уровень единицы (рис. 5).

Рисунок 5 Таблица истинности, схема и обозначение Т-триггера

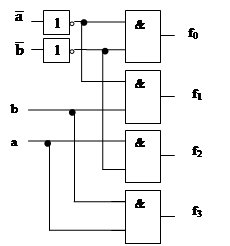

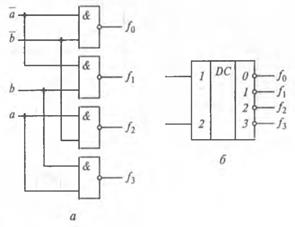

13. Устройство, назначение, система логических функций и принцип действия дешифратора 4х1. Дешифратор (DC - decoder) предназначен для преобразования входного кода в сигнал только на одном выходе. Количество входов равно n и представляет собой двоичное число - двоичный код, а количество выходов равно N, причём N = 2n. Такой дешифратор называется полным. При поступлении двоичного кода на вход на его выходе, номер которого равен числу на входе, появляется сигнал "1". Нумерация выходов начинается с 0. Например, если на вход поступил сигнал 101, то на выходе №5 возникнет "1", а на остальных будут "0". Дешифраторы используются в устройствах памяти для выбора заданной ячейки по её адресу. ДвухвходовыйDC реализует логические функции:

Рисунок 1 Схема дешифратора на ЛЭ "И" и "НЕ"

Из системы логических функций следует, что дешифратор может быть построен на логических элементах "И" и "НЕ. Для двухвходового DC схема устройства примет вид – рис. 1. Логика работы двухвходового DC приведена в табл. 1 – любая комбинация на входе декодируется в сигнал на одном из выходов.

Таблица 1

На практике часто используется DC с инверсными выходами. Инверсный выход означает, что выходным сигналом на комбинацию на входе будет не "1", а "0", при этом на остальных выходах будут "1". Функциональная схема DC на два входа с инверсными выходами и его схемное обозначение приведены на рис. 2.

Рисунок 2 Дешифратор на два входа с инверсными выходами

а – функциональная схема, б – графическое обозначение

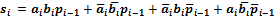

14. Устройство, назначение, система логических уравнений и принцип действия одноразрядного сумматора. Одноразрядный сумматор. Сумматоры выполняют арифметическое сложение чисел, которое производится, начиная с младших разрядов чисел. В каждом разряде сумматора выполняются одинаковые действия, т.е. суммируются две двоичные цифры в соответствии с правилами сложения двоичных цифр плюс возможный перенос из младшего разряда:

1 1 1 – перенос из младшего разряда pi-1. 0 0 1 1 - первое слагаемое ai.; 0 1 1 1 - второе слагаемо bi.; 1 0 10 - сумма si. с переносом pi

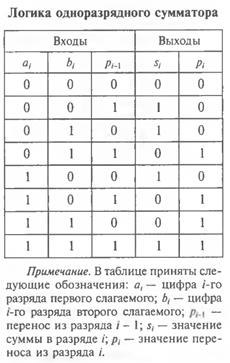

При сложении двух единиц возникает единица переноса в старший разряд, которую нужно учесть при сложении цифр следующего разряда. Поэтому в каждом разряде сумматора необходимо предусмотреть возможность суммирования трех цифр: двух цифр слагаемых и единицы переноса из младшего разряда. Таким образом, сумматор для сложения многоразрядных чисел можно построить из одинаковых схем, каждая из которых выполняет сложение двух цифр слагаемых и переноса из младшего разряда. Такая схема называется одноразрядным сумматором. Одноразрядный сумматор представляет собой комбинационную схему с тремя входами и двумя выходами (рис. 1), логика работы которой соответствует следующей таблице истинности (табл. 1). Как известно, уравнения выходов логических устройств записываются как сумма (дизъюнкция)произведений (конъюнкций) входных сигналов для тех строк таблицы состояний, в которых выходная функция = 1 В соответствии с таблицей истинности (табл. 1)канонические уравнения одноразрядного сумматора примут вид:

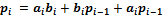

Уравнение (1) не минимизируется, для минимизации функции pi добавляются ещё два слагаемых Таблица 1

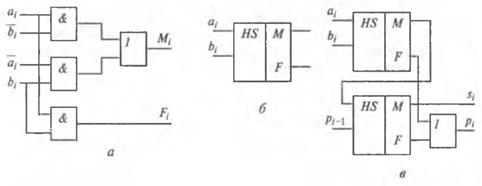

Рисунок 1. Одноразрядные сумматоры: а — схема сумматора на элементах И —НЕ; б — схема сумматора с использованием элементов сложения по модулю 2; в — условное графическое обозначение (УГО)

15. Устройство, назначение, система логических уравнений и принцип действия одноразрядного полусумматора.

Полусумматор. Полусумматором, или одноразрядным сумматором на два входа, называется схема с двумя входами и двумя выходами, которая реализует следующие функции:

Fi = ai bi

где М i- значение суммы в данном разряде; Fi - значение переноса из данного разряда; ai и bi - одноименные разряды слагаемых.

Полусумматоры могут быть использованы для построения схем одноразрядных сумматоров на три входа, а также схем ускорения умножения. Варианты схемы полусумматора и его УГО приведены на рис. 2

Рис. 2 Полусумматор: а — схема полусумматора; б — УГО; в — схема одноразрядного сумматора на основе полусумматоров

|

||||||

|

Последнее изменение этой страницы: 2021-03-09; просмотров: 119; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.134.90.44 (0.008 с.) |

(1)

(1)

и выносятся за скобки общие сомножители, т.е. используются тождества Булевой алгебрыА+А+…+А = А и

и выносятся за скобки общие сомножители, т.е. используются тождества Булевой алгебрыА+А+…+А = А и  .

.

М i = aibi

М i = aibi