Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Интегрированные прикладные системы. Им. Р. Е. АлексееваСтр 1 из 20Следующая ⇒

Им. Р. Е. Алексеева Кафедра «Ядерные реакторы и энергетические установки»

КОНСПЕКТ ЛЕКЦИЙ по дисциплинам: «Информационно-компьютерные технологии в физико-техническом эксперименте», “Интегрированные прикладные системы»

Н.Новгород, 2016 г. 1 Интегрированные прикладные системы 4 1.1 Классификация вычислительных устройств 4 2 История развития вычислительной техники 5 2.1 История развития ПК 7 3 История развития операционных систем (ОС) 8 3.1 Кодирование данных в ПК 8 3.2 Символьный монитор 9 3.3 Функциональная схема вычислительного устройства 9 4 Формы представления данных в вычислительных системах 10 4.1 Двоичная система 10 4.2 Системы исчисления 10 5 Выходной каскад логического элемента 12 5.1 Типы логических элементов 12 5.2 Принцип работы выходного каскада логического элемента 13 5.3 Конкуренция сигналов 14 6 Современная интерпретация принципа Фон-Неймана 14 6.1 Принцип работы ВУ 14

6.2 Особенности тактирования ВУ с автономным источником питания 17 7 Процесс записи в ВУ 18 7.1 Расходование энергии 18 8 Процесс чтения в ВУ 20 9 Процессор 20 9.1 Характеристики процессора 21 9.2 Архитектура процессора 21 9.3 Основные элементы процессора 25 10 Компьютерная память 26 10.1 Классификация типов памяти 26 10.2 Метод прямого доступа к памяти 28 11 Прерывание 28 11.1 Виды прерываний 29 11.2 Приоритизация прерываний 30 11.3 Маскирование прерываний 30 12 Таймер 30

12.1 Формирование периода по совпадению регистра кода 32 12.2 Сторожевой таймер 33 13 Аналоговые устройства 34 13.1 Аналоговый компаратор 34 13.2 АЦП 36 13.3 ЦАП 36 13.4 Методы преобразования 39 14 Платы ввода/вывода данных ПК 44 15 Методы передачи сигналов и защита от помех 46 15.1 Виды помех 46 15.2 Методы передачи сигналов 48 16 Стандарт NAMUR 52 17 Гальваническая развязка 54 18 Интерфейсы 56 18.1 Параллельный интерфейс 57 18.2 Последовательный 59 18.3 Промышленный интерфейс 63 22 Протоколы обмена данными 64 19.1 Полезность ASCII-кода 65 19.2 Категории команд 66 19.3 Примеры протоколов 67 23 Режимы работы вычислительных систем 70 24 Методы программирования вычислительных устройств 73 21.1 Классификация ПО 73

21.2 Классификация языков программирования 74 25 Виртуальные приборы 74 26 Микроконтроллеры 77 27 Структура и основные принципы работы сети Интернет 79 27.1 Адресация в сети интернет 81 27.2 IP-адресация 81 27.3 Понятие маски подсети 83 27.4 Доменные имена 83 27.5 Как работают серверы DNS 84 28 Универсальная последовательная шина 85

История развития ПК В 1974 году фирма INTEL выпустила 8-разрядный процессор INTEL 8080. Российским аналогом этого процессора стал 580ИК80. Он имел 16-разрядную шину адресов, позволявшую адресоваться к 216 ячейкам, и 8-разрядная шина данных. Характеристики: 8 разрядная шина данных Шина данных – число параллельных разрядов.

В 1976 году INTEL выпустила 16-разрядный процессор INTEL 8086. Появился INTEL 80286 (i286), который имел 24-битную адресацию и 16-разрядную шину данных, а также обладал 16Мб адресного пространства. На основе процессора INTEL 8086 IBM разработала ПК (системный блок и сопутствующая периферия). Процессор INTEL 80386 появился в 1985 году и привнёс 32-битную адресацию, позволившую использовать до 4Гб оперативной памяти и поддержку механизма виртуальной памяти. За годы существования микропроцессоров было разработано множество различных их архитектур. Многие из них (в дополненном и усовершенствованном виде) используются и поныне. Например, Intel x86, модифицированный вначале в 32-битный IA-32, а позже в 64-битный x86-64 (Intel EM64T). Процессоры архитектуры x86 вначале использовались только в персональных компьютерах компании IBM, но в настоящее время всё более активно используются во всех областях компьютерной индустрии, от суперкомпьютеров до встраиваемых решений.

Популярность и широкое распространение компьютеров IBM было достигнуто благодаря применению принципа открытой архитектуры, который заключался в разделении элементов компьютера на стандартные устройства, связанные между собой стандартными интерфейсами. Это позволило частично модернизировать и расширять возможности компьютера без замены его всего целиком. К ним относятся: материнская плата, блок питания, дополнительная память, порты ввода/вывода, интерфейсы для подключения внешних носителей информации: флоппи, HARD диска, CD диска. Достоинства открытой архитектуры: · возможность создавать взаимозаменяемые устройства с большими возможностями; · на рынке появилось множество фирм, специализирующихся на выпуске подобных устройств. Это привело к ускорению прогресса в развитии вычислительной техники. Кодирование данных в ПК Первые устройства вывода данных использовали ASCII-код. Таблица ASCII символов

Он используется для: - передачи данных по стандартным интерфейсам; - вывода данных на символьный монитор и на печатные устройства. Символы ASCII А-41h

1−31h … 9-39h @-40h Enter-0Dh Символьный монитор

ASCII код до сих пор используется для передачи данных в промышленных интерфейсах. Он удобен, поскольку позволяет разделять собственно данные и управляющие символы (служебные символы от информативных). Например, если компьютер передает устройству конечную команду, то обычно она начинается с признака – команды (@-40h). Конец передачи команды определяется финализатором (Enter-0Dh). Принимающее устройство анализирует сигнал, и если встречается анализатор, то только тогда приступает к декодированию и исполнению команды. Двоичная система Двоичный код – активное значение в одном разряде может принимать только 2 значения: «0» или «1». Максимальное число, которое может быть записано с помощью 1 байта = 256 Системы исчисления

Система исчисления — символический метод записи чисел, представление чисел с помощью письменных знаков. Системы исчисления подразделяются на позиционные, непозиционные и смешанные. В вычислительной технике нашли применение позиционные системы исчисления. Позиционная система исчисления - система исчисления, в которой значение каждого числового знака (цифры) в записи числа зависит от его позиции (разряда). Позиционная система счисления определяется целым числом D>1, называемым основанием системы счисления. Система счисления с основанием D также называется В вычислительных устройствах для записи заданных значений применяют двоично-десятичное кодирование десятичных цифр (Binary-Coded Decimal), при этом для одной двоично-десятичной цифры отводится четыре двоичных разряда (двоичная тетрада). Также используется шестнадцатеричная система исчислений, в которой для записи одного значения аналогично используют 4 разряда. Если суммарное значение превышает 9, то используются буквы латинского алфавита A-F. При объединении 4-х разрядов в один знак получим младший и старший разряд. dec → bin, hex При переводе числа из десятичной системы счисления в произвольную применяется метод последовательного деления deс-числа на основание произвольной системы. Остаток от деления записывается как младший бит, а частное (если оно не равно 0) вновь подвергается делению на основание произвольной системы. Каждый следующий остаток записывается в разряд нового числа в направлении от младшего разряда к старшему. dec ← bin, hex Для перевода числа в десятичную систему счисления из произвольной необходимо представить его в виде суммы произведений степеней основания произвольной системы счисления на соответствующие цифры в разрядах числа произвольной системы. bin → hex Для перевода многозначного двоичного числа в шестнадцатеричную систему нужно разбить его на тетрады справа налево и заменить каждую тетраду соответствующей шестнадцатеричной цифрой из вышеприведённой таблицы перевода. Таблица и правила перевода чисел из одной системы исчисления в другую

Dec |

Hex | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 8 | 4 | 2 | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 8 | 4 | 2 | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 1 | 1 | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 0 | 2 | 2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 1 | 3 | 3 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 0 | 4 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 1 | 5 | 5 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 0 | 6 | 6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 1 | 7 | 7 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 0 | 8 | 8 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 1 | 9 | 9 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 0 | 10 | A | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 1 | 11 | B | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 0 | 12 | C | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 1 | 13 | D | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 0 | 14 | E | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 1 | 15 | F |

Общий принцип:

1. Берется число хххх делится на подходящий делитель, так, чтобы был не нулевой результат;

2. Результат умножается на делитель;

3. Из хххх вычитается результат операции 2;

4. С остатком выполняются аналогичные операции с 1 по 4;

5. Последний остаток (<16) в младшие разряды.

bin ← hex

Для перевода числа из шестнадцатеричной системы в двоичную нужно заменить каждую его цифру на соответствующую тетраду из вышеприведённой таблицы перевода.

Пример:

Запишем 100deс:

|

Dec

| D 7 | D 6 | D 5 | D 4 | D 3 | D 2 | D 1 | 0 |

| 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 | |

| 8 | 4 | 2 | 1 | 8 | 4 | 2 | 1 | |

| → bin | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| → hex | 100/16= 6, остаток 4 | |||||||

Так, 100dec = 01100100bin = 64hex.

Запишем 55hex:

|

| 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

| 8 | 4 | 2 | 1 | 8 | 4 | 2 | 1 | |

| → bin | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| → de с | 5 · 20 + 5 · 24 = 85 dec | |||||||

Так, 55hex = 01010101bin = 85dec.

Запишем 0A34hex:

|

| 2 15 | 2 14 | 2 13 | 2 12 | 2 11 | 2 10 | 2 9 | 2 8 | 2 7 | 2 6 | 2 5 | 2 4 | 2 3 | 2 2 | 2 1 | 2 0 |

| 8 | 4 | 2 | 1 | 8 | 4 | 2 | 1 | 8 | 4 | 2 | 1 | 8 | 4 | 2 | 1 | |

| hex | 0 | A | 3 | 4 | ||||||||||||

| → bin | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| → de с | 0·212 + A·28 + 3·24 + 4·20 = 2612 dec | |||||||||||||||

Так, 0A34hex = 0000101000110100bin = 2612 dec.

- 1 разряд - это 1 бит информации;

- 8 разрядов = 1 байт;

- 8 разрядов и более составляют слово.

Допустим, есть переменная А.

Для хранения 1 байта она должна иметь символьный тип char:

char 55

0x55, // hex

0 1010101 b // bin

Если переменная имеет более 56 цифр, то она должна иметь целочисленный тип int или longint:

int // 0÷216 = 65535

longint // 0÷232 = 4294967296

Переменные вещественных чисел описываются типами float или double float (точность последнего в два раза больше первого и составляет 15 значащих цифр). Float позволяет хранить 4 байта информации, тогда как double float – 8 байт.

В большинстве случаев тип double float является наиболее удобным: ограниченной точности чисел float во многих случаях попросту недостаточно. Причина, по которой тип float все ещё используется, - экономия памяти при хранении, что важно при работе с большими массивами вещественных чисел.

Типы логических элементов

Логический элемент представляет собой устройство, предназначенное для обработки информации в цифровой форме.

Логический элемент представляет собой устройство, предназначенное для обработки информации в цифровой форме.

входы A выход

B

1. Инвертор (НЕ)

|

2. Логическое умножение (И)

А 0 1 0 1

А 0 1 0 1

В 0 0 1 1

Вых. 0 0 0 1

3. Логическое сложение (ИЛИ)

А 0 1 0 1

А 0 1 0 1

В 0 0 1 1

Вых. 0 1 1 1

4. Исключающее (ИЛИ НЕ)

А 1 0 1 0

А 1 0 1 0

В 0 1 1 0

Вых. 1 1 0 0

Конкуренция сигналов

В современных логических элементах выходной каскад имеет защиту от перегрузки по току, исключающую 4-ю комбинацию логического элемента и обеспечивающую некий средний промежуточный потенциал на выходе. Для исключения конкуренции сигналов выходы устройств, адрес которых не установлен, находятся в z-состоянии.

До момента  к выходу подавалась 1 с элемента ЭЛ1. В момент

к выходу подавалась 1 с элемента ЭЛ1. В момент  выход ЭЛ1 был выключен, но включился ЭЛ3 и на шину стал подаваться 0 (т.е. до момента времени

выход ЭЛ1 был выключен, но включился ЭЛ3 и на шину стал подаваться 0 (т.е. до момента времени  подавался логический 0). В момент

подавался логический 0). В момент  ЭЛ3 не выключен и к шине подключается выход ЭЛ1. За счет ограничений по выходному току элементы из строя не выходят, но ток идет повышенный. На шине возникает промежуточное значение (между 0 и 1) – это состояние называется конкуренцией сигналов. (Возникает тогда, когда 2 и более выходов активны). При этом вход может неадекватно воспринять образовавшийся на шине уровень. Т.е., 0 вместо 1 и 1 вместо 0. Это может повлечь определенные последствия. Чтобы исключить конкуренцию сигналов, каждый элемент ВС имеет свой уникальный номер (адрес) и откликается только на него.

ЭЛ3 не выключен и к шине подключается выход ЭЛ1. За счет ограничений по выходному току элементы из строя не выходят, но ток идет повышенный. На шине возникает промежуточное значение (между 0 и 1) – это состояние называется конкуренцией сигналов. (Возникает тогда, когда 2 и более выходов активны). При этом вход может неадекватно воспринять образовавшийся на шине уровень. Т.е., 0 вместо 1 и 1 вместо 0. Это может повлечь определенные последствия. Чтобы исключить конкуренцию сигналов, каждый элемент ВС имеет свой уникальный номер (адрес) и откликается только на него.

Все устройства вычислительной системы подключаются к процессору параллельно по шине данных (ШД). Выбор устройства, с которым процессор будет осуществлять обмен данными (чтение/запись) осуществляется установкой уникального номера устройства на ША. [для каждого устройства – свой единственный номер; задается адрес устройства ] А также, для процесса обмена необходима подача управляющих сигналов по шине управления (ШУ).

Такой метод обмена позволяет исключить конкуренцию с устройствами, с которыми не производится обмен данными. В качестве устройства может выступать память, а также регистры портов ввода/вывода.

Источники тактирования

1. Внешний высокочастотный кварцевый генератор;

2. Внешний низкочастотный кварцевый генератор (32768 Гц). Этот же генератор тактирует часы реального времени;

3. Внутренний встроенный генератор.

В слип-моде процессор работает с источниками 2 и 3. Дополнительными мерамиэкономии заряда аккумулятора являются:

- отключение подсветки дисплея;

- отключение части периферийных устройств.

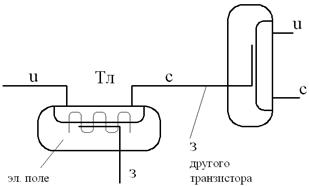

Расходование энергии

Если затвор (З) насыщен электронами, то в области между истоком (И) и стоком (С) возникает запирающее электрическое поле, и наоборот.

Чем чаще идёт ток и чаще меняется напряжение на затворе (З), тем выше потребляемая энергия.

Чем чаще идёт ток и чаще меняется напряжение на затворе (З), тем выше потребляемая энергия.

Проводник имеет сопротивление, следовательно, потребляемая мощность обусловлена ненулевым сопротивлением нанопроводников, и, как следствие, выделением тепла при протекании тока (поэтому необходимо использование кулеров и воздушных охладителей).

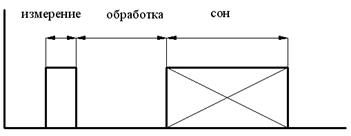

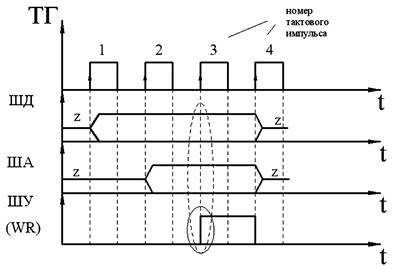

На рисунке показан процесс записи из процессора в какое-либо устройство (WR – сигнал “write” ШУ).

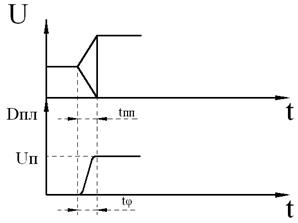

Покажем переходный процесс изменения состояния разряда шины – время, необходимое для того, чтобы открылся/закрылся ключ в выходном каскаде логического элемента.

tпп - время установки комбинации на шине, необходимое для того, чтобы все ключи у логических элементов открылись или закрылись.

tф - длительность фронта импульсов.

Время переходного процесса ~  …

…  с (например, время за которое меняется 0 на 1)

с (например, время за которое меняется 0 на 1)

1. По переднему фронту 1 тактового импульса ТГ процессор устанавливает на ШД данные, которые записываются (двоичную комбинацию записываемого кода – База данных). До этого шина находилась в нейтральном состоянии (z-состоянии) для исключения конкуренции сигналов.

2. По переднему фронту 2 импульса ТГ процессор устанавливает на ША двоичную комбинацию номера УВВ (устройство ввода/вывода) или ячейки памяти, в которую происходит запись данных.

3. По переднему фронту 3 тактового импульса ТГ, процессор устанавливает сигнал «WR» - импульс записи – на ШУ, который производит запись в ячейку, адрес которой установлен на ША.

4. По переднему фронту 4 тактового импульса ТГ процессор снимает 2-ичные комбинации на ША и ШД и переводит их в нейтральное z-состояние, убирает сигнал “write” на ШУ, а также формирует задний фронт импульса записи.

Вопрос. Когда нет обмена данных, процессор держит ШД в нейтральном состоянии.

Ответ. Существует другой контроллер, который может выполнять эти функции (с шинами ШД и ША). В это время процессор «отдыхает».

Переходный процесс – изменение уровня с одного состояния на другое, изменение состояния на шине.

Время переходного процесса – время, за которое разряд шины изменяет своё состояние с одного на другое; оно зависит от электроники и ёмкости шины.

Все схемы основаны на полевых транзисторах.

Когда электрическое поле есть, транзистор не проводит (т.е. 0). Если нет, то транзистор проводит (т.е. 1). Современные ВУ основаны на базе полевых транзисторов, которые потребляют ток в момент открывания/закрывания (переходные процессы).

Процесс чтения в ВУ

Процесс чтения представляет собой процесс, обратный записи.

1. По переднему фронту 1 тактового импульса ТГ процессор устанавливает двоичную комбинацию адреса (номера) ячейки памяти или УВВ, из которой будет производиться чтение на ША.

2. По переднему фронту 2 тактового импульса ТГ процессор формирует передний фронт импульса чтения «RD» на ШУ. В ответ на это устройство выставляет содержимое своей ячейки на ШД.

3. По переднему фронту 3 тактового импульса ТГ процессор записывает комбинацию данных на ШД в свою ячейку (свой регистр).

По заднему фронту 3 тактового импульса процессор формирует задний фронт импульса «чтения».

4. По переднему фронту 4 тактового импульса, процессор переводит ША в нейтральное состояние, снимает сигнал “read”, и устройство, с которого производится чтение, переводит выходы, подключённые к ШД, в нейтральное z-состояние.

ША, ШД – элементы параллельного интерфейса, а не последовательного. Последовательный интерфейс используется в интернете.

ША процессора в отсутствии акта обмена данными поддерживается в z-состоянии для того, чтобы ей мог воспользоваться контроллер DMA (контроллер прямого доступа к памяти). Последний применяется для пересылки массивов данных из одной адресной области в другую без участия процессора и позволяет делать эту операцию быстрее и эффективнее, чем микропроцессор.

Процессор

Процессор – один из основных компонентов ВУ, который выполняет логические и арифметические операции по заданной программе, а также координирует работу компонентов ВУ.

Виды процессоров:

1. Центральный процессор (CPU) – это основной процессор в ВУ. (выполняет максимальное количество команд)

CPU (Central Processing Unit) – это электронный блок либо интегральная схема (микропроцессор), исполняющая машинные инструкции (код программ), главная часть аппаратного обеспечения компьютера или программируемого логического контроллера.

Для разгрузки CPU существуют разгрузочные процессоры. Например, GPU (графический процессор) – выполняет графические функции по обработке графической информации. Устанавливается на видеокарте или материнской плате.

2. Математический сопроцессор – служит для выполнения математических вычислений (для чисел с плавающей точкой), а также для вычислений специальных функций (например, тригонометрических, логарифмирования и т. п.).

В мощных ВУ сопроцессор включён в состав CPU. Процессоры, не имеющие в своём составе математический сопроцессор (микроконтроллер), выполняют его функции за счёт специальных подпрограмм CPU, на что тратится много машинных тактов и занимает много времени.

3. Микроконтроллер (МК) – устройство, которое объединяет в одном кристалле процессор, а также все необходимые вычислительные элементы в ВУ:

- память программ;

- память данных;

- порты ввода/вывода;

- таймеры;

- ТГ: внутренний, внешний, высокочастотный кварцевый, внешний низкочастотный кварцевый – рабочая частота 32768 Гц (часовой кварцевый генератор 32 кГц);

- интерфейсы;

- аналоговый компаратор;

- аналогово-цифровой преобразователь (АЦП);

- цифро-аналоговый преобразователь (ЦАП);

- некоторые уникальные редкоиспользуемые элементы и т.д.

К классу микроконтроллеров относят DSP (digital signal processor) (цифровой сигнальный процессор) – микроконтроллер, ориентированный на цифровую обработку аналоговых сигналов (обычно в масштабе реального времени) и применяющийся в измерительных системах.

4. Сетевой процессор (NP) – это процессор, размещённый в сетевых устройствах, выполняющий операции по передаче данных по сети; используется в сетевых картах, маршрутизаторах, коммуникаторах (передача больших массивов по сетям).

5. Аудиопроцессор (ASP) – предназначен для обработки звуков, музыки, цифровой фильтрации и т.д.; применяется в специальной аудиоаппаратуре.

6. Видеопроцессор – предназначен для выполнения функций по обработке графической информации; используется в видеокартах.

Характеристики процессора

1) разрядность;

2) архитектура процессора;

3) максимальная тактовая частота – максимальная частота, на которой может работать процессор;

4) производительность, определяется в флопах:

1 флоп – 1 операция над числами с плавающей точкой в 1 секунду.

Процессор в своём ядре имеет математический вычислитель, который «заточен» на подобного рода работу. Это эффективно, а значит, выше производительность.

5) Энергопотребление – зависит отархитектуры, тактовой частоты и от используемой технологии производства.

6) Технология производства– определяется длиной волны лазера для выжигания кристаллов кремния; относится к производству транзисторов.

Архитектура процессора

Архитектура Фон-Неймана

Архитектура фон Неймана — широко известный принцип совместного хранения команд и данных в памяти компьютера. Вычислительные системы такого рода часто обозначают термином «машина фон Неймана», однако соответствие этих понятий не всегда однозначно. В общем случае, когда говорят об архитектуре фон Неймана, подразумевают принцип хранения данных и инструкций в одной памяти.

Архитектура фон Неймана

Общая структура фон-Неймановского процессора.

Принципы фон Неймана

Принцип однородности памяти

Команды и данные хранятся в одной и той же памяти и внешне в памяти неразличимы.

Принцип адресности

Структурно основная память состоит из пронумерованных ячеек, причём процессору в произвольный момент доступна любая ячейка.

Принцип программного управления

Все вычисления, предусмотренные алгоритмом решения задачи, должны быть представлены в виде программы, состоящей из последовательности управляющих слов — команд.

Принцип двоичного кодирования

Согласно этому принципу, вся информация, как данные, так и команды, кодируются двоичными цифрами 0 и 1. Каждый тип информации представляется двоичной последовательностью и имеет свой формат.

Гарвардская архитектура

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются:

1. Программы и данные хранятся в физически разных различных областях памяти.

2. Канал инструкций и канал данных также физически разделены.

-30h

-30h

64hex

64hex