Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

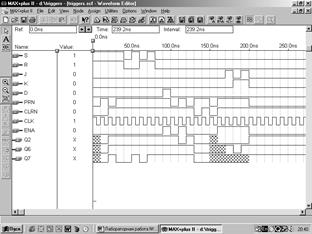

Результати програмної реалізації тригерів

На рис. 7.1.11 зображено вікно сигнального редактору проекту “triggers”.

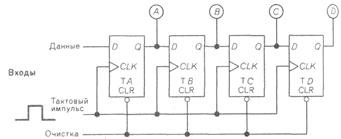

Рис.7.1.11. Результати тестування RS-, D-, JK-тригерів Теоретичні відомості про регістри Послідовні регістри зсуву Схема одного з типових регістрів зсуву подана на рис. 7.2.1. Цей регістр реалізований на 4 D-тригерах. Такий регістр має назву 4-розрядний регістр зсуву, оскільки він дозволяє зберігати 4 двійкових розряди даних А, B, C, D.

Рис.7.2.1. 4-розрядний послідовний регістр зсуву

За допомогою табл. 7.2.1 і рис. 7.2.1 ми маємо можливість спостерігати за роботою цього пристрою. Спочатку очистимо регістр (встановимо рівні логічного нуля на його виходах А, B, C, D). Для цього потрібно подати логічний 0 на вхід очищення CLR. Отриманому стану регістра зсуву відповідає рядок 1 табл. 7.2.1 До приходу тактового імпульсу виходи регістру залишаються в стані 0000. Подамо перший імпульс на синхронізуючий вхід CLK; індикатор покаже число 1000 (рядок 3 в табл. 7.2.1), оскільки на тактовому імпульсі логічна 1 з інформаційного входу тригера TA переноситься на його логічний вихід Q. Тепер при наявності логічної 1 на інформаційному вході регістру ця одиниця з кожним тактовим імпульсом вводиться в розряд А, а введені раніше одиниці зсуваються на одну позицію (розряд) вправо (тактові імпульси 2 і 3 в табл. 7.2.1). Таким самим чином при подачі на інформаційний вхід логічного 0 цей нуль при кожному тактовому імпульсі вводиться в розряд А, а введені раніше одиниці та нулі зсуваються вправо (тактові імпульси 4-8 в табл. 7.2.1). Перед приходом тактового імпульсу 9 на інформаційному вході встановлюється 1, а перед приходом імпульсу 10 цей вхід повертається до 0. В час дії тактових імпульсів 9-13 введена в регістр на імпульсі 9 одиниця буде зміщуватись на індикаторі вправо. Рядок 15 в табл. 7.2.1 показує, на імпульсі 13 ця одиниця покидає крайній правий розряд регістру зсуву і втрачається.

Табл.7.2.1. Робота 4-розрядного регістру зсуву

Нагадаємо, що D-тригер називають також тригером з затримкою. Він просто передає інформаційний сигнал з входу D на вихід Q з затримкою на один такт.

Прилад, схема якого приведена на рис. 7.2.1 має назву послідовного регістру зсуву. Термін “послідовний” відображає той факт, що в цей регістр дані вводяться порозрядно. Наприклад, щоб ввести в регістр двійкову комбінацію 0111 треба пройти всю послідовність станів від рядка 1 до рядка 6 в табл. 7.2.1. Послідовне завантаження 4-бітової комбінації 0111 в послідовний регістр відбувається за 5 тактів (рядок 2 можливо виключити). Інший спосіб завантаження регістру – паралельне (або розширене) завантаження, при якому всі інформаційні біти вводяться в регістр одночасно “за командою” одного тактового імпульсу. Регістр зсуву на рис. 7.2.1 можливо трансформувати в 5-розрядний, додав до схеми ще один D-тригер. Регістри зсуву частіше бувають 4-, 5- або 8-розрядними. В них можливо використання не тільки D-тригеру, але й тригерів іншого типу (наприклад, JK-тригера, або синхронних RS-тригерів).

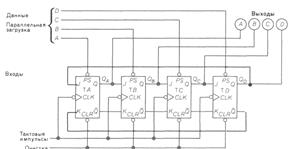

Паралельні регістри зсуву Послідовний регістр зсуву, робота якого описана вище має два суттєві недоліки: він дозволяє вводити тільки по одному біту інформації на кожному тактовому імпульсі і, крім того, кожний раз при зсуві вправо втрачається крайній правий біт. На рис. 7.2.2 показана схема 4-розрядного паралельного кільцевого регістру. Входи A, B, C, D вданому приладі є інформаційними.

Рис. 7.2.2. 4-розрядний паралельний кільцевий регістр зсуву

Цю систему можливо спорядити ще однією корисною характеристикою – можливістю кільцевого переміщення інформації, коли дані з входу приладу повертаються на його вхід і не втрачаються. В даному регістрі зсуву використовуються чотири JK-тригери. Треба звернути увагу на зворотній зв’язок виходу тригера TD та входів J і K тригера ТА. Завдяки цьому ланцюгу зворотного зв’язку введена в регістр інформація, яка звично втрачається на виході тригеру TD, буде циркулювати по регістру зсуву. Сигналом очищення регістру (встановлення його виходів в стан 0000) є рівень логічного нуля на вході CLR.

Входи паралельного завантаження A, B, C, D пов’язані з входами попереднього встановлення тригерів PRN, що дозволяє встановлювати рівень логічної одиниці на будь-якому виході (A, B, C, D). Якщо на один з цих входів подати логічний 0, то на відповідному виході буде логічна 1. Подача тактових імпульсів на входи CLK всіх JK-тригерів призводить до зсуву інформації в регістрі вправо. З тригеру TD дані передаються в тригер ТА (кільцеве переміщення інформації).

Табл. 7.2.2. Робота 4-розрядного паралельного кільцевого регістру зсуву

Табл. 7.2.2 допомагає зрозуміти принцип роботи паралельного регістру зсуву. При включенні живлення на виходах регістру встановлюється будь-яка двійкова комбінація, така, наприклад як в рядку 1 таблиці 7.2.2. Подача логічного 0 на входи CLR тригерів ініціює очищення регістру (рядок 2). Далі (рядок 3) відбувається завантаження в регістр двійкової комбінації 0100. Послідовні тактові імпульси викликають зсув введеної інформації вправо (рядки 4-8). Треба звернути увагу на рядки 5 і 6: одиниця з крайнього правого тригеру TD переноситься в крайній лівий тригер ТА. В даному випадку можливо говорити про кільцеве переміщення одиниці в регістрі. Далі (рядок 9) заново ініціюється очищення регістру за допомогою входу CLR. Завантажується нова двійкова комбінація 0110 (рядок 10). Подача 5 тактових імпульсів (рядки 11-15) призводить до кільцевого зсуву інформації на 5 позицій вправо. Треба звернути увагу, що для повернення даних в початковий стан потрібно 4 тактових імпульси. Якщо в регістрі зсуву на рис. 2.2 розірвати ланцюг зворотного зв’язку, то ми отримаємо звичайний паралельний регістр зсуву; можливість кільцевого переміщення даних буде виключена.

7.2.3 Програма реалізації регістрів в інтегрованому середовищі MAX+PLUS II Програма для реалізації 4-розрядного послідовного регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: Title "register1"; Parameters (WIDTH = 4); - встановлення розрядності регістру Assert (WIDTH > 0) - перевірка розрядності регістру на відмінність від 0

Report "Value of WIDTH parameter must be greater then %" WIDTH Severity Error; Subdesign register1 ( D_INPUT, SET, RESET: input = GND; - вхідні сигнали CLK: input; - вхід синхронізації ENABLE: input = VCC; - вхід дозволу роботи Q_OUTPUT: output; - вихідні сигнали ) Variable FF[WIDTH..1]: DFFE; - об'ява змінної FF, що належить до класу DFFE Begin FF[].clk = CLK; FF[].prn =!SET; FF[].clrn =!RESET; FF[].ena = ENABLE; FF[].d = (FF[WIDTH-1..1].q, D_INPUT); Q_OUTPUT = FF[WIDTH].q; End; - Примітка: на часовій діаграммі: - FF - двійкове число на виході регістру Програма для реалізації 4-розрядного паралельного кільцевого регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: Subdesign register2 Parameters (WIDTH = 4); - встановлення розрядності регістру Assert (WIDTH > 0) - перевірка розрядності тригера (більша від нуля) Report "Value of WIDTH parameter must be greater then %" WIDTH Severity Error; ( I[WIDTH..1]: input = VCC; - вхідні сигнали (дані) CLK: input; RESET: input; O[WIDTH..1]: output; - вихідні сигнали (дані) ) Variable FF[WIDTH..1]: JKFF; - об'ява змінної FF, що належить до класу JKFF Begin FF[WIDTH..1].j = (FF[WIDTH-1..1].q, FF[WIDTH].q); FF[WIDTH..1].k = (!FF[WIDTH-1..1].q,!FF[WIDTH].q); FF[WIDTH..1].clk = CLK; FF[WIDTH..1].clrn =!RESET; FF[WIDTH..1].prn = I[WIDTH..1]; O[WIDTH..1] = FF[WIDTH..1].q; End;

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-06; просмотров: 183; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.225.55.198 (0.031 с.) |