Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Схема памяти микропроцессорной системы.

Иногда одной БИС памяти для микропроцессорной системы оказывается недостаточно. Это происходит или из за малой разрядности БИС или из за ее недостаточного адресного пространства. В обоих случаях запоминающие устройства строятся из набора однотипных микросхем ЗУ с определенным их соединением. Например, если требуется хранить данные размером в n-бит, а длина слова ячейки памяти m-бит (n>m), то прибегают к наращиванию длины слова. Делается это путем объединения n / m - микросхем в группы, причем все одноименные входы, кроме информационных, соединяются между собой. Более распространен случай, когда надо увеличить адресного пространства. Увеличение адресного пространства ЗУ в 2k раз требует столько же микросхем памяти и k дополнительных линий адреса, к уже имеющимся n линиям An+k-1,..An+0, An-1, An-2,... A1, A0. Дополнительные адресные линии An+k-1.. An+0 должны разбивать требуемое адресное поле на 2k неперекрывающихся интервалов, покрываемых объемом памяти каждой отдельной микросхемы. Для решения этой задачи требуется дополнительный дешифратор "k в 2k". Полная схема памяти микропроцессорной системы показана на рис 3.9.

Рис. 3.9. Схема организации памяти микропроцессорной системы.

.

Микросхемы ОЗУ и ПЗУ подключаются к шине данных и необходимому числу младших линий адреса А0 – А7. Сигналы выборки кристалла для микросхем ЗУ формирует дешифратор 3:8, что обеспечивает в системе одновременный выбор только одной микросхемы. Для этого используют линий адреса А8 – А10. В любой момент времени только на одном из выходов дешифратора действуют сигнал логического 0, разрешающий работу микросхемы ЗУ. Причем на входе разрешения самого дешифратор (ЕN) также должен быть сигнал логического 0. Этот сигнал формируется при наличии на шине управления или сигнала чтения RD или сигнала записи WR. Сигналы на линиях адреса А11 – А15 поступают на логическую схему, например 4 – И – НЕ, сигнал с выхода которой разрешает работу верней или нижней частей дешифратора. В конкретной схеме, как на рис. 3.9, может быть организована совмещенная адресация памяти и ввода - вывода. При этом сигналы CS4 -, CS7 на выходах дешифратора могут быть использованы для выбора устройств ВВ. Если в микропроцессорной системе имеется больше восьми микросхем памяти и ВВ, то вместо дешифратора 3:8 потребуется дешифратор большей емкости, на вход которого будут подаваться неиспользуемые старшие линии шины адреса. При изолированной адресации ВВ для микросхем памяти и ВВ следует применять отдельные дешифраторы.

В этой конфигурации микросхемы и регистры памяти и ВВ могут иметь одни и те же адреса, но конфликта не возникает, так как CPU выдает при работе с памятью один сигнал IO/M=0 (работает первый дешифратор, связанный с памятью), а при работе с ВВ другой IO/M=1 (второй дешифратор, связанный с ВВ). Регистры, регистровые структуры и адресация данных однокристальных МП. Регистры и их типы. Основным архитектурным компонентом МПС, определяющим и организацию взаимодействия с CPU модулей системы и организацию вычислительного процесса в целом, является структура регистровой области CPU. Регистры МП можно рассматривать как скоростное ОЗУ малой емкости, предназначенное для хранения адресов и данных и входящее в состав CPU. Регистров относительно немного, поэтому команды работы с регистрами имеют компактный код. Короткая адресация регистровой области и быстрый доступ к ней обеспечивают создание эффективно исполняемых программ. Регистры МП функционально неоднородны: одни регистры служат для хранения данных или адресной информации, другие - для управления работой CPU. В соответствии с этим все регистры можно разделить на регистры данных, указатели и регистры специального назначения. Регистры данных участвуют в арифметических и логических операциях в качестве источников операндов и приемников результата, адресные регистры или указатели используются для вычисления адресов данных (операндов) и команд, расположенных в основной памяти. Специальные регистры служат для индикации текущего состояния CPU и управления режимами работы CPU. Функциональная специализация регистров в свою очередь определяет систему команд CPU. При слабой специализации часть регистров обычно применяется для хранения, как операндов, так и адресов. Если при этом разрядность шин адреса и данных совпадает, например 16/16, то их называют регистрами общего назначения (РОН). Функциональная неоднородность регистров связана с широким использованием неявной (подразумеваемой) адресации регистров. Неявная адресация, в свою очередь, порождает компактный код команд CPU, что, в конечном счете, приводит к созданию коротких программ. Но функциональная специализация регистров затрудняет программирование, так как требует учета особенностей организации регистрового набора, присущих данному CPU. Однако в результате объектный код команд исполняется быстрее и для его хранения требуется меньшая память.

Адресные регистры. А дресные регистры - регистры указатели применяются для реализации различных методов непрямой (вычисляемой) адресации данных. Например у некоторых CPU, регистр косвенного адреса DP (Data Pointer) содержит непосредственно адрес операнда, регистр базы ВР (Base Pointer) используется для хранения начальных адресов массивов и записей, содержимое индексного регистра Х (Index) является относительным адресом (индексом) операнда. Среди адресных регистров следует также отметить регистры автоинкрементной и автодекрементной адресации, которые автоматически увеличивают или уменьшают свое состояние до или после выполнения операции доступа в соответствии с длиной адресуемого ими операнда, и регистры расширения адресного пространства или указатели сегментов и страниц. Очень важной является функция хранения адреса следующего элемента программной последовательности, подлежащего выборке в очередном машинном цикле. Эту функцию выполняет программный счетчик (РС). Большая часть команд CPU выполняется последовательно, в порядке возрастания адресов памяти. Во время выборки очередной команды содержимое РС увеличивается на 1 или 2 для указания адреса следующего байта или слова в последовательных ячейках памяти. При этом процесс адресации следующего элемента командной последовательности, как правило, осуществляется неявно. В типовой команде, какие - либо сведения об адресе следующей команды отсутствуют. Поэтому функция РС возлагается на конкретный регистр, содержимое которого автоматически инкрементируется после очередной выборки элемента командной последовательности. Изменение последовательности процесса выборки команд должно осуществляться специальными командами передачи управления CPU. Эти команды выполняют загрузку в РС адреса, который может отличаться от адреса следующей команды.

Стек. Частным случаем регистра с авто модификацией является указатель стека SP (Stack Pointer). Он необходим для организации системного стека, который предназначен для хранения адресов возвратов и состояний процессора при вызове подпрограмм и обслуживании прерываний. Стек может также использоваться для временного хранения локальных переменных и передачи входных или выходных параметров при вызовах подпрограмм. Стек - это область памяти с доступом типа «последний пришел - первый вышел» или LIFO. Стек обычно заполняется в сторону уменьшения адресов, при этом указатель стека показывает на последнюю заполненную ячейку стека - вершину стека TOS (Top of Stack). Такой стек называется типовым, так как именно он применяется в большинстве МПС. При записи в стек нового элемента данных (операция PUSH) содержимое SP уменьшается на 1 или 2 в зависимости от длины элемента (байт или слово) и затем используется в качестве адреса новой вершины, в которую заносится элемент. При считывании элемента данных из стека (операция РОР) сначала считывается содержимое TOS, а затем содержимое SP увеличивается на 1 или 2 для адресации новой вершины стека. Работа стека показана на рис. 4.1.

Рис. 4.1. Работа стека при вызове подпрограмм.

Исключительные удобства, предоставляемые стеком при вызове подпрограмм, привели к тому, что практически все современные CPU имеют встроенные средства для его построения в виде SP и соответствующих команд CPU. При использовании стека для хранения локальных переменных и обмена параметрами между вызываемой и вызывающей процедурой может оказаться полезным специальный адресный регистр, указывающий на начало области параметров в стеке. Регистр с таким функциональным назначением называется указателем кадра FP. Действительно, значение SP непрерывно меняется, поэтому применять его в качестве точки отсчета при доступе к данным в стеке крайне неудобно. Процедуру доступа можно значительно упростить, если функцию точки отсчета отдать специально зарезервированному для этой цели указателю FP, который принадлежит к классу базовых регистров.

Специальные регистры. При выполнении многих команд АЛУ, кроме результата операции еще генерирует ряд двоичных сигналов - признаков, дополнительно характеризующих результат операции. Функцию хранения этих признаков выполняет специальный регистр признаков (флагов) RF. С каждым признаком результата операции связана одноразрядная переменная - флажок, состояние которой отображает соответствующий бит RF. В состав этого регистра включаются также некоторые другие флажок, характеризующие текущее состояние или режим CPU. Регистр признаков RF вместе со счетчиком команд PC часто объединяют в слово состояния программы PSW (Program Status Word). У первых микропроцессоров был минимальный набор флажков-признаков результата операции: CF - флажок переноса из старшего разряда АЛУ. Флажок CF используется наиболее часто. ZF - флажок признака нуля. SF - флажок знака результата. Применяется при целочисленной арифметике со знаком AC – флажок дополнительного переноса или переноса из младшей тетрады. OF - флажок арифметического переполнения. РЕ - флажок четности результата.

Рис. 4.2. Формат регистра флагов RF.

Бывает очень удобно, если поле условия RF содержит один или несколько флажков пользователя, функциональное назначение которых определяет он сам. Обычно эти флажки служат для связи между отдельными частями программы. В системе команд любого CPU есть команды условного перехода или команды тестирования. Каждая такая команда проверяет состояние определенного флажка RF. В зависимости от этого или происходит изменение последовательности процесса выборки команд или выполняется следующая команда. Таким образом, организуется ветвление программы. В состав PSW может входить также ряд специальных флажков, управляющих работой CPU и устанавливающих, например: маски и приоритеты прерываний, условия реакции на прерывания или флажок пошаговой трассировки. Упаковка всех флажков в одно слово дает возможность организовать их быструю засылку в память (стек) с последующим восстановлением. У более сложных CPU специальных регистров может быть несколько.

Регистры данных. Наиболее типичным представителем регистров данных является аккумулятор А, который используется для временного хранения исходных операндов и промежуточных результатов. С аккумулятором связано большинство команд арифметической и логической обработки. Ссылка на него, как правило, производится неявно с помощью кода операции. Неявная адресация позволяет не указывать в командах местоположения одного из операндов и (или) результата операции, что существенно уменьшает длину их кода. Это очень важно в условиях ограниченной пропускной способности системной магистрали, особенно для 8-разрядных МПС. Поэтому большинство первых CPU, имели аккумулятор и были ориентированы на его интенсивное использование. В составе CPU может находиться один или несколько аккумуляторов. Так, у микропроцессора МС6809 два аккумулятора - А и В. Такие CPU имеют одноадресную систему команд, так как в коде команды явно указывается адрес лишь одного операнда. При этом предполагается, что источником другого операнда служит аккумулятор. Он же, как правило, применяется и для хранения результата операции:

Другим вариантом регистров данных являются рабочие регистры. В отличие от аккумулятора они адресуются явно (R0-RN) и могут интерпретироваться как сверхскоростные регистровые ОЗУ данных. Рабочие регистры могут использоваться в операциях как совместно с аккумулятором, гак и без него. Если рабочие регистры совмещают свою функцию хранения данных с функцией их адресации, то в этом случае они приобретают функции РОН. В командах тогда допускается только один операнд, хранящийся в памяти МПС, тогда как другой должен находиться в регистровой области. В архитектуре с рабочими регистрами для реализации быстрого доступа к промежуточным данным часть основной памяти данных обычно размещена на одном кристалле с CPU. В ряде CPU, предназначенных для работы в реальном масштабе времени, могут быть предусмотрены два или даже четыре набора рабочих регистров, один из которых резервируется для системных целей или обработки прерываний, а все остальные - для прикладных задач пользователя. В каждый момент времени доступен только один набор рабочих регистров, выбираемый специальным указателем WP. Выпускаемые промышленностью CPU обычно являются результатом компромиссного выбора между несколькими типами организаций и, следовательно, могут быть отнесены к тому или иному классу лишь условно. Микропроцессоры выпускаются в виде семейств, в которых на одном ядре, содержащем типовой набор регистров выполнены различные по параметрам CPU. В таких семействах, как правило, варьируются параметры размещенной на кристалле памяти и периферии.

Примеры регистровых структур. Классический набор регистров с аккумулятором имеет один из первых 8 – разрядных микропроцессоров фирмы INTEL – i8085. Программная модель микропроцессора i8085, раскрывающая его структуру представлена на рис. 4.3.

Рис. 4.3. Регистровая структура микропроцессора i8085.

Помимо аккумулятора А, в нем имеются шесть 8-битных регистров данных: В, С, D, Е, Н и L. В некоторых командах эти регистры можно объединять в регистровые пары (Rp) ВС, DE и HL для работы с 16-битныии величинами, как данными, так и адресами. Кроме того, регистровая пара HL является типовым индексным регистром и применяется в командах для задания косвенной регистровой адресации. Например, команда МОV А, М передает в аккумулятор А байт данных из ячейки памяти (M - memory), адрес которой находится в регистровой паре HL. Признаки результата операции в АЛУ фиксируются в регистре признаков F, который совместно с аккумулятором А образует 16 - разрядное слово состояния программы PSW. Это слово используется в некоторых командах, работающих со стеком, чтобы быстро сохранить и восстановить контекст CPU. Микропроцессор i8085 также содержит два 16-разрядных адресных регистра: программный счетчик PC и указатель стека SP. Эта регистровый набор был расширен у микропроцессора Z80 фирмы ZILOG. Набор регистров Z80 показан на рис.4.4. Рабочие регистры А, В, С, D, E, H и L аналогичны соответствующим регистрам 8085, но в Z80 существует такой же второй набор регистров (А1-L1) и второй регистр флагов F1. Наличие второго набора (банка) регистров значительно ускоряет работу системы при вызове подпрограммы или обработке прерывания, потому что программист может использовать для них альтернативный набор, избегая сохранения содержимого регистра основной программы, например командами включения в стек. Для программной поддержки этого процесса в системе команд Z80 есть две команды, которые осуществляют обмен содержимого всех регистров:

EXX; Обменять BC, DE, H. EX AF, AF; Обменять AF и AF (F обозначает флажки).

В состав регистров Z80 введен 8 - и битный регистр вектора прерывания I. Этот регистр используется Z80 для локализации адреса вектора прерывания ISR, когда CPU работает в одном из режимов прерывания. Специально для работы с динамической памятью в состав регистров Z80 введен регистр R. После каждой команды CPU производится инкремент регистра R и его содержимое выдается между командами на младшую половину шины адреса. Таким образом, происходит регенерация текущей страницы (256 ячеек) динамической памяти. И, наконец. в структуру Z80 добавлены два 16-битных индексных регистра IХ и IУ, который используются в командах с индексным режим адресации.

Рис. 4.4. Регистровая структура микропроцессора Z80.

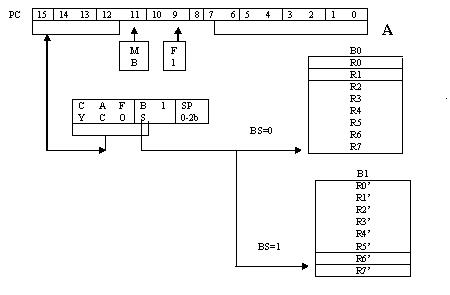

Архитектура с переключаемыми банками регистров нашла применение в популярных семействах микроконтроллеров MCS-48 и MCS-51 фирмы INTEL. Отечественными аналогами этих семейств являются микроконтроллеры (однокристальные микро ЭВМ) семейств К1816ВЕ48/ВЕ51. Онитоже имеет элементы организации аккумуляторного типа, которая расширена набором из восьми рабочих регистров составляющих регистровый банк. В семействе MCS-48 предусмотрено два набора (два банка), а в семействе MCS-51 уже четыре банка. Два первых регистра в каждом наборе являются регистрами общего назначения (РОН). Они, следовательно, могут быть использованы как регистры данных. а также применяться для адресации данных во внутреннем ОЗУ. Все регистровые банки располагаются в области внутренней памяти данных, причем их размещение в памяти данных строго регламентировано. Прямой переход из банка в банк защищен, поэтому для выбора конкретного набора используется одно - или двухразрядный указатель текущего банка BS, входящий в состав PSW. Микроконтроллеры этих семейств имеют гарвардскую архитектуру и двенадцатиразрядный счетчик команд. Область программной памяти тоже разбита на банки, выбором которых управляет указатель МВ. Трехразрядный указатель стека, который находится во внутреннем ОЗУ, также входит в состав PSW. Структуру PSW и механизм переключения банков рассмотрим позже. Регистровая структура семейства микроконтроллеров MCS-48 показана на рис.4.4.

Рис. 4.5. Регистровая структура семейства микроконтроллеров MCS-48

Адресация данных. Способ задания операнда в команде называется методом адресации. Код команды содержит именную часть или код операции (КОП) и адресную часть, содержащую сведения об операндах. Для конкретной архитектуры микропроцессора существует несколько способов адресации, эффективных для различных применений. Рассмотрим основные методы адресации: прямой, непосредственный, косвенный, индексный и способы с автомодификацией. При прямой адресации команда состоит из код операции и адреса операнда. Вариантом прямой адресации является прямая регистровая адресация. Для прямой ссылки на регистр, входящий в состав небольшой регистровой памяти МС, обычно требуется несколько бит. В результате получаем короткую команду. Кроме того, при пересылке операндов в АЛУ, все происходит внутри кристалла, и поэтому отсутствуют циклы обращения к системной магистрали. Рис. 4.6. Все это обеспечивает большую скорость выполнения команд, а значит эффективность регистровой адресации. Команды пересылки регистр – регистр выделяются в особый подкласс. Время их выполнения служит одной из характеристик быстродействия CPU.

Рис. 4.6. а) Прямая адресация данных. б) Регистровая адресация данных.

При непосредственной адресации данные, подлежащие обработке, содержатся непосредственно в самой команде в виде ее второго 8 или 16-разрядного слова (литерала). Вариантом прямой адресации является прямаяадресация порта. Рис. 4.7

Рис. 4.7. а) Непосредственная адресация данных. б) Прямая адресация порта.

Основной недостаток этих видов адресации невозможность манипуляции данными без модификации кода привел к созданию способов с вычисляемым адресом. Простейшим из них является косвенная адресация, где в адресной части команды содержится указатель на объект (ячейку памяти или регистр) с адресом операнда. Особенно распространен вариант регистровой косвенной адресации, где хранителем исполнительного адреса является регистр или регистровая пара. Часто данные некоторой структуры располагаются в памяти последовательно, причем каждый элемент структуры занимает одинаковый объем. Например, это могут быть массивы, записи, списки, и т. д. Для повышения эффективности работы со структурами такого типа используются автоинкрементный и автодекрементный способы адресации (адресация с автомодификацией). При способе с автомодификацией обеспечивается вычисление исполнительного адреса, как при косвенной регистровой адресация, но с последующим (или предшествующим) автоматическим увеличением (или уменьшением) содержимого адресного регистра на длину операнда. Рис. 4.8. При обычном автоинкрементном способе содержимого адресного регистра сначала используется как исполнительный адрес, а затем увеличивается на длину операнда.

MOVB dst, (reg)+.;dst ← (reg), reg = reg+1.

При автодекрементном способе содержимого адресного регистра сначала уменьшается на длину операнда, а затем используется как исполнительный адрес.

MOVB dst, - (reg);reg = reg-1, dst ← (reg)

Рис. 4.8. а)Косвенная адресация. б) Автоинкрементнаяадресация. в) А втодекрементная адресация

Неявно автодекрементный способ адресации применяется при операциях со стеком: PUSH src; POP dst; CALL src; RET; При исполнении программы и выборке очередной команды используется неявно заданная автоинкрементная адресация по P C. Индексная адресация является вариантом многокомпонентной адресации. Индексная адресация применяется при последовательном доступе к элементам блока, адрес размещения которого не известен во время создания программы. При этом переменный адрес начала блока хранится в индексном регистре, а известный относительный номер элемента (смещение) непосредственно в команде. Исполнительный адрес получается при сложении содержимого индексного регистра и смещения. Рис. 4.9.

Рис. 4.9. Индексная адресация данных. Подсистема ввода-вывода.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 308; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.191.44.23 (0.074 с.) |