Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

ИСР Code Composer Studio (CCS)

TMS320С6000 Серия TMS320C6x (сокращенно ’C6x)компании Texas Instruments Inc – это цифровые сигнальные процессоры (ЦСП) для обработки сигналов в реальном времени. Их отличает большая производительность. Высокая производительность достигается за счет внедрения параллельной архитектуры VelociTI, реализованной на основе технологии очень длинного командного слова VLIW (Very Long Instruction Word), а также за счет применения ряда других аппаратных решений и средств разработки.

По оценкам специалистов, применение данной архитектуры в будущем позволит, при сохранении совместимости по командам, достичь рубежей 8000 MIPS для ЦСП с фиксированной точкой и 3 GFLOPS для ЦСП с плавающей. Изготовляются и широко применяются следующие разновидности ЦСП серии TMS320C6000: · TMS320C62x – устройства с фиксированной точкой и производительностью от 1200 до 2400 MIPS. · TMS320C64x – устройства с фиксированной точкой и производительностью от 3200 до 4800 MIPS. Данные ЦСП являются наиболее скоростными. · TMS320C67x – устройства с плавающей точкой и производительностью от 600 до 1350 MFLOPS. Производительность ЦСП:

Оценка продолжительности выполнения популярных алгоритмов.

При проектировании ЦСП ‘C6x особое внимание изготовителя уделялось снижению времени, которое понадобится пользователю для разработки и выпуска конечных систем. Сокращению этих сроков способствует свойство совместимости устройства с фиксированной точкой с соответствующим устройством с плавающей точкой. ЦСП ‘C67х имеют совместимость по командам и по выводам микросхем с ЦСП ‘С62х, что позволяет разработчику быстро выполнять прототипы, используя плавающую точку, и легко переходить к ЦСП с фиксированной точкой для снижения стоимости изделия при производстве. Вначале разработчик может взять за основу ЦСП с плавающей точкой, отработать все элементы устройства, определить оптимальные алгоритмы обработки данных. При этом большие запасы по производительности и по точности вычислений позволяют заниматься именно алгоритмами, а не экономией ресурсов. После, когда все параметры определены, наступает этап оптимизации системы с учетом наработанных решений и перевод ее на более дешевый ЦСП с фиксированной точкой.

Данный подход предопределил переход от аппаратно-ориентированной среды разработки к программным моделям, что делает процесс разработки более быстрым, дешевым и простым. Архитектура VelociTI Все ЦСП С6x основаны на одном и том же 32-разрядном ядре центрального процессора с высоко параллельной и детерминированной архитектурой VelociTI. Архитектура ядра ЦСП С6x включает 8 модулей - 2 умножителя и 6 АЛУ. Все модули максимально независимы, что дает компилятору и оптимизатору множество комбинаций их использования. На каждом такте ЦСП выбирается восемь 32-битных RISC-подобных инструкций. Предусмотренная в архитектуре VelociTI упаковка команд позволяет исполнять эти восемь инструкций параллельно, последовательно или параллельно/последовательно. Эта оптимизированная схема существенно снижает размер кода, количество выборок команд и потребление питания. При добавлении функции плавающей запятой к шести из восьми функциональных модулей из ЦСП с фиксированной точкой 'С62х получается ЦСП с плавающей точкой – 'С67х. При этом система команд 'С62х - расширение системы команд 'С67х и весь код написанный для 'С62х будет выполняться на 'С67х без модификаций самого кода. Рассмотрим подробнее архитектуру ядра ЦСП серии TMS320C6000. Упрощенная схема ядра, без периферии и внешних шин, иллюстрирующая архитектуру VelociTI.

Как видно из рисунка, ЦСП использует очень длинные инструкции (256 бит) для выдачи до 8 команд по 32 бита для каждого из 8 функциональных модулей в каждом такте. Выбираются инструкции всегда по 256 бит, однако длина исполняемого пакета может быть разной, как показано на рисунке. Переменная длина выполняемой команды позволяет существенно сэкономить память – это отличительная черта ЦСП С6x от остальных ЦСП с очень длинным командным словом.

Ядро ЦСП С6x имеет два набора функциональных модулей. Каждый набор включает 4 модуля и регистровый файл. Каждый файл состоит из 16 32-разрядных регистров. Таким образом, всего в ядре 32 32-разрядных регистра. Два набора функциональных модулей, связанных с двумя наборами регистров, создают разделение ядра на стороны А и В. 4 модуля с каждой стороны ЦСП С6x имеют произвольный доступ к регистровому файлу данной стороны. Кроме того, каждая сторона имеет шину, соединенную с регистровым файлом другой стороны. При доступе к регистрам своей стороны возможен доступ к регистрам всех модулей одновременно в одном такте. Другой особенностью архитектуры ЦСП С6x является использование стратегии сохранения/загрузки, при которой все команды работают с регистрами. При этом два адресных модуля D1 и D2 выделяются только под передачу данных между регистровым файлом и памятью. Шины адреса, управляемые D-модулями, позволяют использовать адрес, сгенерированный в одном регистровом файле, для операций с данными в другом регистровом файле. Ядро ЦСП С6x поддерживает широкий набор режимов косвенной адресации, включая линейный или кольцевой с 5- или 15-битным смещением. Все команды могут быть условными, и большинство команд могут использовать любой из 32 регистров. Некоторые регистры могут быть выделены для поддержки специфических режимов адресации или для хранения условий для условных команд. 2 М-модуля выделены под аппаратные умножители 16х16. Два S- и два L-модуля выполняют арифметические, логические операции и операции перехода, и при этом результаты их выполнения доступны в каждом такте (возможна задержка до 5 тактов конвейера, но большинство команд выполняются за 1 такт). Процесс обработки команды в ядре начинается после выборки 256- битовой инструкции из внутренней памяти команд, которая также может быть сконфигурирована как кэш-память команд. Далее каждая из 32-битных команд распределяется на свой модуль для исполнения. При этом у команд, выполняемых на разных модулях, проверяется младший бит. Он устанавливается в 1 для всех команд, которые должны выполняться одновременно. Команды, которые собраны для одновременного выполнения (до 8 команд), образуют пакет выполнения. Ноль ставится в младшем бите команды, которая нарушает последовательность выполнения и откладывает команду на следующий пакет выполнения. Всего в выборке может быть до 8 пакетов выполнения. Очередной пакет размещается для выполнения в модулях в каждом такте. До окончания выполнения пакета следующий пакет выборки из памяти не выбирается. Эта «стратегия» позволяет существенно экономить память команд и менять режим работы программы от одновременного параллельного выполнения 8 команд на 8 модулях до практически последовательного выполнения команд, в зависимости от требований алгоритма. Обратим внимание на организацию памяти данных. Как уже упоминалось, данные из функциональных модулей помещаются в регистры, а затем по адресам, генерируемым D-модулями, идет обмен с памятью данных. При этом каждый из регистровых файлов соединен 32 разрядными шинами с диспетчером памяти. Диспетчер организует одновременную выборку из памяти по четырем шинам до 64 разрядов по двум подаваемым адресам. При этом память дробится на множество мелких банков, что практически исключает конфликты доступа к памяти. Такое решение обеспечивает доступ без задержек при параллельных потоках обращения и при возможности адресовать отдельно каждый байт памяти. Фактически вся память данных ЦСП С6x организована не как двухпортовая, а как многопортовая, и количество одновременно выбираемых данных может меняться.

Структура и состав ЦСП С6x На рисунке показана внутренняя структура ЦСП С6x. ЦСП можно условно разделить на несколько частей: · Ядро процессора. · Области памяти данных и памяти команд. · Размещенная на кристалле периферия. Все эти части связаны между собой двумя контроллерами – памяти команд или кэш-памяти и памяти данных. Эти блоки связывают ядро ЦСП и банки памяти (с их специфической конфигурацией и доступом) с традиционными шинами, к которым подключаются периферийные модули и внешние устройства.

Рассмотрим подробнее периферийные устройства ЦСП TMS320С6000. Контроллер ПДП. Устройство предназначено для передачи данных из памяти в память без участия центрального процессора. Контроллер ПДП имеет четыре основных программируемых и пять дополнительных каналов. Кроме того, контроллер ПДП используется при начальной загрузке программы в память ЦСП при старте (bootloader). Хост «Порт-интерфейс» (ХПИ). ХПИ используется как для обмена данными с управляющим контроллером, так и для асинхронного обмена. ХПИ – это 16-разрядный параллельный порт, который обеспечивает прямой доступ к памяти ЦСП. При этом ЦСП является управляющим устройством для данного интерфейса, что существенно упрощает процедуру доступа. ЦСП может обмениваться информацией, как через внутреннюю, так и через внешнюю память. Кроме того, ЦСП может иметь прямой доступ к большинству устройств размещенной на кристалле периферии. Шина расширения (ШР). ШР является расширением как ХПИ, так и ИВП (см. ниже). С использованием ШР можно реализовать 32-разрядный ХПИ, который будет работать аналогично штатному 16-разрядному. ШР также может реализовать синхронный протокол обмена между хост ЦСП и ЦП, что дает возможность прямого подключения к большому набору стандартных шин хост ЦСП. Также к шине расширения могут быть подключено синхронное FIFO и асинхронные периферийные устройства. Интерфейс внешней памяти (ИВП). ИВП это специальный блок, предназначенный для обмена данными с внешней памятью и быстродействующими внешними устройствами. ИВП может принимать запросы на обмен с внешней памятью от трех: контроллеров памяти данных, программной памяти-КЭШ и ПДП. Поскольку сам ЦСП – очень скоростное устройство, то ИВП не только выводит наружу классическую шину, но и имеет специальные сигналы для непосредственного подключения быстродействующего синхронного внешнего ОЗУ как динамического (SDRAM), так и статического (SBSRAM). Кроме того, к ИВП можно подключить и обычное статическое ОЗУ, ПЗУ, FIFO и другие устройства.

Начальный загрузчик. ЦСП TMS320C62x и TMS320C67x могут иметь множество режимов начальной загрузки, которые определяют, что именно будет делать ЦСП после сброса при подготовке к инициализации. Они могут включать загрузку программы с внешнего ПЗУ через ИВП или загрузку программы через ХПИ/ШР из внешнего устройства. Многоканальный буферизованный последовательный порт МКБПП. Это последовательный скоростной порт, базирующийся на стандартном последовательном порте, как и в ЦСП других серий. Он имеет возможность читать и записывать данные в память без участия центрального процессора через контроллер ПДП. Кроме того, у него существуют многоканальные расширения, совместимые со стандартами El, Tl, SCSA и MVIP. Отметим следующие функциональные возможности последовательного порта: · полнодуплексная работа; · двойная буферизация данных (позволяет поддерживать непрерывность потока); · независимые тактовые частоты и схемы синхронизации для приема и передачи данных;, · прямое подключение микросхем аналоговых интерфейсов, микросхем · ЦАП и АЦП с последовательным интерфейсом. МКБПП, по сравнению со стандартным последовательным портом, имеет дополнительные возможности: · прямое подключение к шинам; · многоканальный обмен при количестве каналов до 128; · переменный размер данных 8, 12, 16, 20, 24 и 32 бита; · встроенное u-Law и А-Law компандирование; · возможность передачи первым старшего или младшего разряда данных; · программируемая полярность сигналов синхронизации и тактовых сигналов данных; · гибкое программирование внутренних тактовых импульсов и синхронизации. Таймер. ЦСП серии TMS320C6000 имеют два 32-разрядных таймера, которые могут быть использованы для: · задания временных событий; · реализации счетчиков; · генерации импульсов · прерывания ЦСП; · посылки синхроимпульсов в контроллер ПДП. Селектор прерываний. Периферия ЦСП TMS320C6000 может иметь до 32-х источников прерываний. ЦП имеет возможность обрабатывать 12 прерываний. Селектор прерываний дает возможность выбора тех 12 прерываний, которые будут использоваться, и также дает возможность смены полярности внешних входов прерываний. «Спящие» режимы. Логика снижения потребляемой мощности позволяет снимать тактовые сигналы с элементов ЦСП для снижения энергопотребления. Несмотря на свое предназначение для базовых станций, ЦСП TMS320C6000 также имеют режимы снижения энергопотребления. КМОП схемы в основном потребляют энергию в момент переключения, и чем выше частота работы, тем больше это потребление. При включении «спящих» режимов у ЦСП снимается тактовая частота сначала с ядра ЦСП, затем с периферии, размещенной на кристалле, и последний «третий» режим снимает тактовую частоту практически со всего кристалла, в том числе и с блока умножения частоты. ЦСП имеет встроенный умножитель частоты с возможностью умножения внешней тактовой частоты на 2 и на 4, что делает возможным работу с низкой входной частотой и упрощает проектирование.

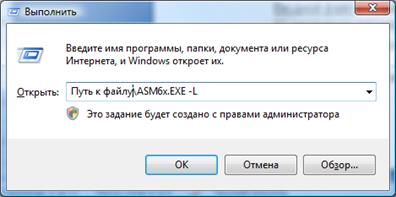

Средства разработки ЦСП С6x Для разработчиков устройств на базе ЦСП серии С6x предлагается широкий набор мощных средств разработки и отладки. Новая архитектура ЦСП данного семейства предполагает и новый подход к процессу разработки, который позволяют уменьшить время и стоимость создания проекта за счет переноса большей части работы на ПО средств разработки. Разработчику остается написать алгоритм на языке высокого уровня, а его реализация и оптимизация с использованием всех преимуществ архитектуры ЦСП С6x перекладывается на компилятор. Это снимает одну из основных трудностей при работе на ЦСП с длинным командным словом – распараллеливание алгоритма. Такой подход имеет ряд преимуществ: · Существенно сокращается срок разработки и качество получаемого продукта за счет сосредоточения именно на реализуемой задаче, а не на средствах ее реализации. · Повышается качество и оптимальность кода за счет того, что автоматический оптимизатор всегда помнит все особенности архитектуры ЦСП и использует их по максимуму. Время разработки сокращается и за счет существенного уменьшения времени отладки из-за отсутствия ошибок в коде низкого уровня, которые часто возникают по вине разработчика (что-то забыл или не учел). Процесс реализации алгоритма на ЦСП С6x протекает в несколько стадий. Вначале разработчик пишет алгоритм на языке Си или на ассемблере, и компилятор переводит его программу в машинный код с использованием всех возможностей ЦСП, таких как конвейерная обработка и интеллектуальное нахождение параллелизма в исходной программе для использования возможностей параллельной обработки команд в ЦСП. После наступает этап оценки производительности кода программными средствами, что позволяет оценить достигнутые результаты и провести оптимизацию кода без обращения к аппаратному обеспечению. И только следующим шагом идет проверка на макете устройства или отладочном модуле. Программные средства, предназначенные для разработки программ для ЦСП С6x: · С-компилятор, ассемблер и компоновщик. · Отладчик. · Среда Code Composer Studio. Высокоуровневый С-компилятор, ассемблер и компоновщик. Данные программные продукты представляют собой набор средств для компиляции кода языка С. Они специально ориентированы на реализацию оптимальных программ, созданных по алгоритмам ЦОС. Имеет широкий набор встроенных средств оптимизации, как общего плана, так и специализированных для ЦСП TMS320С6000. Является ANSI совместимым компилятором. В состав данного продукта входит ассемблерный оптимизатор - средство для перевода последовательного ассемблерного кода в параллельный, специфичный для ЦСП TMS320С6000. Отдадчик. Продукт позволяет производить проверку выполнения кода на персональном компьютере без ЦСП. Code Composer Studio. Многомодульный программный продукт представляет собой мощную интегрированную отладочную среду для ЦСП С6x и других серий. Имеет развитый оконный интерфейс, встроенные средства редактирования, возможность дизассемблирования и вызова внешнего компилятора, расширенные средства визуализации данных. По оценкам изготовителей среда Code Composer Studio станет стандартом и останется, чуть ли не единственным продуктом для программирования ЦСП компании Texas Instruments Inc. по крайней мере, до 2020 года. В настоящее время это средство платное. Ассемблер ЦСП С6x · Введение Ассемблер преобразовывает (транслирует) исходные файлы ассемблера в объектные файлы в машинном коде. Эти файлы находятся в общем формате объектного файла (COFF). Исходные файлы могут содержать следующие элементы ассемблера: · Директивы Ассемблера. · Макро директивы. · Команды ассемблера. Двухпроходовый ассемблер делает следующее: · Преобразует операторы исходника в объектный файл. · Создает листинг исходника (если требуется) и дает Вам возможность управлять им. · Позволяет Вам сегментировать код по разделам и устанавливает счетчик команд SPC в каждом разделе объектного кода. · Определяет глобальные символы и ссылки на них, создает перекрестные ссылки на листинг исходника (если требуется). · Допускает условное ассемблирование. · Допускает макросы, позволяя создавать макросы в исходнике или в библиотеке. Вызвать ассемблер можно двумя способами: · Запустить ASM6X. Ассемблер запускается с опциями по умолчанию. В частности без опции –L, которая заставляет его формировать файл листинга. · В командной строке ОС ввести путь к файлу ASM6x, имя файла и опцию –L. Файл листинга будет сформирован, и допущенные ошибки можно увидеть.

В окне ассемблера нужно задать: · Source file - исходный файл ассемблера. Если Вы не даете расширение, ассемблер использует заданное по умолчанию расширение.asm. · Формат инструкций исходника Исходник ассемблера ЦСП С6x состоит из инструкций, которые могут содержать директивы ассемблера, команды ассемблера, макро-директивы, и комментарии. Инструкция может содержать 7 упорядоченных полей (метка, признак параллельности ||, условие, мнемоника инструкции, спецификатор модуля, список операндов, и комментарий). Примеры инструкций: two.set 2; Символ two = 2 Label: MVK two, A2; Запись значения two в регистр A2 .word 016h; Инициализация слова значением 016h Ассемблер читает до 200 знаков в строке. Любые знаки свыше 200 усекаются. Операционная часть инструкций (т.е. все, кроме комментариев) должна быть короче 200 знаков для правильной трансляции. Комментарии могут простираться за пределы 200 знаков, но усеченная часть не включается в файл листинга. Следуйте этим рекомендациям: · Все инструкции должны начаться с метки, пробела, звездочки, или точки с запятой. · Метки не обязательны, если они используется, они должны начаться в столбце 1. · Один (или больше) пробелов должно отделять каждое поле. Символы табуляции интерпретируются, как пробелы. Вы должны отделить список операндов от предшествующего поля пробелом. · Комментарии необязательны. Комментарии, которые начинаются в столбце 1, могут начинаться со звездочки или точки с запятой (* или;), комментарии, которые начинаются в любом другом столбце должны начинаться с точки с запятой. · Если Вы используете условную команду, имя регистра, по содержимому которого выполняется команда, должно быть окружено квадратными скобками. · Спецификатор модуля необязательный. Если Вы не определяете функциональный блок, ассемблер назначает функциональный блок сам, основываясь на мнемоническом поле. · Мнемоника не может начинаться с 0 или 1, иначе это будет интерпретироваться, как метка. Метки. Они необязательны для всех команд ассемблера и для большинства (но не всех) директив ассемблера. Когда используется, метка должна начаться в столбце 1 инструкции. Метка может содержать до 128 алфавитно-цифровых знаков (A-Z, a-z, 0-9, _, и $). Метки чувствительны к регистру, и первый знак не может быть числом. Метка может сопровождаться двоеточием (:). Если Вы не используете метку, знак в столбце 1 должен быть пробелом, звездочкой, или точкой с запятой. Признак параллельности. Символы || указывают команды, которые выполняются параллельно с предыдущей командой. Вы можете иметь до восьми команд, выполняющихся параллельно. Следующий пример демонстрирует шесть команд (Inst1…Inst6), выполняющихся параллельно: Inst1 || Inst2 || Inst3 || Inst4 || Inst5 || Inst6 Inst7 Условие. Квадратные скобки [] указывают условные команды. Команда выполняется на основании значения регистра в пределах скобок, допустимые имена регистров – A1, A2, B0, B1, B2. Команда выполняется, если значение регистра отлично от нуля. Если перед именем регистра стоит восклицательный знак (!), то команда выполняется, если значение регистра = 0. Например: [A1] ZERO A2; Если A1 не равен 0, обнулить A2 Мнемоника инструкции. Например, ADD, MVK. Поле спецификатора модуля. Это необязательное поле, которое следует за мнемоническим полем. Поле спецификатора модуля начинается с точки (.), сопровождаемой спецификатором функционального блока. Вообще, одна команда может быть назначена каждому функциональному блоку в одном командном цикле. Имеется восемь функциональных блоков, по два каждого функционального типа: ·.D1 и.D2 Данные/сложение/вычитание. Используются для формирования адресов памяти данных. ·.L1 и.L2 АЛУ/сравнение/арифметика длинных данных. АЛУ означает арифметико-логическое устройство. ·.M1 и.M2 Умножение. ·.S1 и.S2 Сдвиг/АЛУ/переходы/битовые поля. Имеются несколько способов использовать поле спецификатора модуля: · Вы можете определить конкретный функциональный блок (например,.D1). · Вы можете определить только функциональный тип (например,.M), и ассемблер назначит определенный модуль (например,.M2). · Если Вы не определяете функциональный блок, ассемблер назначает модуль, основываясь на мнемоническом поле. Поле операнда. Оно следует за мнемоническим полем и содержит один или большее количество операндов. Поле операнда требуется не для всех команд или директив. Операнд состоит из следующих элементов: символы, константы выражения (комбинация констант и символов). Операнды друг от друга отделяются запятыми (никаких пробелов!). Комментарий. Может начинаться в любом столбце и простирается до конца исходной строки. Комментарий может содержать любые знаки ASCII, включая пробелы. Комментарии печатаются в листинге программы ассемблера, но не влияют на процесс трансляции. Исходная инструкция, которая содержит только комментарий, допустима. Такой комментарий – заголовок части кода. Если она начинается в столбце 1, то может начинаться с точки с запятой (;) или звездочки (*). Комментарии, которые начинаются где-нибудь еще на строке, должны начинаться с точки с запятой. Такой комментарий описывает операцию в строке кода. Команды ассемблера

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 471; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.137.192.3 (0.088 с.) |