Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Регистры общего назначения (РОН)

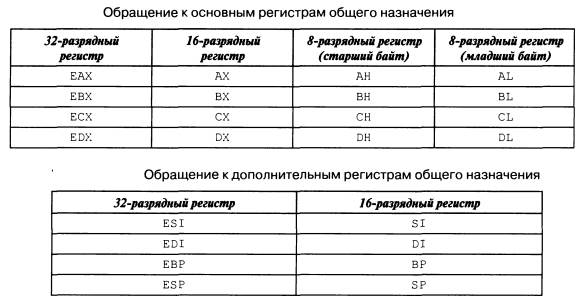

Регистры EAX, EBX, ECX, EDX называют рабочими регистрами. Так как эти регистры физически находятся в микропроцессоре внутри арифметико-логического устройства (АЛУ), то их еще называют регистрами АЛУ: · eax/ax/ah/al (Accumulator register) — аккумулятор. Применяется для хранения промежуточных данных. В некоторых командах использование этого регистра обязательно. · ebx/bx/bh/bl (Base register) — базовый регистр. Применяется для хранения базового адреса некоторого объекта в памяти. · ecx/cx/ch/cl (Count register) — регистр-счетчик. Применяется в командах, производящих некоторые повторяющиеся действия. Его использование зачастую неявно и скрыто в алгоритме работы соответствующей команды. · edx/dx/dh/dl (Data register) — регистр данных. Так же, как и регистр eax/ax/ah/al, он хранит промежуточные данные. В некоторых командах его использование обязательно; для некоторых команд это происходит неявно. РОНы используются в основном для выполнения арифметических операций и пересылки данных. Как показано на рисунке, к каждому РОНу можно обратиться как к 32-разрядному или как к 16-разрядному регистру.

К некоторым 16-разрядным регистрам можно обращаться как к двум 8-разрядным регистрам. Например, регистр EAX является 32-разрядным, однако его младшие 16-разрядов находятся в регистре АХ. Старшие 8-разрядов регистра АХ находятся в регистре АН, а младшие 8-разрядов — в регистре AL. В таблицах показаны особенности обращения к другим регистрам общего назначения, которые мы условно назвали основными и дополнительными

Особенности использования регистров. При выполнении команд процессором часть регистров общего назначения имеют особое значение. · Содержимое регистра ЕАХ автоматически используется при выполнении команд умножения и деления. Поскольку этот регистр обычно связан с выполнением арифметических команд, его часто называют расширенным регистром аккумулятора (extended accumulator). · Регистр ЕСХ автоматически используется процессором в качестве счетчика цикла. Регистры EDI, ESI - индексные регистры, используются для поддержки так называемых цепочечных операций, то есть операций, производящих последовательную обработку цепочек элементов, каждый из которых может иметь длину 32, 16 или 8 бит:

· esi/si (Source Index register) — индекс источника. Этот регистр в цепочечных операциях содержит текущий адрес элемента в цепочке-источнике; · edi/di (Destination Index register) — индекс приемника (получателя). Этот регистр в цепочечных операциях содержит текущий адрес в цепочке-приемнике. Регистры флагов EFLAGS eflags/flags (flags register) — регистр флагов. Разрядность eflags/flags — 32/16 бит. Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами. Младшая часть этого регистра полностью аналогична регистру flags для i8086. Содержимое регистра eflags.

Каждый бит этого регистра отвечает либо за особенности выполнения некоторых команд ЦП, либо отражает результат выполнения команд блоком АЛУ процессора. Для анализа битов этого регистра предусмотрены специальные команды процессора. · Управляющие флаги. Состояние битов регистра EFLAGS, соответствующих управляющим флагам, программист может изменить с помощью специальных команд процессора. Эти флаги управляют процессом выполнения некоторых команд ЦП. В качестве примера можно привести флаги управления направлением пересьшки данных (Direction) и прерыванием (Interrupt). · Флаги состояния. Эти флаги отражают результат выполнения арифметической или логической команды ЦП. Их название, описание и сокращенное обозначение приведены ниже^ · Флаг переноса (Carryflag, или CF) устанавливается в случае, если при выполнении беззнаковой арифметической операции получается число, разрядность которого превышает разрядность выделенногодля него поля результата. · Флаг переполнения {Overflow flag, или OF) устанавливается в случае, если при выполнении арифметической операции со знаком получается число, разрядность которого превышает разрядность выделенногодля него поля результата. · Флаг знака (Sign f!ag, или SF) устанавливается, если при выполнении арифметической или логической операции получается отрицательное число (т.е. старший бит результата равен 1). · Флаг нуля {Zero f!ag, или ZF) устанавливается, если при выполнении арифметической или логической операции получается число, равное нулю (т.е. все биты peзультата равны 0).

· Флаг служебного переноса {Auxiliary Carry, или AF) устанавливается, если при выполнении арифметической операции с 8-разрядным операндом происходит перенос из третьего бита в четвертый. · Флаг четности {Parity flag, или PF) устанавливается в случае, если в результате выполнения арифметической или логической операции получается число, содержащее четное количеств единичных битов. Исходя из особенностей использования, флаги регистра eflags/flags можно разделить на три группы: 8 флагов состояния. Эти флаги могут изменяться после выполнения машинных команд. Флаги состояния регистра eflags отражают особенности результата исполнения арифметических или логических операций. Это дает возможность анализировать состояние вычислительного процесса и реагировать на него с помощью команд условных переходов и вызовов подпрограмм.

1 флаг управления. Обозначается df (Directory Flag). Он находится в 10-м бите регистра eflags и используется цепочечными командами. Значение флага df определяет направление поэлементной обработки в этих операциях: от начала строки к концу (df = 0) либо наоборот, от конца строки к ее началу (df = 1). Для работы с флагом df существуют специальные команды: cld (снять флаг df) и std (установить флаг df). Применение этих команд позволяет привести флаг df в соответствие с алгоритмом и обеспечить автоматическое увеличение или уменьшение счетчиков при выполнении операций со строками;

5 системных флагов, управляющих вводом/выводом, маскируемыми прерываниями, отладкой, переключением между задачами и виртуальным режимом 8086. Прикладным программам не рекомендуется модифицировать без необходимости эти флаги, так как в большинстве случаев это приведет к прерыванию работы программы.

eip/ip (Instraction Pointer register) — регистр-указатель команд. Регистр eip/ip имеет разрядность 32/16 бит и содержит смещение следующей подлежащей выполнению команды относительно содержимого сегментного регистра cs в текущем сегменте команд. Этот регистр непосредственно недоступен программисту, но загрузка и изменение его значения производятся различными командами управления, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур. Возникновение прерываний также приводит к модификации регистра eip/ip.

Регистр указателя команд В регистре EIP, который также называют регистром указателя команд, хранится адрес следующей выполняемой команды. В процессоре есть несколько команд, которые влияют на содержимое этого регистра. Изменение адреса, хранящегося в регистре ЕIР, вызывает передачу управления на новый участок программы. Сегментные регистры В программной модели микропроцессора имеется 6 сегментных регистров: CS, SS, DS, ES, GS, FS. Их существование обусловлено спецификой организации и использования оперативной памяти микропроцессорами Intel. Она заключается в том, что микропроцессор аппаратно поддерживает структурную организацию программы в виде 3 частей, называемых сегментами. Соответственно, такая организация памяти называется сегментной. Для того чтобы указать на сегменты, к которым программа имеет доступ в конкретный момент времени, и предназначены сегментные регистры. Фактически в этих регистрах содержатся адреса памяти, с которых начинаются соответствующие сегменты. Логика обработки машинной команды построена так, что при выборке команды, доступе к данным программы или к стеку неявно используются адреса во вполне определенных сегментных регистрах. Микропроцессор поддерживает следующие типы сегментов: Эти регистры используются в качестве базовых при обращении к заранее распределенным областям оперативной памяти, которые называются сегментами. Существует 3 типа сегментов и, соответственно, сегментных регистров: · кода (CS), в них хранятся только команды процессора, т.е. машинный код программы; · данных (DS, ES, FS и GS). В них хранятся области памяти, выделяемые под переменные программы и под данные; · стека {SS), в них хранится системная область памяти, называемая стеком, в которой распределяются локальные (временные) переменные программы и параметры, передаваемые функциям при их вызове. Сегмент кода. Содержит команды программы. Для доступа к этому сегменту служит регистр CS (code segment register) — сегментный регистр кода. Он содержит адрес начала сегмента с машинными командами, к которому имеет доступ микропроцессор (то есть эти команды загружаются в конвейер микропроцессора). Суть сегментной адресации заключается в следующем. Обращение к памяти осуществляется исключительно с помощью сегментов - логических образований, накладываемых на те или иные участки физической памяти. Исполнительный адрес любой ячейки памяти вычисляется процессором путем сложения начального адреса сегмента, в котором располагается эта ячейка, со смещением к ней (в байтах) от начала сегмента. Это смещение иногда называют относительным адресом. Образование физического адреса из сегментного адреса и смещения:

Начальный адрес сегмента без четырех младших битов, т.е. деленный на 16, помещается в один из сегментных регистров и называется сегментным адресом. Сам же начальный адрес хранится в специальном внутреннем регистре процессора, называемом теневым регистром. Для каждого сегментного регистра имеется свой теневой регистр; начальный адрес сегмента загружается в него процессором в тот момент, когда программа заносит в соответствующий сегментный регистр новое значение сегментного адреса.

Сегмент данных. Содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр ds (data segment register) — сегментный регистр данных, который хранит адрес начала сегмента данных текущей программы. Сегмент стека. Этот сегмент представляет собой область памяти, называемую стеком. Работу со стеком микропроцессор организует по принципу LIFO (Last In First Out – последним пришел, первым ушел). Для доступа к этому сегменту служит регистр SS (stack segment register) — сегментный регистр стека, содержащий адрес начала сегмента стека. Для работы со стеком в системе команд микропроцессора есть специальные команды, а в программной модели микропроцессора для этого существуют специальные регистры: · С помощью регистра ESP/SP (Stack Pointer register) происходит обращение к данным, хранящимся в стеке. Этот регистр обычно никогда не используется для выполнения обычных арифметических операций и команд пересылки данных. Его часто иазывают расширенным регистром указателя стека (extended stack pointer). · Регистр EBP/BP (Base Pointer register) обычно используется для произвольной адресации в стеке параметров и локальных переменных. Регистр ESP - указатель стека, автоматически модифицируется командами PUSH, POP, RET, CALL. Явно используется реже. Дополнительный сегмент данных. Неявно алгоритмы выполнения большинства машинных команд предполагают, что обрабатываемые ими данные расположены в сегменте данных, адрес которого находится в сегментном регистре ds. Управляющие регистры Регистр CR0. · 0-й бит, разрешение защиты (РЕ). Переводит процессор в защищенный режим. · 1-й бит, мониторинг сопроцессора (МР). Вызывает исключение 7 по каждой команде WAIT. · 2-й бит, эмуляция сопроцессора (ЕМ). Вызывает исключение 7 по каждой команде сопроцессора. · 3-й бит, бит переключения задач (TS). Позволяет определить, относится данный контекст сопроцессора к текущей задаче или нет. Вызывает исключение 7 при выполнении следующей команды сопроцессора. · 4-й бит, индикатор поддержки инструкций сопроцессора (ЕТ). · 5-й бит, разрешение стандартного механизма сообщений об ошибке сопроцессора (NE). · 5-15-й бит, не используются. · 16-й бит, разрешение защиты от записи на уровне привилегий супервизора (WP). · 17-й бит, не используется. · 18-й бит, разрешение контроля выравнивания (AM). · 19-28-й бит, не используются. · 29-й бит, запрет сквозной записи кэша и циклов аннулирования (NW). · 30-й бит, запрет заполнения кэша (CD). · 31-й бит, включение механизма страничной переадресации. Регистр CR1 пока не используется. Регистр CR2 хранит 32-битный линейный адрес, по которому был получен последний отказ страницы памяти. Регистр CR3 - в старших 20 битах хранится физический базовый адрес таблицы каталога страниц. 3-й бит, кэширование страниц со сквозной записью (PWT). 4-й бит, запрет кэширование страницы (PCD). Регистр CR4 · 0-й бит, разрешение использования виртуального флага прерываний в режиме V8086 (VME). · 1-й бит, разрешение использования виртуального флага прерываний в защищенном режиме (PVI). · 2-й бит, превращение инструкции RDTSC в привилегированную (TSD). · 3-й бит, разрешение точек останова по обращению к портам ввода-вывода (DE). · 4-й бит, включает режим адресации с 4-мегабайтными страницами (PSE). · 5-й бит, включает 36-битное физическое адресное пространство (РАЕ). · 6-й бит, разрешение исключения МС (МСЕ). · 7-й бит, разрешение глобальной страницы (PGE). · 8-й бит, разрешает выполнение команды RDPMC (РМС). · 9-й бит, разрешает команды быстрого сохранения/восстановления состояния сопроцессора (FSR). Системные адресные регистры Само название этих регистров говорит о том, что они выполняют специфические функции в системе. Использование системных регистров жестко регламентировано. Именно они обеспечивают работу защищенного режима. Их также можно рассматривать как часть архитектуры микропроцессора, которая намеренно оставлена видимой для того, чтобы квалифицированный системный программист мог выполнить самые низкоуровневые операции. Большинство из системных регистров программно доступны. Не все из них понадобятся в нашем дальнейшем изложении, но, тем не менее, я коротко рассмотрел их с тем, чтобы возбудить у читателя интерес к дальнейшему исследованию архитектуры микропроцессора. Системные регистры можно разделить на три группы: · 4 регистра системных адресов; · 4 регистра управления; · 8 регистров отладки. Регистры системных адресов. Эти регистры еще называют регистрами управления памятью. Они предназначены для защиты программ и данных в мультизадачном режиме работы микропроцессора. При работе в защищенном режиме микропроцессора адресное пространство делится на: · глобальное — общее для всех задач; · локальное — отдельное для каждой задачи. Этим разделением и объясняется присутствие в архитектуре микропроцессора следующих системных регистров: · регистра таблицы глобальных дескрипторов gdtr (Global Descriptor Table Register) имеющего размер 48 бит и содержащего 32-битовый (биты 16—47) базовый адрес глобальной дескрипторной таблицы GDT и 16-битовое (биты 0—15) значение предела, представляющее собой размер в байтах таблицы GDT; · регистра таблицы локальных дескрипторов ldtr (Local Descriptor Table Register) имеющего размер 16 бит и содержащего так называемый селектор дескриптора локальной дескрипторной таблицы LDT. Этот селектор является указателем в таблице GDT, который и описывает сегмент, содержащий локальную дескрипторную таблицу LDT; · регистра таблицы дескрипторов прерываний idtr (Interrupt Descriptor Table Register) имеющего размер 48 бит и содержащего 32-битовый (биты 16–47) базовый адрес дескрипторной таблицы прерываний IDT и 16-битовое (биты 0—15) значение предела, представляющее собой размер в байтах таблицы IDT; · 16-битового регистра задачи tr (Task Register), который подобно регистру ldtr, содержит селектор, то есть указатель на дескриптор в таблице GDT. Этот дескриптор описывает текущий сегмент состояния задачи (TSS — Task Segment Status). Этот сегмент создается для каждой задачи в системе, имеет жестко регламентированную структуру и содержит контекст (текущее состояние) задачи. Основное назначение сегментов TSS — сохранять текущее состояние задачи в момент переключения на другую задачу. Регистры управления. В группу регистров управления входят 4 регистра: cr0, cr1, cr2, cr3. Эти регистры предназначены для общего управления системой. Регистры управления доступны только программам с уровнем привилегий 0. Хотя микропроцессор имеет 4 регистра управления, доступными являются только 3 из них — исключается cr1, функции которого пока не определены (он зарезервирован для будущего использования). Регистр cr0 содержит системные флаги, управляющие режимами работы микропроцессора и отражающие его состояние глобально, независимо от конкретных выполняющихся задач. Назначение системных флагов: · pe (Protect Enable), бит 0 — разрешение защищенного режима работы.Состояние этого флага показывает, в каком из двух режимов — реальном (pe=0) или защищенном (pe=1) — работает микропроцессор в данный момент времени. · mp (Math Present), бит 1 — наличие сопроцессора. Всегда 1. · ts (Task Switched), бит 3 — переключение задач. Процессор автоматически устанавливает этот бит при переключении на выполнение другой задачи. · am (Aligment Mask), бит 18 — маска выравнивания. Этот бит разрешает (am = 1) или запрещает (am = 0) контроль выравнивания. · cd (Cache Disable), бит 30, — запрещение кэш-памяти.С помощью этого бита можно запретить (cd = 1) или разрешить (cd = 0) использование внутренней кэш-памяти (кэш-памяти первого уровня). · pg (PaGing), бит 31, — разрешение (pg = 1) или запрещение (pg = 0) страничного преобразования. Регистр cr2 используется при страничной организации оперативной памяти для регистрации ситуации, когда текущая команда обратилась по адресу, содержащемуся в странице памяти, отсутствующей в данный момент времени в памяти. Регистр cr3 также используется при страничной организации памяти. Это так называемый регистр каталога страниц первого уровня. Он содержит 20-битный физический базовый адрес каталога страниц текущей задачи. Этот каталог содержит 1024 32-битных дескриптора, каждый из которых содержит адрес таблицы страниц второго уровня. В свою очередь каждая из таблиц страниц второго уровня содержит 1024 32-битных дескриптора, адресующих страничные кадры в памяти. Размер страничного кадра — 4 Кбайт. Регистры отладки. Это очень интересная группа регистров, предназначенных для аппаратной отладки. Средства аппаратной отладки впервые появились в микропроцессоре i486. Аппаратно микропроцессор содержит восемь регистров отладки, но реально из них используются только 6. Регистры отладки DR0...DR3 - хранят 32-битные линейные адреса точек останова. DR6 (равносильно DR4) - отражает состояние контрольных точекDR7 (равносильно DR5) - управляет установкой контрольных точек. Регистры dr0, dr1, dr2, dr3 имеют разрядность 32 бит и предназначены для задания линейных адресов четырех точек прерывания. Используемый при этом механизм следующий: любой формируемый текущей программой адрес сравнивается с адресами в регистрах dr0...dr3, и при совпадении генерируется исключение отладки с номером 1. Регистр dr6 называется регистром состояния отладки. Биты этого регистра устанавливаются в соответствии с причинами, которые вызвали возникновение последнего исключения с номером 1. · b0 — если этот бит установлен в 1, то последнее исключение (прерывание) возникло в результате достижения контрольной точки, определенной в регистре dr0; · b1 — аналогично b0, но для контрольной точки в регистре dr1; · b2 — аналогично b0, но для контрольной точки в регистре dr2; · b3 — аналогично b0, но для контрольной точки в регистре dr3; · bd (бит 13) — служит для защиты регистров отладки; · bs (бит 14) — устанавливается в 1, если исключение 1 было вызвано состоянием флага tf = 1 в регистре eflags; · bt (бит 15) устанавливается в 1, если исключение 1 было вызвано переключением на задачу с установленным битом ловушки в TSS t = 1. Все остальные биты в этом регистре заполняются нулями. Обработчик исключения 1 по содержимому dr6 должен определить причину, по которой произошло исключение, и выполнить необходимые действия. Регистр dr7 называется регистром управления отладкой. В нем для каждого из 4 регистров контрольных точек отладки имеются поля, с помощью которых можно уточнить следующие условия, при которых следует сгенерировать прерывание: · Место регистрации контрольной точки — только в текущей задаче или в любой задаче. Эти биты занимают младшие восемь бит регистра dr7 (по два бита на каждую контрольную точку (фактически точку прерывания), задаваемую регистрами dr0, dr1, dr2, dr3 соответственно). Первый бит из каждой пары — это так называемое локальное разрешение; его установка говорит о том, что точка прерывания действует если она находится в пределах адресного пространства текущей задачи. Второй бит в каждой паре определяет глобальное разрешение, которое говорит о том, что данная контрольная точка действует в пределах адресных пространств всех задач, находящихся в системе. · Тип доступа, по которому инициируется прерывание: только при выборке команды, при записи или при записи/чтении данных. Биты, определяющие подобную природу возникновения прерывания, локализуются в старшей части данного регистра.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 1604; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.144.154.208 (0.059 с.) |