Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Обобщенная технология проектирования ПЛИС

Рынок программируемых логических интегральных схем (ПЛИС) бурно развивается и по своим темпам опережает все остальные технологии проектирования и изготовления ИМС. Объем рынка ПЛИС за 5 лет (с 1994 по 1999 г.г.) вырос в 5,3 раза. Бурный рост популярности ПЛИС объясняется в том числе и наличием хороших и довольно дешевых средств САПР ПЛИС. В отличие от САПР заказных и полузаказных ИМС, программные решения, используемые в САПР ПЛИС, базируются на надежных и эффективных алгоритмах и позволяют «закрыть» все этапы проектирования. Кроме того, такие системы в простейших случаях работают почти в автоматическом режиме. В начале 1980-х годов на мировой рынок микроэлектронных изделий вышли три ведущие фирмы-производителя ПЛИС. В июне 1983 года основана фирма Altera Corporation, в феврале 1984 — компания Xilinx, Inc., в 1985 году — Actel Corporation. Эти три компании на сегодняшний день занимают около 80 % всего рынка ПЛИС и являются основными разработчиками идеологии их применения. Если ранее ПЛИС являлись одним из множества продуктов, выпускаемых такими гигантами, как Intel, AMD и др., то начиная с середины 1980-х годов на рынке ПЛИС происходит специализация, и законодателями мод становятся фирмы, специализирующиеся только на разработке и производстве ПЛИС. Практически все фирмы-разработчики кристаллов ПЛИС поддерживают свои кристаллы средствами топологического проектирования и пакетами формирования файлов загрузки и программирования (так называемые программные средства нижнего уровня). Все эти программы являются приборозависимыми, и, конечно, решать такие задачи могут только разработчики кристаллов. Поэтому такие программные средства имеют все крупные компании-разработчики ПЛИС (например, Intel, AMD, Philips и др.). Ведущие фирмы-производители кристаллов ПЛИС (Xilinx, Altera и др.) поддерживают собственными САПР полный цикл проектирования собственных кристаллов и имеют соглашения с фирмами-разработчиками общецелевых САПР (Cadence, Mentor, Synopsys и др.) по включению пакетов нижнего уровня для своих кристаллов в эти общецелевые САПР. С разработчиками кристаллов ПЛИС тесно сотрудничают многие компании-разработчики программных средств, которые выходят на рынок САПР либо с собственными программными продуктами (например, OrCAD, Synopsys и др.), либо разрабатывают программные модули и включают их в САПР ведущих фирм-производителей ПЛИС (например, ALDEC).

Полный цикл проектирования ПЛИС, характерный для таких ведущих фирм, как Xilinx, Altera, Actel, Atmel, включает в себя следующие основные шаги: А. Ввод описания проекта. Различные САПР ПЛИС предлагают следующие основные средства ввода описаний проектов: - схемотехнический ввод с помощью графического редактора (Schematic Editor); - ввод описания на одном из языков высокого уровня: ABEL, VHDL, Verilog (HDL); - ввод диаграмм состояний конечного автомата с помощью соответствующего редактора состояний (FSM Editor). На данном этапе также вводятся временные и физические ограничения (Physical & Timing Constraints). Ввод описаний возможен также с помощью САПР третьих фирм, поддерживающих экспорт данных в промышленных стандартах описания электронных схем: Viewlogic, EDIF, VHDL, XNF, SXNF. Б. Функциональная верификация. На этом этапе с помощью подсистемы функционального моделирования (Functional Simulator) выполняется функциональная верификация проекта без учета временных характеристик выбранного кристалла с целью обнаружения ошибок в описании. В. Реализация проекта. На данном этапе выполняются следующие последовательные шаги: - компиляция описаний проекта, при котором описания, выполненные различными вышеуказанными способами, объединяются в единый файл проекта (Native Generic Design); - отображение списка цепей (netlist) в файл проекта с учетом выбранной целевой архитектуры кристалла (Mapping). Выполняется формирование списка в одном из промышленных форматов: EDIF, XNFc; - циклические размещение и трассировка проекта на кристалле с целью получения оптимизированного размещения проекта по одному из критериев: по площади, по скорости или баланс площади и скорости (Cyclic Place & Routing); Действия на данном этапе выполняются в автоматическом режиме. Пользователь имеет доступ к отчетам о выполненных шагах и может вмешаться в процесс реализации проекта с целью изменения настроек алгоритмов реализации. Г. Временная верификация. На данном этапе выполняется временной анализ размещенного и трассированного проекта с учетом знаний о временных характеристиках выбранного кристалла и пользовательских временных ограничениях (Timing Analysis).

Д. Формирование конфигурации. На этом этапе производится формирование двоичного файла конфигурации кристалла и аппаратная отладка проекта с помощью аппаратного отладчика (Hardware Debugger). Е. Форматирование файла PROM. На этом шаге двоичный файл конфигурации проекта обрабатывается для размещения в программируемом ПЗУ (PROM). Приведенный маршрут проектирования справедлив как для FPGA, так и для CPLD схем. В случае проектирования CPLD циклическое размещение и трассировка не выполняются, а имеет место монтаж проекта (fitting) в кристалле CPLD. Программное обеспечение САПР ПЛИС с полным циклом проектирования сегодня реализовано для всех платформ, включая PC, Unix, SUN и HP.

Информационные источники, использованные при подготовке раздела: [1],[2].

2.1.2 САПР производителей (вендоров) ПЛИС САПР ПЛИС, ввиду сложности новых разрабатываемых изделий, а в ряде случаев – ввиду значительных объемов серийного выпуска, наиболее эффективно разрабатываются и эксплуатируются, как правило, самими предприятиями-производителями. Рассмотрим возможности и методы решения задач автоматизированного проектирования ПЛИС с помощью САПР, разработанных основными участниками рынка производителей ПЛИС. САПР фирмы Actel Сo Американская компания Actel Corporation была основана в 1985 году. Особенностью ПЛИС, производимых этой компанией, является применение технологии Antifuse, представляющей собой создание металлизированной перемычки при программировании. Данная технология обеспечивает высокую надежность и гибкие ресурсы трассировки, кроме того, не требуется конфигурационное ПЗУ. По технологии Antifuse выпускаются семейства ACT1, ACT2, 1200XL, а также семейства SX, SX-A, eX, А40МХ, А42МХ (со встроенными модулями памяти), имеющие хорошие показатели «цена — логическая емкость». Данные ПЛИС являются хорошей альтернативой БМК при среднесерийном производстве. Микросхемы Actel, выпускаемые по технологии Antifuse, требуют применения специального программатора. Устройство Flash Pro предназначено для конфигурации в системе ПЛИС семейств Pro ASIC и Pro ASIC Plus и представляет собой дешевое и простое решение. ПЛИС Actel отличает высокая надежность, поэтому они являются весьма перспективной базой для специальных применений. ПЛИС фирмы Actel выпускаются в коммерческом и индустриальном диапазоне температур, а также с военной и космической приемкой. Для проектирования устройств на базе своих ПЛИС Actel предлагает сегодня пакет Libero (предыдущая известная разработка фирмы – САПР Design Series). ACTEL Libero v5.2 IDE представляет собой комплексный пакет средств проектирования ПЛИС, доступный даже для начинающих дизайнеров. В состав Libero IDE входят: ViewDraw от ACTEL (ввод HDL); Synplify от Synplicity (синтез); ModelSim от Mentor Graphics (верификация); Designer от ACTEL (размещение на кристалле); Libero IDE поддерживает все существующие на сегодняшний день ПЛИС ACTEL и выпускается в трех различных версиях: Libero Silver, Libero Gold и Libero Platinum. Возможности Libero IDE: Создание RTL-модели на языках Verilog и VHDL; Схематический ввод (schematic entry); Синтез на VHDL / Verilog; Трассировка и размещение на кристалле (place-and-route) с учетом физических характеристик ПЛИС; Проведение симуляции поведенческой модели VHDL или Verilog после синтеза и трассировки кристалла;

Симуляция и отладка в кристалле для получения "xорошей" верификации; Возможность реализации ПЛИС дизайна комбинируя схемный ввод и описание RTL модели на языке VHDL или схемный ввод и описание на языке Verilog. Выпускаются несколько различных программаторов: Silicon Sculptor II – программатор для всех семейств ПЛИС ACTEL (с переходными адаптерами для разных типов корпусов); Flash Pro – компактный программатор для всех семейств flash* ПЛИС; Flash Pro Lite – компактный программатор для flash семейства ProASICPLUS; Activator – программатор для antifuse ПЛИС первого поколения. Логические анализаторы: Silicon Explorer II – 18-канальный внутрикристальный логический анализатор; FS2 CLAM – внутрикристальный логический анализатор для flash ПЛИС. Маршрут проектирования в пакете Libero (design flow) включает следующие этапы: · создание проекта с помощью схемы, только как описание на языках описания аппаратуры и в смешанном режиме (mixed schematic-HDL flows); · синтез проекта; · моделирование; · программирование ПЛИС; · верификация системы. Создание проекта (Design Creation) осуществляется путем генерации по введенной схеме или описанию генерации списка цепей, проведении функционального и временного моделирования с использованием тестов (testbench/test fixture). Для ввода схемы (schematic capture) в пакете Libero используется графический редактор ViewDraw, который включает редактор схем (schematic editor) и редактор символов (symbol editor), позволяющий пользователю создавать собственные символы, что удобно при смешанном методе описания схемы. После ввода схемы генерируется список цепей в формате EDIF и производится трассировка проекта на ПЛИС. Функциональное моделирование (Functional Simulation) позволяет проверить правильность работы схемы. Для этих целей в пакете Libero используется широко известный продукт ModelSim. Кроме того, для генерации тестовых воздействий применяется продукт WaveFormer Lite фирмы SynaptiCAD. Трассировка проекта в выбранную пользователем ПЛИС осуществляется с помощью собственного продукта Designer, который также имеет средство анализа временных характеристик Designer's Timer tool, позволяющее провести статический анализ задержек сигналов на кристалле; средство размещения макросов ChipEdit; средство назначения контактов PinEdit. После размещения и трассировки проекта на кристалле с помощью пакета ModelSim выполняется временнóе моделирование (timing simulation).

Непосредственно программирование ПЛИС осуществляется с использованием программатора и программного средства Actel Designer. Программатор подключается к компьютеру через SCSI-контроллер (SCSI – Small Computer System Interface, промышленный стандарт параллельного интерфейса подключения периферийных устройств), который входит в комплект поставки. Тестирование ИС возможно или в программаторе, или прямо в устройстве, в котором предполагается использовать ИС. В этом случае для отладки используется устройство Actionprobe, с помощью которого можно полностью контролировать процессы, происходящие в любой точке схемы. Проект завершается верификацией всей системы (System Verification), осуществляемой с помощью средства Silicon Explorer (или FS2 CLAM).

Информационные источники, использованные при подготовке раздела: САПР фирмы ALTERA Фирма ALTERA, ориентирующаяся на выпуск семейств FPGA и CPLD схем (MAX7000, MAX9000, FLEX8000, FLEX10K и др.), предлагает для проектирования этих схем такие современные программные решения, как Quartus II и MAX+PLUS II. САПР MAX+PLUS II (Multiple Array matriX Programmable Logic User System – Пользовательская система программируемой логики матричных упорядоченных структур) представляет собой многоплатформную, архитектурно независимую интегрированную среду, обеспечивающую выполнение всех этапов, необходимых для выпуска готовых изделий: · создание проектов устройств; · синтез структур и трассировку внутренних связей ПЛИС; · подготовку данных для программирования или конфигурирования ПЛИС (компиляцию); · верификацию проектов (функциональное моделирование и временной анализ); · программирование или конфигурирование ПЛИС. В состав пакета MAX+PLUSII входят связанные между собой программные решения, реализующие все перечисленные выше этапы разработки цифровых устройств на ПЛИС фирмы ALTERA: - приложения для ввода проектов (редакторы проектов): -Graphic Editor – графический редактор, предназначенный для ввода проекта в виде схемы соединений символов элементов, извлекаемых из стандартных библиотек пакета либо из библиотеки пользователя; -Waveform Editor – редактор временных диаграмм (некоторые авторы называют это приложение сигнальным редактором), который выполняет двойную функцию: на этапе ввода обеспечивает ввод логики проекта в виде диаграмм (эпюр) состояний входов и выходов, а на этапе моделирования обеспечивает ввод диаграмм тестовых (эталонных) входных состояний моделируемого устройства и задание перечня тестируемых выходов; -Text Editor – текстовый редактор, предназначенный для создания и редактирования текстовых файлов, содержащих описание логики проекта на языке описания устройств AHDL (Altera Hardware Description Language) или на близких к нему языках типа VHDL, «Verilog»; -Symbol Editor – символьный редактор, позволяющий редактировать существующие символы и создавать новые. Кстати, любой откомпилированный проект может быть свёрнут в символ, помещён в библиотеку символов и использован как элемент в любом другом проекте;

-Floorplan Editor – редактор связей (поуровневый планировщик), который на плане расположения основных логических элементов позволяет вручную распределять выводы ПЛИС (закреплять выводы за конкретными входными и выходными сигналами) и перераспределять некоторые внутренние ресурсы ПЛИС. - приложения пакета компиляции Приложения этого базового пакета системы предназначены для синтеза структуры, трассировки связей, проверки корректности проекта и локализации ошибок, формирования файлов программирования или конфигурирования ПЛИС: -Netlist Extractor – приложение, обеспечивающее извлечение списка соединений из исходного файла представления проекта, созданного при вводе проекта; -Database Builder – приложение, предназначенное для построения базы данных проекта; -Logic Synthesizer – приложение, обеспечивающее проверку корректности проекта по формальным правилам и синтез оптимальной структуры проекта; -Partitioner– приложение, обеспечивающее разбиение проекта на части в тех случаях, когда ресурсов одного кристалла (микросхемы) недостаточно для реализации проекта; -Fitter – трассировщик внутренних связей, обеспечивающий реализацию синтезированной структуры; -SNF Extractor – приложение, обеспечивающее извлечение параметров проекта, необходимых для функционального моделирования и временного анализа. - приложения для верификации проектов -Simulator – приложение, которое совместно с редактором временных диаграмм предназначено для функционального моделирования проекта с целью проверки правильности логики его функционирования; -Timing Analyzer – приложение, обеспечивающее расчет временных задержек от каждого входа до каждого логически связанного с ним выхода. - приложение-программатор Программное решение MAX+plus II Programmer предназначено для программирования или конфигурирования ПЛИС. Программирование и перепрограммирование микросхем, имеющих встроенную систему программирования (ISP), может осуществляться непосредственно в составе конечного изделия через специальный кабель, подключаемый либо к LPT-порту (Byte Blaster), либо к COM-порту (Bit Blaster) компьютера и технологического 10-контактного соединителя интерфейса JTAG, устанавливаемого на плате изделия. Если на плате изделия устанавливается несколько ПЛИС со встроенными системами программирования, то все они могут программироваться через один технологический разъём. Для этой цели приложение имеет режим Multi-Device. - сервисные приложения В состав САПР MAX+PLUSII входят и три сервисных приложения: - Design Doctor – приложение, предназначенное для проверки корректности проекта с использованием эмпирических правил; - Message Processor – процессор сообщений, обеспечивающий обработку, вывод на отображение и локализацию (указание места в проекте, к которому оно относится) сообщений об ошибках («Error»), предупреждений («Warning») и информационных сообщений («Info»); - Hierarhy Display – приложение, обеспечивающее обзор иерархической структуры проекта, который может состоять из множества составленных в различных редакторах и свёрнутых в символы проектов более низких уровней, причём число уровней не ограничивается. Однако при этом основной проект (проект самого верхнего уровня) должен быть создан в графическом редакторе. САПР MAX+plus II Compiler разворачивается на PC платформе под Windows NT/XP. Имеется также версия САПР, работающая под Linux (Red Hat). Интерес представляет стратегия проектирования, в последнее время все шире используемая фирмой Altera (и другими фирмами также). Основная идея этой стратегии заключается в том, чтобы на начальных этапах проектирования использовать сторонние САПР, и лишь на заключительных этапах переходить на собственные программные средства.

Информационные источники, использованные при подготовке раздела: САПР фирмы ATMEL Корпорация ATMEL, основанная в 1984 г., является в настоящее время признанным мировым лидером в областях разработки, производства и маркетинга современных электронных компонентов, включая логические микросхемы с расширенными функциональными возможностями, микросхемы энергонезависимой памяти, а также интегральные схемы для радиочастотного диапазона и для смешанной обработки сигналов. Фирма Atmel является одним из ведущих производителей кристаллов ПЛИС. Фирма разработала свою САПР для ПЛИС – FPGA Designer 5.0 с HDLPlanner – это были первые средства разработки FPGA с автоматической генерацией архитектурно-независимых VHDL- или Verilog-поведенческих описаний и оптимизированной, детерминированной раскладкой FPGA для ряда семейств ПЛИС, выпускаемых фирмой (АТ6000 и АТ40К). Эти программные средства поддерживали также автоматическую генерацию повторно используемых IP-cores (ядер), которые могут быть использованы для ускорения проектирования. Имеется макрогенератор с устанавливаемыми пользователем параметрами, обеспечивающий быстрое создание архитектурно оптимизированных ядер и их файлов поддержки для оптимизированных под DSP архитектуру АТ6000 и АТ40К. Одновременно с созданием таких макросов FPGA Designer 5.0 автоматически генерирует схемотехнику и символику, VHDL или Verilog и выводит данные физической синхронизации в симулятор. Такие возможности позволяют улучшить характеристики FPGA на 70% и уменьшить размеры ПЛИС на 50% при существенном сокращении времени компиляции. Модуль HDLPlanner позволяет повысить производительность и эффективность разработки на основе поведенческих моделей и ядер. Генерируемые VHDL или Verilog коды могут подходить как для ПЛИС, так и для ASIC методологии проектирования. Учитывая функциональную совместимость с PLD фирмы ALTERA, можно использовать известный пакет MAX+PLUS II. В среде этого пакета создается схема и производится компиляция с последующей загрузкой выходного файла в микросхему PLD. Следует учесть, что САПР MAX+PLUS II не позволяет использовать расширенные возможности современных микросхем ATMEL. Поэтому фирмой были разработаны и сегодня предлагаются два специализированных программных продукта: Atmel WinCupl и Atmel Synario. ATMEL WinCupl представляет собой усеченную версию пакета WinCupl, разработанного фирмой LOGICAL DEVICES. WinCupl функционирует в среде Win95/98/NT и поддерживает все микросхемы SPLD и CPLD, выпускаемые фирмой ATMEL. Пакет позволяет провести все фазы проекта – ввод описания проекта в текстовом виде на языке Cupl (синтаксис языка близок к языку ABEL), компиляцию проекта (на выходе формируется стандартный JEDEC файл), а также временную симуляцию (в графическом виде). Существенный недостаток пакета – его малая мощность. Данный пакет пригоден для разработки лишь небольших проектов PLD схем фирмы ATMEL. Для серьезных проектов рекомендуется другое программное решение – Synario. Это профессиональная среда разработки, состоящая из нескольких компонентов: базового пакета (графический ввод, ABEL-описание, функциональная симуляция), Verilog-пакета функциональной и временной симуляции, пакета VHDL-синтеза и VHDL-симулятора.

Информационные источники, использованные при подготовке раздела: САПР фирмы MINC Inc. Фирма MINC Inc. (Франция) является одним из немногих европейских участников рынка САПР ПЛИС. Фирма является правообладателем двух широко известных пакетов – PLDesigner-XL для логического синтеза PLD и CPLD схем и ASYL+ для логического синтеза FPGA/CPLD схем (права на последний перешли к MINC Inc. после покупки ею фирмы-разработчика пакета Innovate Synthesis Technologies (IST)). Система PLDesigner-XL является стандартом де-факто в области логического синтеза PLD схем, включенным по OEM-соглашениям в большинство крупных пакетов САПР. Описание проекта в PLDesigner-XL задается на языке DSL (Design Synthesis Language), который обладает достаточно мощными выразительными средствами описания как комбинационной логики, так и конечных автоматов. Язык позволяет описывать и физические ограничения на синтезируемый проект: типы устройств, используемых для реализации проекта, назначение сигналов на выводы микросхем, специфические для каждого типа кристаллов ограничения и условия и т.п. Недостатком языка является его “нестандартность”, что ограничивает область его применения относительно небольшими проектами. Под нестандартностью понимается несовместимость языка DSL с такими промышленными стандартами, как VHDL и Verilog, отсутствие развитых систем моделирования для него. Для преодоления этого недостатка система PLDesigner предоставляет дополнительную возможность описания проекта на ограниченных подмножествах стандартных языков VHDL, Verilog. Для полного подмножества VHDL, Verilog можно использовать систему ASYL+, которая тесно связана и интегрирована с PLDesigner. Компания MINC рекомендует для синтеза с языков VHDL и Verilog использовать развитые средства кодирования автоматов, оптимизации и разделения ресурсов и генерации макроячеек системы ASYL+. Интеграция этих систем сейчас настолько тесная, что в ближайшее время они, вероятно, сольются в одну систему логического синтеза ПЛИС. Кроме того, в систему встроена поддержка библиотек компонентов OrCAD, Viewlogic и стандартной библиотеки компонентов EDIF 2.0.0. Поддерживаются ПЛИС фирм: Xilinx, Actel, Altera, AMD, AT&T, Cypress, Motorola, Philips Semiconductor, Texas Instruments, Toshiba, и ряда других. При этом база данных системы различает кристаллы по типу корпуса, температурному диапазону и исполнению (коммерческое или военное). Система тесно связана со схемотехническими редакторами. Связь с системами моделирования осуществляется на уровне стандартных языков VHDL, Verilog с использованием продуктов других поставщиков. Система позволяет генерировать VHDL/Verilog-модели, учитывающие задержки для уже размещенных кристаллов, что позволяет моделировать затем весь проект на более высоком уровне платы или блока. Имеется своя собственная система моделирования на языке DSL, которая позволяет проверить правильность функционального описания проекта перед началом синтеза. Для задания тестовых последовательностей при моделировании используется специальный язык тестов PLD-XL Test Lanquage, который похож на Паскаль. Система тесно интегрирована и с программными и аппаратными средствами собственно программирования кристаллов. Помимо широкого набора методов оптимизации, отличительной особенностью ядра системы синтеза является автоматическая декомпозиция большого проекта на несколько корпусов PLD/CPLD. Система позволяет автоматически декомпозировать проект на несколько микросхем различных семейств, различных поставщиков и даже смешивать кристаллы PLD/CPLD и FPGA. Это является несомненным достоинством системы. Система может быть развернута на ПК, однако предъявляет к персональным компьютерам достаточно высокие требования.

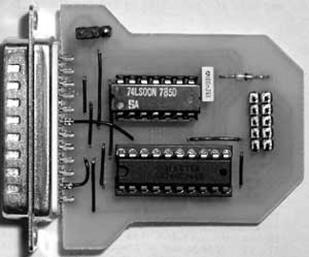

Информационные источники, использованные при подготовке раздела: САПР фирмы Xilinx Фирма Xilinx – разработчик ПЛИС, поставляет также САПР для разработки устройств на FPGA и СPLD. Пожалуй, из всех производителей ПЛИС фирма Xilinx может считаться лидером по номенклатуре серий ПЛИС и программного обеспечения (ПО). При этом новые версии ПО поддерживают старые серии ПЛИС, позволяя разработчику производить плавную миграцию проектов на новые серии. Первоначально фирма ориентировалась на поддержку своих САПР дополнительными программными средствами других компаний, интегрируя их под заказчика. Сегодня среди программных продуктов Xilinx имеются как относительно простые пакеты проектирования, так и мощные, интегрированные программные решения, позволяющие разрабатывать ПЛИС эквивалентной емкостью более 1000000 вентилей. Среди облегченных систем проектирования Xilinx следует выделить систему WebFITTER, особенностью которого является возможность использования в ходе проектирования web-ресурсов Internet. Альтернативой использованию WebFITTER является применение пакета WebPack ISE*, ориентированного на проектирование CPLD схем. В последней системе ввод описания проекта возможен как с помощью схемного редактора, так и с использованием языков описания аппаратуры ABEL и VHDL. Возможно программирование устройств непосредственно в системе с использованием аппаратного загрузчика XСhecker. Говоря о «тяжелых» САПР фирмы Xilinx, ориентированных на проектирование FPGA устройств, можно упомянуть САПР X-ACT. Первые версии САПР XACT (начало 90-х годов) включали: - один (любой) из перечисленных ниже пакетов графического схемного ввода: DASH-LCA (DS31, фирмы DATA I/O); OrCAD-SDT (DS35, фирма OrCAD); ViewDraw (DS390, фирмы ViewLogic); - один (совместимый с выбранным пакетом схемного ввода) из перечисленных ниже пакетов функционального и временного моделирования: PC-SILOS (DS22, фирмы SimuCAD); OrCAD-VST (DS351, фирмы OrCAD); ViewSim (DS290, фирмы ViewLogic); - пакет XACT (DS502) для проектирования всех микросхем FPGA фирмы Xilinx (семейства ХС2000/3000/3100/4000); - пакет DS501 - для микросхем семейств ХC2000/3000; - пакет DS550 для работы с EPLD. Позже, в 1996г., фирма выпустила единый пакет САПР XACTstep-5 для проектирования всех своих ПЛИС (как CPLD, так и FPGA). Кроме этого, фирма поддерживала САПР Alliance Series, базирующуюся на комплектовании программными средствами третьих фирм. Во второй половине 90-х (1997) для работы с FPGA, в том числе и с новым семейством Virtex, фирмой Xilinx в кооперации с Aldec и Synopsys был разработан мощный и современный пакет Foundation ISE, последние версии которого реализуют ряд новых функций, позволяющих использовать ПЛИС в качестве основной элементной базы для построения "систем на кристалле" (system-on-chip, SOC), а затем и полную САПР, объединяющую программы ввода, моделирования и топологического проектирования ПЛИС (Foundation Series ISE), что позволило получать модели новых ПЛИС одновременно с завершением их разработки. Поставляются три основных конфигурации пакета Foundation Series, различающиеся по своим функциональным возможностям и, соответственно, по стоимости. Типовой состав САПР Foundation Series Express включает следующие компоненты: 1. Foundation Project Manager. Это средство администрирования (управления) проектами в САПР. Из этой программы доступны все средства ввода, реализации, анализа и синтеза, а также отчеты о проектах. 2. Средства ввода описаний. Программное обеспечение формирует описания в формате EDIF(в более ранних версиях использовался формат XNF). В Xilinx Foundation Series Express имеются следующие подсистемы ввода описаний: o LogiBLOX. Данная программа позволяет, задавая параметры требуемой структуры устройства (ПЗУ, ОЗУ, счетчики и т.д.), получать готовые топологические фрагменты, которые могут использоваться как в схемных, так и в HDL-проектах; o редактор HDL-кода HDL Editor. Позволяет осуществлять ввод проектов на одном из языков HDL. Программа формирует список цепей netlist в формате EDIF (программа XVHDL). Поддерживает иерархическое представление проекта; o схемотехнический редактор Schematic Editor. Позволяет на основе библиотек САПР вводить принципиальную схему проекта в интерактивном режиме. Позволяет также включать LogiBLOX-модули, FSM-модули, VHDL- и Verilog-модули; o редактор диаграмм состояний (конечного автомата) State Editor. Позволяет вводить описание проекта в виде диаграмм состояний конечного автомата в графическом виде. В результате формирует поведенческое VHDL-описание; o COREgen. Это программное обеспечение позволяет встраивать в проекты ядра (COREs) любых модулей, например, мультиплексоры, DSP-модули, арифметические модули и любые иные макросимволы, являющиеся собственностью третьих фирм. Это средство позволяет существенно упростить и ускорить проектирование. 3. Средства моделирования схем: o программа функционально-логического моделирования Foundation Logic Simulator. Позволяет осуществлять функциональное моделирование проекта, а также временное моделирование с учетом задержек распространения сигналов по кристаллу. Результаты моделирования с учетом задержек полностью имитируют реальную картину работы ПЛИС, что практически исключает необходимость отладки кристалла на плате; o графический редактор директив оптимизации Constraints Editor. Позволяет устанавливать и изменять директивы пользователя при оптимизации временных параметров проекта; o программа VHDL синтеза FPGA Express. Выполняет синтез проекта на основе VHDL-кода; o программа моделирования на основе VHDL - VHDL Simulator. HDL-моделирование помогает верифицировать проект еще на стадии проектирования; o программа временного анализа Timing Analyzer. Выполняет точный расчет задержек по результатам размещения проекта в кристалле. 4. Средства трассировки и программирования: o трассировщик Flow Engine. Представляет собой набор трансляторов и программ, осуществляющих в автоматическом режиме преобразование выходного формата схемотехнического редактора во внутренний формат описания ПЛИС Xilinx; o топологический редактор Floorplanner. Позволяет дополнительно оптимизировать временные задержки путем переразмещения проекта в кристалле. С помощью данного средства можно менять положение CLB в общей структуре проекта на кристалле; o топологический редактор EPIC. Позволяет осуществить просмотр топологии проекта после трассировки и при необходимости выполнить ручную трассировку выбранных цепей; o утилита загрузки конфигурации ПЛИС непосредственно из PC Hardware Debugger. Загрузка осуществляется с помощью специального кабеля. Кроме того, с помощью этой утилиты выполняется верификация ПЛИС через порт JTAG (рис. 2.1); o

Рисунок 2.1 - JTAG-программатор 5. Специализированные библиотеки проектирования (доступны библиотека схемотехнических элементов (от простейших логических элементов до сложных счетчиков и элементов памяти), продукты LogiCore (сложные функции ЦОС, интерфейсы и др.), и т.д.). В новых версиях ПО поддерживаются расширенные библиотеки отлаженных и готовых к использованию ядер (Intellectual Property Cores), которые становятся очень важными при создании проектов больших размеров, сокращают сроки и упрощают проектирование. Информационные источники, использованные при подготовке раздела:

|

|||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 593; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.135.183.89 (0.097 с.) |

утилита для работы с программатором PROM File Formater.

утилита для работы с программатором PROM File Formater.