Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

До виконання лабораторних робіт з курсу «комп’ютерна електроніка»Стр 1 из 9Следующая ⇒

Методичні вказівки До виконання лабораторних робіт з курсу «Комп’ютерна електроніка» для студентів спеціальності 7.05020101 «Комп’ютеризовані системи управління та автоматики» Міністерство освіти і науки України Вінницький національний технічний університет

Методичні вказівки До виконання лабораторних робіт з курсу «Комп’ютерна електроніка» для студентів спеціальності 7.05020101 «Комп’ютеризовані системи управління та автоматики» Вінниця ВНТУ

Рекомендовано до друку Методичною радою Вінницького національного технічного університету Міністерства освіти і науки України (протокол № -- від --.--.---- р.)

Рецензенти: В.М. Севастьянов, к.т.н., доцент кафедри МПА М.М. Биков, к.т.н., професор кафедри КСУ

Методичні вказівки до виконання лабораторних робіт з курсу «Комп’ютерна електроніка» для студентів спеціальності 7.05020101 «Комп’ютеризовані системи управління та автоматика» / Уклад. Кривогубченко С.Г, Кулик Я.А. – Вінниця: ВНТУ, 2015. – 50 с. У даних методичних наводяться основні рекомендації до вивчення, підготовки та проведення лабораторних занять з дисципліни «Комп’ютерна електроніка».

ЗМІСТ

Опис лабораторного стенду. 5 Лабораторна робота №1. 6 Дослідження роботи логічних елементів і найпростіших комбінаційних схем 6 Лабораторна робота №2. 12 Дослідження роботи тригерів. 12 Лабораторна робота №3. 16 Дослідження роботи генераторів та формувачів електричних імпульсів. 16 Лабораторна робота №4. 25 Дослідження роботи регістрів. 25 Лабораторна робота №5. 29 Дослідження роботи лічильників імпульсів. 29 Лабораторна робота №6. 34 Дослідження роботи подільників частоти. 34 Лабораторна робота №7. 38 Дослідження мультиплексорів. 38 Лабораторна робота №8. 41 Дослідження роботи кодуючих і декодуючих пристроїв. 41 Лабораторна робота №9. 44 Моделювання роботи функціональних вузлів цифрової техніки. 44 Література. 49

Опис лабораторного стенду

1. Живлення стенду здійснюється від однофазної мережи змінної напруги 220 В з частотою 50 Гц. Кнопка "мережа" з фіксацією для увімкнення мережевої напруги знаходиться у верхньому лівому куті лицевої панелі стенду. При увімкненні стенду поруч з кнопкою увімкнення загоряється світлодіод.

2. Більшість логічних елементів та інтегральних схем, зображених на лицевій панелі стенду, доповнено світлодіодними елементами індикації, за допомогою яких можна спостерігати логічні вихідні рівні відповідних елементів схем. 3. При увімкненні стенду тригерні елементи схем довільно установлюються у будь-який з логічних станів "0", або "1". Тому при увімкненні стенду в мережу загоряються світлодіоди різноманітних елементів. 4. На всіх виходах елементів, до яких підключені світлодіодні елементи індикації, засвіченому стану світлодіода відповідає високий рівень позитивної напруги (рівень логічної одиниці). Виняток складають тільки мікросхеми DD2 і DD3 дешифраторів, у яких засвіченому стану їх виходів відповідає низький рівень напруги (рівень логічного нуля). Таке підключення елементів індикації викликане методичною доцільністю, пов'язаною з наочністю функціонування зазначених мікросхем. 5. Стенд виконаний на мікросхемах ТТЛ структури. В зв'язку з цим, якщо на входи таких мікросхем не подані логічні сигнали (входи не з'єднані провідниками з іншими елементами), це рівнозначно подачі на них рівня напруги, відповідного рівню логічної одиниці. 6. При з'єднанні входів мікросхем з шинами нульового потенціалу стенду необхідно спочатку штекер з'єднувального провідника з'єднати з відповідним входом мікросхеми. 7. Генератор тактових імпульсів стенду (ГТІ) виробляє прямокутні імпульси. При натиснутій кнопці, розміщеній у полі умовної позначки ГТІ, частота слідування імпульсів генератора становить 1 Гц, при віджатій – 100 кГц.

Лабораторна робота №1

Зміст звіту У звіті повинні бути представлені схеми та умовні позначення елементів, що досліджуються, таблиці їх станів, які ілюструють їх роботу, виміряні параметри, результати досліджень, висновки.

Лабораторна робота №2 Дослідження роботи тригерів

Ціль роботи - вивчення принципів роботи, засобу синтезу тригерів, виконаних на основі інтегральних мікросхем малого та середнього ступеня інтеграції, придбання навиків та уміння налагодження та перевірки працездатності схеми, що досліджується.

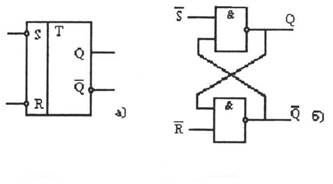

Теоретичні відомості Теоретичні відомості приведені в літературі [1, 2, 6, 7]. На рис. 2.1 - 2.4 показані умовні позначення тригерів та схеми для їх реалізації на логічних елементах "І-НЕ". На рис. 2.1 зображений RS-тригер з інверсними входами. Вихідний стан входів тригера в режимі збереження інформації відповідають рівню логічної одиниці. Для переключення тригера в одиничний стан необхідно короткочасно з'єднати вхід S тригера з нульовою шиною стенду. Для переключення тригера в нульовий стан необхідно короткочасно з'єднати вхід R з нульовою шиною стенду. При цьому вхід S тригера повинен мати потенціал логічної 1.

Рисунок 2.1 – RS – тригер з інверсними входами

Стан, при якому на обидва входи такого тригера подається рівень логічного нуля, є забороненим. При такому стані на обох виходах тригера з'явитися рівень логічної одиниці. На рис. 2.2 зображений RS-тригер з прямими входами. Стан входів у режимі збереження - рівні логічного нуля. Керуючі інформаційні сигнали повинні мати рівень логічної одиниці.

Рисунок 2.2 – RS-тригер з прямими входами

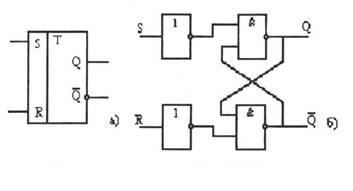

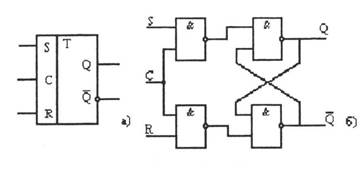

На рис. 2.3 зображена схема тактувального RS-тригера з прямими входами. Інформація в такий тригер заноситься шляхом подачі рівнів логічної одиниці на один із входів S або R та наступної подачі на тактувальний вхід С рівня логічної одиниці. При рівні логічного нуля на вході С тригер зберігає попередню інформацію і стан входів на його роботу не впливає.

Рисунок 2.3 – RS – тригер з прямими входами

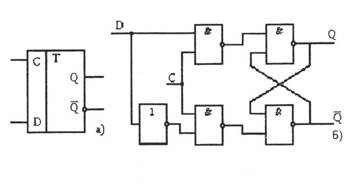

На рис. 2.4 зображена схема потенційного D-тригера. Інформація, подана на вхід D (логічний 0 або логічна 1), буде записана в тригер після подачі рівня логічної одиниці на вхід С.

Рисунок 2.4 – D -тригер

На лицьовій панелі стенду зображені мікросхеми DD6 - DD9, що представляють динамічні D-тригери. Інформація в такий тригер заноситься шляхом подачі на інформаційний вхід D з наступною подачею тактувального імпульсу на вхід С. Запис інформації в такий тригер здійснюється по передньому фронту тактувального імпульсу. Входи R і S такого тригера є пріоритетними. D-тригер можна використовувати у вигляді інверсного RS-тригера. Для побудови лічильного Т-тригера на базі D-тригера необхідно його інверсний вихід з'єднати з D-входом. На вхід С при цьому подаються імпульси лічби.

Завдання порядок виконання роботи

1. Вивчити роботу тригерів на логічних елементах. З існуючих на стенді логічних елементів скласти схеми тригерів, що досліджуються. Користуючись довідником по інтегральним мікросхемам (7), проставити номери виводів мікросхем на складених схемах тригерів. Зобразити часові діаграми роботи тригерів і скласти відповідні їм таблиці станів. 2. Зібрати послідовно схеми тригерів. Подати на їх входи відповідні інформаційні та керуючі сигнали. По результатам досліджень замалювати одержані часові діаграми і порівняти їх з раніше складеними при підготовці до роботи. 3. Вивчити роботу тригерів на інтегральних схемах. Користуючись довідником (7), замалювати їх схеми, умовні позначки і таблиці станів. Зобразити часові діаграми роботи тригерів відповідно до таблиці станів.

Подати на входи тригерів відповідні інформаційні та керуючі сигнали. По результатам досліджень замалювати одержані часові діаграми і порівняти їх з раніше складеними при підготовці до роботи. Визначити час переключення тригерів. Для цього необхідно: - з'єднати вхід зовнішньої синхронізації осцилографа з відповідним входом тригера; - переключити осцилограф у режим зовнішньої синхронізації, установити перемикач час/поділка в положення (0.2... 0.05) мкс/поділка та добитися появи непорушного зображення вхідного сигналу; - підключити вхід осцилографа до виходу тригера, визначити затримку розповсюдження логічного сигналу по зміщенню зображення вихідного сигналу на екрані осцилографа по відношенню до вхідного сигналу. Зміст звіту

У звіті повинні бути представлені схеми та умовні зображення схем тригерів, що досліджуються, часові діаграми і таблиці станів, що ілюструють їх роботу, виміряні параметри, результати досліджень, висновки.

Лабораторна робота №3 Лабораторна робота №4 Лабораторна робота №5 Лабораторна робота №6 Теоретичні відомості

Принципи роботи подільників частоти приведені в книгах (2, 3, 6, 7). Подільники частоти знайшли широке застосування в обчислювальній техніці, приладах автоматики, телемеханіки, управління, побутовій техніці. Подільниками частоти називаються прилади, що виробляють М вихідних імпульсів в відповідь на кожні N вхідних. Відношення N/M називається коефіцієнтом ділення. Подільники частоти з будь-яким коефіцієнтом ділення будують на основі додаючих або віднімаючих лічильників і логічних елементів. На рис. 6.1 показана схема подільника частоти з коефіцієнтом ділення 6, побудованого на основі додаючого двійкового лічильника, а на рис. 6.2 - часові діаграми його роботи.

Рисунок 6.1 – Лічильник-дільник з коефіцієнтом ділення 6

Рисунок 6.2 – Часова діаграма роботи лічильник

При надходженні шести імпульсів на додаючий вхід лічильника його виходи встановлюються в стан 0110, що відповідає цифрі 6 в десятковій системі числення. При цьому на всі чотири входи логічного елементу DD10 поступають рівні напруги, відповідні по величині логічній "1", а на виході цього елементу виникає напруга, відповідна рівню логічного нуля. Елемент DD19 інвертує його і рівень логічної одиниці, поступаючий на вхід R, скидає лічильник в нульовий стан. На виході логічного елементу DD10 з'явиться рівень логічної "1", на виході елементу DD19 - рівень логічного нуля, що переводить лічильник DD1 в режим рахунку. При подальшому надходженні вхідних імпульсів цикл роботи повторюється. Виходами дільника є вихід DD10 (вихідний імпульс - "від'ємний") або вихід DD19 (вихідний імпульс -"додатній"). Подібним же чином будуються і інші дільники частоти. В тих випадках, коли коефіцієнт ділення можливо розкласти на множники, дільник частоти можна зробити багатоступеневим, складається з декількох дільників з коефіцієнтами ділення, рівними відповідним множникам. Так, наприклад, якщо необхідно збудувати дільник частоти на 24, то його можна утворити шляхом ділення спершу на 2 (використовуючи один рахувальний тригер), а після цього його вихід з'єднати зі входом дільника на 12, збудованого на інтегральному лічильнику DD1 і логічних елементах згідно описаному вище принципу.

Деякі типи подільників (з заданим коефіцієнтом переліку, з коефіцієнтом переліку 3N) були розглянуті в роботі 5 при вивченні лічильників. На рис. 6.3 представлена схема подільника частоти з коефіцієнтом ділення 1,5. На рис. 6.4 - часові діаграми його роботи. Схема містить двійковий лічильник DD1 і суматор по модулю 2, виконаний на логічних елементах 2 І-НЕ. На лічильний вхід "+1" лічильника поступає вихідний сигнал схеми суматора по модулю 2, а на входи схеми суматора - тактовий сигнал і вхідний сигнал з другого розряду лічильника. Якщо на виході другого розряду лічильника встановлюється рівень логічного 0, то сигнал на виході суматора повторює вхідний тактовий сигнал з урахуванням деякої часової затримки. Якщо на виході другого розряду встановлюється рівень логічної 1, то тактовий сигнал на виході суматора інвертується. Це призводить до збільшення кількості переходів з 1 в 0 та з 0 в 1 на виході схеми суматора і викликає додаткові переключення лічильника DD1. У підсумку на виході "1" лічильника частота сигналу менше вхідної частоти не в 2, а в 1,5 рази, а на виході "2" - в 3 рази.

Рисунок 6.3 – Дільник частоти на 1,5

Рисунок 6.4 – Часові діаграми роботи дільника частоти на 1,5

Зміст звіту

У звіті повинні бути наведені схеми, часові діаграми, що ілюструють роботу подільників частоти, виміряні параметри, пропозиції з можливого застосування подільників частоти в конкретних технічних приладах, висновки.

Лабораторна робота №7 Дослідження мультиплексорів Ціль роботи - вивчення принципу роботи, методів синтезу мультиплексорів, виконаних на основі мікросхем малого і середнього ступеня інтеграції, придбання навиків і уміння складання та перевірки працездатності схем з використанням мультиплексорів.

Теоретичні відомості

Принципи роботи і методи синтезу мультиплексорів наведені у літературі (6, 7). Мультиплексором називається прилад, що забезпечує підключення деяких незалежних вхідних каналів на один вихідний. Мультиплексор аналогічний комутатору і служить для комутації (з'єднання) двійкових сигналів в різноманітних галузях цифрової техніки, де під терміном "мультиплексування" розуміють використання однієї і тієї ж шини у визначені (наприклад програмно) проміжки часу для передачі по ній різноманітної цифрової інформації (існують також мультиплексори для комутації аналогових сигналів).

Мультиплексор К155КП7, що використовується в лабораторному стенді, містить вісім інформаційних входів D0-D7, три керуючих входи А0-А2, вхід дозволу роботи мультиплексора Е. На входи управління (адресні входи) подається від зовнішніх приладів комбінація двійкового коду. При наявності дозволу на вході Е, з прямим виходом мультиплексора, з'єднується один із з входів D0-D7, десятковий номер якого відповідає двійковому коду, який подано на входи управління. Так, якщо на входи А0-A3 подана комбінація двійкового коду 011, то рівень напруги на 3-му вході буде поданий на прямий вихід мікросхеми. На рис. 7.1 приведена схема формувача паралельного коду у послідовний на основі мультиплексора.

Рисунок 7.1 – Формувач послідовного коду

Керуючі сигнали, що надходять на адресні входи мультиплексора А0-А2, виробляє двійковий лічильник К155ІЕ7, на підсумовуючий вхід якого надходять імпульси від ГОІ або ГТІ. При цьому двійковий код з інформаційних входів D0-D7 мультиплексора послідовно передається на прямий вихід мультиплексора і одночасно інвертується на його другому виході. На рис. 7.2 зображена схема мультиплексора, в «старт-стопному» режимі. Після натиску кнопки "ПУСК" (СТАРТ) починається передача необхідної інформації, поданої на інформаційні входи мультиплексора. Після завершення передачі всіх символів інформації схема автоматично виробляє сигнал припинення передачі - "Стоп".

Рисунок 7.2 – Мультиплексор в «старт-стопному» режимі Завдання і порядок виконання роботи

1. Вивчити принципи побудови і порівняти між собою мікросхеми К155КП1, К155КП2, К155КП5, К561КП1, К561КП2. Вивчити роботу мікросхеми К155КП7, записати паспортні дані та розробити і замалювати схеми перетворення паралельного 8-ми розрядного двійкового коду в послідовний. Збудувати часові діаграми роботи перетворювача. 2. Розробити і замалювати схему мультиплексора в «старт-стопному» режимі. 3. Запропонувати схему перетворювача паралельного коду у послідовний при числі інформаційних входів, які перевищують 16. 4. Зібрати послідовно схеми формувача послідовного коду та «старт-стопного» приладу на базі мультиплексора. Подати на входи зібраних приладів відповідні сигнали від ГОІ і ГТІ, зняти осцилограми роботи приладів і по результатам досліджень скласти часові діаграми їх роботи. Порівняти їх з розробленими при підготовці до роботи. 5. Розробити і зібрати схему зворотного перетворення послідовного коду з виходу мультиплексора в паралельний за допомогою універсального регістру К155ІР13. Дослідити роботу перетворювача послідовного коду в паралельний. Зміст звіту В звіті повинні бути представлені схеми формувача послідовного коду у циклічному і «старт-стопному» режимах, виміряні по осцилограмам параметри, схема перетворювача послідовного коду в паралельний на базі універсального регістру К155ІР13, часові діаграми роботи схем, висновки.

Лабораторна робота №8 Лабораторна робота №9 Література 1. Скаржепа В.А. Электроника и микросхемотехника. / В.А. Скаржепа, А.А. Новицкий, В.И. Сенько Лабораторный практикум. Под общ. ред. А.А. Краснопрошиной. - К.: Вища школа. – 1989. – 279 с. 2. Скаржепа В.А. Электроника и микросхемотехника. / В.А. Скаржепа, А.Н. Луценко Учебник: в 2 ч. Под ред. А.А. Краснопрошиной. - К: Вища школа. – 1989. – 303 с. 3. Хоровиц П. Искусство схемотехники. / П. Хоровиц, У. Хилл Искусство схемотехники. - М.: Мир. – 1984. – 598 с. 4. Князьков О.М. Лабораторные работы по основам промышленной электроники. / О.М. Князьков, А.Є. Краснопольський, П.С. Культиасов Под ред. В.Г. Герасимова. - М.: Высшая школа. – 1989. – 176 с. 5. Куценко В.М. Импульсные и цифровые узлы ЭВМ и техники связи. / В.М. Куценко, А.В. Згурский, Л.Д. Стащук Лабораторний практикум. - К.: Вища школа. – 1989. – 156 с. 6. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа. – 1987. – 318 с. 7. Кривогубченко С.Г. Функціональні перетворювачі систем автоматики і управління / С.Г. Кривогубченко, А.Я. Кулик, М.М. Компанець, А.Ф. Хомчук. Навчальний посібник. – Вінниця, ВНТУ, 2011. – 185 с. 8. Партала О.Н. Цифровая электроника / О.Н. Партала. СПб.: Наука и техника, Издательство Додэка –XXI. – 2007. – 224 с. 9. Угрюмов Е. П. Цифровая схемотехника / Е.П. Угрюмов. – СПб.: БХВ –Петербург. – 2004. – 528 с. 10. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования / Ю.В. Новиков. – М.: Мир. – 2001. – 379 с. 11. Гусев В.Г. Электроника и микропроцессорная техника / В.Г. Гусев. – М.: Высшая школа. – 2005. – 237 с. 12. Лаврентьев Б.Ф. Аналоговая и цифровая электроника / Б.Ф. Лаврентьев. – Йошкар-Ола: МарГТУ. – 2000. – 155 с. 13. Никамин В.А. Аналогово - цифровые и цифро-аналоговые преобразователи / В.А. Никамин. – М.: Техносфера. – 2003. – 145 с. 14. Комарова М.А. Использование LPT- порта ПК для ввода/ вывода информации / М.А. Комарова. – М.: НТ Пресс. – 2008. – 160 с. 15. Бабич Н.П. Основы цифровой схемотехники / Н.П. Бабич, И.А. Жуков. – М.: Издательство Додэка –XXI. – 2007. – 224 с. 16. Ан П. Сопряжение ПК с внешними устройствами / П Ан. – М.: ДМК Пресс. – 2001. – 320 с. 17. Ратхор Т.С. Цифровые измерения. Методы и схемотехника / Т.С. Ратхор. – М.: Техносфера. – 2004. – 376 с.

Методичні вказівки до виконання лабораторних робіт з курсу «Комп’ютерна електроніка» для студентів спеціальності 7.05020101 «Комп’ютеризовані системи управління та автоматики»

Редактор … Укладачі: Кривогубченко С.Г. Кулик Я.А.

Оригінал-макет підготовлено …

Підписано до друку …….. Формат 29,7´42¼. Папір офсетний. Гарнітура Times New Roman. Друк різографічний. Ум. др. арк. …... Наклад … прим. Зам. № 2015-

Вінницький національний технічний університет, навчально-методичний відділ ВНТУ. 21021, м. Вінниця, Хмельницьке шосе, 95, ВНТУ, к. 2201. Тел. (0432) 59-87-36. Свідоцтво суб’єкта видавничої справи серія ДК № 3516 від 01.07.2009 р.

Віддруковано у Вінницькому національному технічному університеті в комп’ютерному інформаційно-видавничому центрі. 21021, м. Вінниця, Хмельницьке шосе, 95, ВНТУ, ГНК, к. 114. Тел. (0432) 59-85-32. Свідоцтво суб’єкта видавничої справи серія ДК № 3516 від 01.07.2009 р. Додаток Б

Методичні вказівки до виконання лабораторних робіт з курсу «Комп’ютерна електроніка» для студентів спеціальності 7.05020101 «Комп’ютеризовані системи управління та автоматики» Міністерство освіти і науки України Вінницький національний технічний університет

Методичні вказівки

|

|||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 344; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.218.172.249 (0.127 с.) |