Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

DESTADDR2 - регистр 2 адреса получателя DMA-канала

Регистры DESTADDR0, DESTADDR1 и DESTADDR2 представляют 24-битное значение DESTADDR - адрес получателя DMA-канала. В регистре DESTADDR2 хранится старший байт этого значения. Значение DESTADDR может автоматически инкрементироваться или декрементироваться, в зависимости от установок бит DESTDIR (см. 5.14.3 "ADDRCTRL - регистр управления адресом DMA-канала"). Чтение и запись 24-битных значений необходимо выполнять с особым вниманием (см. 3.11.1 "Доступ к 24- и 32-битным регистрам").

8. Биты 7:0 - DESTADDR[23:16]: байт 2 адреса получателя DMA-канала В данных битах хранится байт 2 24-битного адреса получателя. DESTADDR1 - регистр 1 адреса получателя DMA-канала

9. Биты 7:0 - DESTADDR[15:8]: байт 1 адреса получателя DMA-канала В данных битах хранится байт 1 24-битного адреса получателя. DESTADDR0 - регистр 0 адреса получателя DMA-канала

10. Биты 7:0 - DESTADDR[7:0]: байт 0 адреса получателя DMA-канала В данных битах хранится байт 0 24-битного адреса получателя. Обзор регистров DMA-контроллера

Обзор регистров DMA-канала

Обзор векторов прерываний DMA

Таблица 5.13. Векторы прерываний DMA и смещения их адресов по отношению к базовому адресу прерываний DMA-контроллера

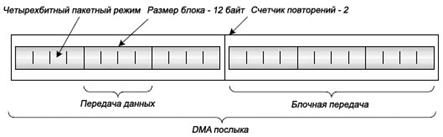

Использование DMA микропроцессора Xmega Автор: Mage 28.12.2011 09:36 Данная статья посвящена особенностям использования прямого доступа к памяти DMA в микропроцессорах Xmega. Прямой доступ к памяти (Direct Memory Access, DMA) — режим обмена данными между устройствами или же между устройством и основной памятью (RAM) без участия центрального процессора. Контроллер DMA (DMAC) в микропроцессорах Xmega является очень гибким четырехканальным контроллером, предназначенным для обмена данными между памятью и периферийными устройствами без вмешательства центрального процессора. Пока центральный процессор находится в спящем режиме или выполняет другие задачи, контроллер DMA берет на себя задачи по копированию данных из одной области в другую. Гибкий выбор приоритета канала, различные способы адресации, возможность двойной буферизации и большой объем делает контроллер DMA микропроцессора Xmega мощным инструментом для всех применений ориентированных на обмен данными, таких как обработка сигналов и промышленное управление. Пример использования DMA контроллера проиллюстрирован на следующем рисунке:

Каналы DMA В дополнение к общим регистрам у контроллера DMA есть четыре независимых канала с отдельно устанавливаемыми регистрами управления и состояния. Каждый канал имеет необходимую информацию по управлению и состоянию для одиночного DMA обмена: источник, адреса получателя, количество байтов и состояние. После завершения обмена, канал можно отключить, перенастроить для другого обмена или запустить на повторение предыдущей передачи.

Передача данных Понятие передачи данных в таком контексте подразумевает операцию, когда контроллер DMA копирует один, два четыре или восемь байтов от источника в заданное место в одной пакетной передаче. Когда канал DMA настроен на передачу двух, четырех или восьми байтов за раз, то контроллер, захватив шину, удерживает ее в течение передачи соответствующего количества байтов. Многобайтные пакеты полезны для передачи многобайтных регистров данных, например от АЦП, без риска того, что центральный процессор или другие DMA каналы, имеющие доступ к многобайтным регистрам испортят данные, хранящиеся во временных многобайтных регистрах. Длина пакета передачи настраивается в битовом поле режима придачи канала (BURSTLEN) в регистре управления (CTRL) по каждому каналу отдельно. Рис.1 иллюстрирует передачи данных в пакетном режиме.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 264; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.148.113.111 (0.01 с.) |