Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Арифметико-логическое устройство

Арифметико-логический блок реализует простейшие арифметические и логические операции (сложение, вычитание, сдвиги, сравнение, логическое умножение и т.д.). Все более сложные операции (умножение, деление, вычисление элементарных функций и др.) выполняются по подпрограммам. В его состав входят следующие основные узлы: - 8-разрядная схема АЛУ предназначенная для выполнения арифметических и логических операций над двоичными данными, представленными в дополнительном коде или двоично-десятичными данными; - аккумулятор (A), подключаемый к одному из входов схемы АЛУ, представляет собой 8-разрядный регистр и предназначен для хранения одного из операндов АЛУ, а также для запоминания результата операции; - буферный регистр (T), подключенный к другому входу схемы АЛУ, служит для временного хранения второго операнда АЛУ (программно не доступен). Он позволяет избежать возникновения «гонок», когда какой-либо из регистров общего назначения (РОН) используется в одной операции и в качестве регистра – операнда и в качестве регистра - результата; - схема десятичной коррекции предназначенная для коррекции результата при выполнении операции сложения двоично-десятичных данных. Для этого к старшей тетраде в схеме десятичной коррекции прибавляется число 6, если (A7…A4) > 9 или C = 1. К младшей тетраде (A3…A0) одновременно также прибавляется число 6, кроме случая отсутствия переноса из младшей тетрады, содержащей число от 0 до 9; - регистр признаков (FLAG) – пятиразрядный регистр признаков, предназначенный для хранения флагов, вырабатываемых АЛУ. При выполнении арифметических и некоторых других операций АЛУ вырабатывает следующие пять признаков: 1. С (Carry) - признак переноса. Устанавливается в «1», если при выполнении операции возник перенос из седьмого разряда сумматора или потребовался заем в седьмой разряд; 2. AC (Auxiliary Carry) – признак вспомогательного переноса. Устанавливается в «1», если при выполнении операции был перенос из третьего разряда сумматора в четвертый; 3. S (Sign) – признак знака. Устанавливается в «1», если старший значащий разряд результата равен единице, т.е. результат операции – отрицательное число; 4. Z (Zero) – признак нуля. Устанавливается в «1», если результат операции равен нулю;

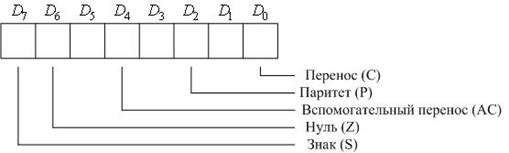

5. P (Parity) – признак четности. Устанавливается в «1», если число единиц результата операции четное. На рисунке 2.3 показан формат регистра признаков.

Рисунок 2.3. Формат регистра признаков Блок регистров Микропроцессор К580 содержит программно-доступные 8-разрядные регистры общего назначения (РОН) и 16-разрядные специализированные регистры: счетчик команд и регистр-указатель стека. Кроме того, имеются непосредственно недоступные программе регистры: 8-разрядные регистры временного хранения W, Z и 16-разрядный регистр адреса. Регистры общего назначения B, C, D, E, H, L используются для хранения операндов, промежуточных и конечных результатов, а также адресов и индексов при косвенной и индексной адресации. Для выполнения операций со словами двойной длины и операций формирования и пересылок двухбайтных адресов имеется возможность оперировать с содержимым пар регистров BC, DE, HL. Особенность блока регистров МП является наличие в его составе схемы инкремента/декремента (INC/DEC), которая производит над содержимым счетчика команд (PC) и регистра-указателя стека (SP) операцию прибавления/вычитания 1 без привлечения АЛУ. Счетчик команд (16-ти разрядный регистр) предназначен для хранения адреса команды; после выборки из оперативной памяти текущей команды содержимое счетчика увеличивается на единицу и таким образом формируется адрес очередной команды (при отсутствии безусловных и условных переходов). Указатель стека (16-ти разрядный регистр) служит для адресации стековой памяти. В МП К580 используется «перевернутый» стек, т.е. при передаче в стек слова значение указателя стека (адрес вершины стека) уменьшается, а при извлечении слова из стека увеличивается. Стековая адресация широко используется при работе с подпрограммами и в процедурах прерывания. Для кратковременного хранения некоторых операндов и результатов выполнения операций служат регистры временного хранения данных W, Z. Использование регистров временного хранения позволяет МП за один цикл выполнения команды реализовать, например, такую операцию, как обмен содержимым двух регистров. В состав блока регистров входит регистр адреса памяти (RA), предназначенный для хранения адреса ячейки памяти, в которой записана текущая команда. Регистр адреса недоступен программисту. Однако любая пара регистров (BC, DE, HL) может быть использована для задания адресов команд и данных в программе.

Буферные схемы Двунаправленный буфер шины данных предназначен для логического и электрического разделения внутрипроцессорной шины данных и внешней, системной шины данных. Буфер состоит из регистра-защелки и выходной схемы с тремя состояниями, т.е. схемы обеспечивающей на выходе состояния 0, 1 и полное отключение от нагрузки (высокоимпедансное состояние). В режиме ввода информации внутренняя шина данных подключается к регистру-защелке буфера, загрузку которого из внешней шины производит буферная схема под управлением команды. В режиме вывода информации буферная схема передает в шину данных содержимое буферного регистра-защелки, на вход которого по внутренней шине с одного из регистров загружена информация, подлежащая выдаче. Во время выполнения операций в МП, не связанных с процедурами обмена с внешними устройствами буферная схема отключается от шины данных. Во время выполнения операций в МП не связанных с процедурами обмена с внешними по отношению к МП устройствами системы, буферная схема отключается от шины данных, т.е. переходит в высокоимпедансное состояние (не нуль, не один). Буферная схема шины адреса – однонаправленная и обеспечивает передачу адресов команд и данных, а также номеров периферийных устройств от МП в систему. Выход буфера адреса, точно также как и буфера данных может переходить в отключенное состояние. Управляющее устройство Блок управления включает: - 8-ми разрядный регистр команд (RK), предназначенный для приема и хранения кода операции; - устройства управления и синхронизации (CU), формирующего управляющие сигналы для всех внутренних регистров и блоков МП, а также его выходные сигналы управления; - управляющей памяти, выполненной на программируемой логической матрице, в которой хранятся микропрограммы отдельных операций. Пользователь не может изменить содержимого управляющей памяти, а, следовательно, и состава команд.

|

||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 315; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.33.153 (0.01 с.) |