Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Тема. Дослідження схемних елементівСтр 1 из 6Следующая ⇒

Лабораторна робота № 1 Тема. Дослідження схемних елементів

Мета роботи – вивчення та засвоєння прийомів роботи з універсальними лабораторними стендами, вимірювальними приладами стендів, формувачами сигналів.

Універсальний лабораторний стенд Лабораторний стенд складається з трьох основних частин: поля для дослідження цифрових схем (ліва частина), індикаторного поля (середня частина), поля для дослідження аналогових схем (права частина). До складу лівого поля входять: 1. логічні елементи – універсальні синхронні D та JK- тригери з входами асинхронної установки R,S (активний рівень нульовий); – дешифратор 3*8 з інверсними виходами (типу ИД7); – мультиплексор 8*1 з інверсним виходом (типу КП7); – два чотирьохрозрядні універсальні регістри зсуву (типу ИР1); – два двійкових реверсивних лічильника (типу ИЕ7); – два двійково-десяткових реверсивних лічильника (типу ИЕ6); – два аналого-цифрових та цифро-аналоговий перетворювачі. Виходи мультиплексора, регістрів та двійкових лічильників постійно підключені до світлодіодних індикаторів. Для одержання логічних констант (логічний 0 та логічна 1) в стенді є точки, де формується логічна одиниця (у верхній частині поля) та логічний нуль у вигляді заземлення (по всьому полі). Для формування логічних змінних (кількістю не більше чотирьох) використовується тумблерний регістр. Існує можливість підключення тумблерного регістра до дешифратора, мультиплексора, регістра, лічильників з допомогою відповідної кнопки комутатора. Для формування синхросигналів використовуються дві кнопки з парафазними виходами (для ручного формування) та два генератори (для автоматичного формування). У лівій частині поля є відповідні гнізда, звідки можна одержати потрібні сигнали. На середньому полі розміщується 8-розрядний індикатор, до якого можуть бути підключені довільні точки схеми. На правому полі розміщуються схемні елементи та пристрої. Вимірювальний прилад Ф4372 Цифровий комбінований прилад типу Ф4372 дозволяє вимірювати напругу і силу струму постійного та змінного струму, частоту змінного струму, активний опір (результат виводиться у цифровому вигляді з допомогою 4-х десяткових розрядів). Крім того, прилад виконує функції осцилографа та генератора синусоїдальних коливань..

При вимірюванні за допомогою цифрового комбінованого приладу необхідно мати на увазі: – при вимірюванні необхідно натиснути кнопки виду роботи (І,U,R,f) і діапазону вимірювання; –при роботі у всіх режимах спочатку вибирають найбільший діапазон виміру, а потім, орієнтуючись на результати виміру, переходять на більш зручний для виміру діапазон. – при вимірюванні сили і напруги постійного струму, опору постійному струму, частоти кнопка “ -- \ ~ ” повинна бути у віджатому стані, при вимірюванні сили і напруги перемінного струму – у натиснутому. Для визначення величини напруги з допомогою осцилографа необхідно шляхом вибору значення коефіцієнта вертикального відхилення встановити зручну для спостереження величину зображення на екрані приладу. Значення цього коефіцієнту визначається натиснутою кнопкою перемикача V/ДЕЛ і установленим множником. Для спостереження низькочастотних сигналів і сигналів з постійною складовою необхідно перемикач ≈ \ ~ перевести в положення ≈. Стійке зображення установлюється вибором відповідного коефіцієнту розгортки (шляхом натискання кнопок перемикача ВРЕМЯ/ДЕЛ) та ручкою ПЛАВНО і вибором полярності синхронізації (кнопка ” +\– “).. Для визначення часових характеристик сигналу за допомогою осцилограми необхідно виміряти горизонтальну відстань між точками, що цікавлять, (ручка ПЛАВНО повинна бути в крайньому правому положенні) та помножити відстань, яку виміряли у великих розподілах, на показання ВРЕМЯ/ДЕЛ перемикача (наприклад, відстань між вимірюваними точками становить 5 великих розподілів, перемикач ВРЕМЯ/ДЕЛ встановлений у положенні 0,1ms, тоді тривалість часового інтервалу 5 * 0.1ms = 0,5ms.

Завдання 1. Ознайомитись зі складом та розміщенням мікросхем та схемних елементів на стенді. 2. Виміряти з допомогою цифрового комбінованого приладу схемні елементи, величину активного опору резистора з відомим номіналом. Визначити відхилення опору від номіналу 3. Одержати осцилограми вихідного сигналу генератора синусоїдальних коливань, що входить до складу комбінованого приладу. Визначити період Т, частоту f, амплітуду А сигналу.

4. Одержати осцилограму вихідного сигналу генератора прямокутних імпульсів та визначити амплітуду А, період Т, частоту f, тривалість імпульсу τ та коефіцієнт заповнення (відношення Т/τ) сигналу за допомогою осцилограми. 5. Виміряти з допомогою цифрового комбінованого приладу величину напруги логічної 1, що формується на стенді.

Зміст звіту 1. Титульний аркуш. 2. Назва та мета роботи. 3. Завдання. 4. Необхідні короткі теоретичні відомості для кожного з виконаних пунктів завдання. 5.Таблиці з результатами вимірювань та осцилограми з позначенням вимірюваних параметрів, результати розрахунку. 6. Висновки по роботі. 5.Контрольні запитання 1. Що входить до складу цифрових елементів стенду? 2. Як вимірюється величина напруги змінного струму з допомогою осцилографа? 3. Як вимірюється тривалість сигналу, період та тривалість імпульсів з допомогою осцилографа? 4. Як вимірюється комбінованим приладом стенда сила і напруга постійного струму? 5. Як вимірюється комбінованим приладом стенда опір постійному струму, частота?

Лабораторна робота № 2 Тема. Дослідження логічних елементів та комбінаційних цифрових схем Мета роботи – вивчення принципів роботи, методів синтезу та особливостей функціонування загальних типів комбінаційних схем, надбання навиків реалізації їх на реальних інтегральних елементах.

Логічні елементи Цифровий логічний елемент реалізує одну з операцій алгебри логіки або просту логічну функцію. Позначення найпростіших логічних елементів наведені на рис.1.

Рис.2.1 Схемні позначення логічних елементів: а - двовходового диз’юнктора; б - двовходового кон’юнктора; в - інвертора; г - двовходового елемента Пірса; д - двовходового елемента Шеффера

Таблиці істинності елементів, зображених на рис.2.1, наведені на рис.2.2.

Рис.2.2 Таблиця істинності логічних елементів: а - двовходового диз’юнктора; б - двовходового кон’юнктора; в - інвертора; г - двовходового елемента Пірса; д - двовходового елемента Шеффера

Завдання 1.Дослідити базові елементи логічних мікросхем та зрівняти результати вимірювань з відповідними таблицями істинності. 2. Для заданої функції згідно з варіантами побудувати комбінаційну схему з використанням елементів, що входять до складу стенда (2 елемента 2АБО–НЕ, 6 елементів 2І–НЕ). 3. Виконати мінімізацію та одержати МДНФ і МКНФ для функції згідно з варіантами. Для обох форм побудувати схеми з використанням елементів, що входять до складу стенда.

Таблиця 2.1

4. Побудувати генератор імпульсів за схемою рис. 2.3 для n =1,3,5. Для кожної схеми одержати осцилограми вихідного сигналу та визначити його амплітуду, період і частоту.

Рис2.3 Схема генератора імпульсів Зміст звіту 1. Титульний аркуш. 2. Назва та мета роботи. 3. Завдання. 4. Необхідні короткі теоретичні відомості для кожного з виконаних пунктів завдання. 5. Результати вимірювання. Мінімізація функцій, всі схеми, осцилограми з позначенням вимірюваних параметрів, результати розрахунку. 6. Висновки по роботі. 4. Контрольні запитання 1. Що таке МДНФ та МКНФ логічної функції? 2. Що таке комбінаційна схема? 3. Як проводиться мінімізація логічної функції? 4. Карти Карно двох, трьох та чотирьох змінних. 5. Методика синтезу комбінаційної схеми. 6. Логічні елементи І, АБО, І-НЕ, АБО-НЕ, Виключне АБО, НЕ. Умовні позначення, таблиці істинності.

Лабораторна робота №3 Шифратори Шифратор має m входів і n виходів ( На рис. 3.1 зображена структурна схема шифратора з т = 8, п = 3 (входи х0 – х7, виходи y0 – y2, х7 та y2 старші розряди). Наявність додаткового виходу z дозволяє відрізнити нульовий вихідний набір, який відповідає х0 = 1, від ситуації, коли всі вхідні сигнали дорівнюють нулю. В останньому випадку z теж дорівнює нулю. Шифратор реалізує логічні функції

z = x 0 + x 1 + x 2 + x 3 + x 4 + x 5 + x 6+ x 7.

а б Рис. 3.1. Функціональна схема (а) і умовне позначення (б) шифратора.

В обчислювальній техніці знаходять також використання пріоритетні шифратори, вихідний сигнал яких однозначно визначається при наявності декількох вхідних сигналів одночасно, що заборонено в звичайних шифраторах. Таблиці істинності звичайного та пріоритетного шифраторів наведені в табл.3.1 та табл.3.2 відповідно. Таблиця 3.1

Таблиця 3.2

Дешифратори Дешифратор має n входів, т ( Таблиця істинності дешифратора, функціональна схема та умовне позначення на прикладі дешифратора 4*10 (п = 4, т = 10) наведені в табл. 3.3 та на рис. 3.2 відповідно. Дешифратор, для якого т < 2n, називається неповним дешифратором на відміну від повного дешифратора, для якого т = 2n.

а б Рис. 3.2 Умовне позначення (а) та функціональна схема дешифратора (б).

Таблиця 3.3

Для неповного дешифратора набори вхідних сигналів від т до 2n -1 (тобто 1010... 1111) заборонені, тому значення виходів дешифратора на таких наборах невизначені (позначені х). Наведений дешифратор реалізує систему функцій

В умовному позначенні дешифратора (рис. 5) у лівому полі вказуються або номери входів, або їх вага в десятковій системі числення, а в правому – номери виходів, починаючи з нульового до т. Дешифратори використовуються також для синтезу комбінаційних схем. Як приклад побудуємо комбінаційну схему, що реалізує таблицю істинності (табл. 3.4), з допомогою дешифратора 3*8 з інверсними виходами.

Таблиця 3.4

З таблиці 3.4 видно, що функція Z1 має три одиничних набори та 5 нульових. Отже доцільно для її побудови використати ДНФ. Аналогічно для Z2 доцільно використати КНФ. Функції в відповідних формах мають вид:

де y i – інверсні виходи дешифратора.

Відповідна схема наведена на рис. 3.3.

Рис. 3.3 Комбінаційна схема на основі дешифратора Перетворювач коду Як приклад розглянемо побудову перетворювача звичайного трьохрозрядного двійкового коду в циклічний код Грея (у цьому коді позначаються клітини карти Карно). Таблиця істинності такого перетворювача наведена в табл. 3.5. Таблиця 3.5

За даними табл. 3.5 будуємо три карти Карно, щоб одержати три функції Y1=f1(Х2,Х1,Х0), Y2=f2(Х2,Х1,Х0), Y3=f3(Х2,Х1,Х0) (рис. 3.4).

Рис. 3.4. Карти Карно для вихідних функцій перетворювача кодів

Після мінімізації одержуємо такі функції:

Функціональна схема перетворювача наведена на рис. 3.6.

Рис. 3.6. Перетворювач двійкового кода в код Грея Завдання Дослідження шифраторів» ПОРЯДОК ВИКОНАННЯ РОБОТИ 1. Вивчити призначення, основи роботи та особливості застосування. Ознайомитися з основними принципами побудови схем шифраторів.

Таблиця 3.6

3. Використовуючи елементи стенду зберіть схему шифратора, отриману після перетворення КС, яка виконує рішення системи рівнянь, отриманої в завданні, в базис 2И-HE для трехразрядного чисел. Подайте на вхід необхідні сигнали і перевірте правильність функціонування зібраної схеми. Після закінчення досліджень оформити звіт. Дослідження дешифраторів» ПОРЯДОК ВИКОНАННЯ РОБОТИ 1. Вивчити призначення, основи роботи та особливості застосування. Ознайомитися з основними принципами побудови схем дешифраторів. Таблиця 3.7

3. Використовуючи елементи стенду, зберіть схему трехвходового дешифратора, отриману після перетворення КС, яка виконує рішення системи рівнянь, отриманої в завданні, в базисі 2І-HE. Подайте на вхід необхідні сигнали і перевірте правильність функціонування зібраної схеми. Після закінчення досліджень оформити звіт. Зміст звіту 1. Титульний аркуш. 2. Назва та мета роботи. 3. Завдання. 4. Необхідні короткі теоретичні відомості для кожного з виконаних пунктів завдань. 5. Етапи синтезу, таблиці істинності, всі схеми на елементах, що входять до складу стенду. 6. Висновки по роботі.

5. Контрольні запитання 1. Що таке шифратор і де він застосовується? 2. Наведіть функціональну схему звичайного шифратора та поясніть принцип його дії. 3. Що таке пріоритетний шифратор і де він застосовується? 4. Наведіть функціональну схему пріоритетного шифратора та поясніть принцип його дії. 5. Що таке дешифратор і де він застосовується? 6. Наведіть функціональну схему дешифратора та поясніть принцип його дії. 7. Як виконується побудова комбінаційних схем з допомогою дешифратора? 8. Як і з застосуванням якого типу виходів мікросхем реалізуються логічна функція «ТА»? 9. Який принцип побудови перетворювачів коду? 10. Дайте роз’яснення принципу побудови перетворювачів коду. 11. В яких пристроях застосовуються перетворювачі коду? 12. Чим визначається швидкодія комбінаційної схеми?

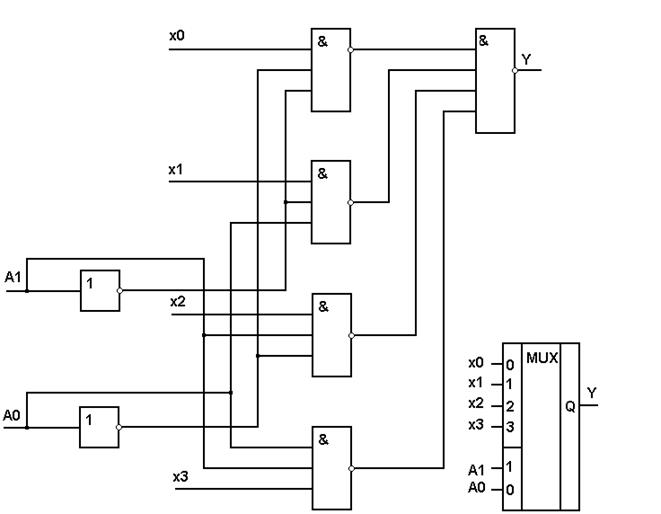

Лабораторна робота № 4 Мультиплексори. На рис. 4.1 зображена структурна схема мультиплексора „із 4 в 1”. На рис. 4.2 наведено мультиплексор „із 16 в 1” на основі чотирьох мультиплексорів „із 4 в 1”. Його інформаційні входи сполучаються з джерелами логічних сигналів „1” або „0” таким чином, що сигнал на вході відповідає таблиці істинності.

Рис. 4.1 Функціональна схема (а) та умовне позначення (б) мультиплексора „із 4 в 1”

Рис. 4.2. Приклад пірамідального каскадування мультиплексорів

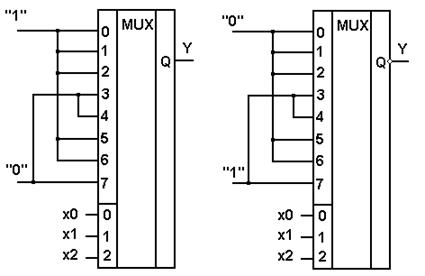

На рис. 4.3 наведені функціональні схеми, які реалізують логічну функцію, задану таблицею істинності табл. 4.1. Схеми побудовані з використанням простого настроювання мультиплексора. Таблиця 4.1

а б Рис. 4.3. Комбінаційні схеми з використанням простого настроювання мультиплексора з прямим виходом (а) або інверсним (б)

Методику складного настроювання мультиплексора розглянемо на прикладі функції табл. 4.1. Таблицю розіб’ємо на ділянки по два рядки так, щоб одна із змінних (Х0, Х1 або Х2) в цих рядках обов’язково змінювала своє значення, а інші залишались постійними. Приклади такого розподілу таблиці 4.1 наведені в таблиці 4.2. Вибрані змінні в таблиці 4.2 виділені курсивом. Таблиця 4.2

а б в Рис.4.4. Комбінаційні схеми з використанням складного настроювання мультиплексора з прямим виходом (а, б) або інверсним (в)

Демультиплексори Демультиплексор призначений для відновлення мультиплексованої інформації. На рис. 4.5 наведені функціональна схема (а) та умовне позначення (б) демультиплексора „із 1 в 4”.

а б Рис. 4.5. Функціональна схема (а) та умовне позначення (б) демультиплексора „із 1 в 4” Завдання «Дослідження мультиплексорів» ПОРЯДОК ВИКОНАННЯ РОБОТИ

1. Вивчити призначення, основи роботи та особливості застосування. Ознайомитися з основними принципами побудови схем мультиплексорів. 2. Виконати синтез мультиплексора «з 4 в 1» з наявних мікросхем логічних елементів. «Дослідження демультиплексорів» ПОРЯДОК ВИКОНАННЯ РОБОТИ

1. Вивчити призначення, основи роботи та особливості застосування. Ознайомитися з основними принципами побудови схем демультиплексорів. 2. Виконати синтез демультиплексора «з 1 в 4» з наявних мікросхем логічних елементів. Зміст звіту 1. Титульний аркуш. 2. Назва та мета роботи. 3. Завдання. 4. Необхідні короткі теоретичні відомості для кожного з виконаних пунктів завдання. 5. Етапи синтезу, таблиці істинності, всі схеми лише на елементах, що входять до складу стенду. 6. Висновки по роботі.

5. Контрольні запитання 1. Що таке мультиплексор і де він застосовується? 2. Принцип структурної організації мультиплексора. 3. Використання мультиплексора для побудови комбінаційних схем. 4. Що таке демультиплексор і де він застосовується? 5. Принцип структурної організації демультиплексора. Лабораторна робота № 5 Тема. Дослідження тригерів Мета роботи – вивчення принципів роботи тригерів та ознайомлення з функціональними схемами основних типів асинхронних і синхронних тригерів.

RS – тригери

В залежності від способу запису інформації RS – тригери поділяються на асинхронні та синхронні. Для створення асинхронного тригера достатньо двох однотипних логічних елементів. Найчастіше RS – тригери будують на логічних елементах І-НЕ чи АБО-НЕ. Умовні графічні позначення RS – тригерів з прямим та інверсним входами показані відповідно на рис. 5.1а, б.

а б Рис. 5.1. Умовні графічні позначення RS-тригера RS – тригер характеризується двома станами: логічною 1 (Q = 1, На рис. 5.2а показана функціональна схема асинхронного RS – тригера з інверсними входами на двовходових логічних елементах І-НЕ.

Рис. 5.2. Функціональна схема (а) асинхронного RS – тригера з інверсними входами та його часові діаграми напруг (б). Закон функціонування тригера наведено у таблиці переходу (табл. 5.1а), де Характеристичне рівняння RS – тригера має вигляд Qn+1 = S + Таблиця 5.1

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-09-18; просмотров: 238; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.166.98 (0.179 с.) |

) і перетворює m -розрядний унітарний код в n -розрядний двійковий код.

) і перетворює m -розрядний унітарний код в n -розрядний двійковий код.

;...,

;...,  .

. ;

; ,

,

01

01

00

00

0

0

0

0

1

1

;

; ;

; .

.

а б

а б

Стовпець Вх заповнюємо, порівнюючи значення вибраної змінної (у нашому випадку Х0 або Х2 відповідно) зі значенням функції (Y) для однієї ділянки. За даними табл. 4.2 а, б будуємо комбінаційні схеми на основі мультиплексора 4*1 (рис. 4.4 а, б). Якщо у мультиплексорі використовується інверсний вихід, то стовпець Вх заповнюють, порівнюючи вибрану змінну зі значенням інверсії функції (

Стовпець Вх заповнюємо, порівнюючи значення вибраної змінної (у нашому випадку Х0 або Х2 відповідно) зі значенням функції (Y) для однієї ділянки. За даними табл. 4.2 а, б будуємо комбінаційні схеми на основі мультиплексора 4*1 (рис. 4.4 а, б). Якщо у мультиплексорі використовується інверсний вихід, то стовпець Вх заповнюють, порівнюючи вибрану змінну зі значенням інверсії функції (

= 0) і логічним 0 (Q = 0,

= 0) і логічним 0 (Q = 0,

та

та  – інформаційні сигнали на вході тригера; Qⁿ – стан тригера на прямому виході до появи на входах інформаційних сигналів; Qn+1 – стан тригера на прямому виході після появи інформаційних сигналів (після його переключення).

– інформаційні сигнали на вході тригера; Qⁿ – стан тригера на прямому виході до появи на входах інформаційних сигналів; Qn+1 – стан тригера на прямому виході після появи інформаційних сигналів (після його переключення). 0

0