Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Усилители. Параметры и характеристики усилителей.Стр 1 из 9Следующая ⇒

Усилители. Параметры и характеристики усилителей. Усилителем называется устройство, предназначенное для увеличения мощности входного сигнала. Процесс усиления основан на преобразовании активным элементом (биполярным, полевым транзистором) энергии источника постоянного напряжения в энергию переменного напряжения на нагрузке при изменении сопротивления активного элемента под действием входного сигнала. Усилители сигналов являются базовыми устройствами для построения сложных аналоговых электронных устройств. В зависимости от того, какой электрод транзистора является общим для входной и выходной цепей, разли-чают три схемы включения для биполярных (БТ) и полевых транзисторов (ПТ) соответственно: с общей базой или общим затвором (ОБ или ОЗ); с общим эмиттером или общим истоком (ОЭ или ОИ); общим коллектором или общим стоком (ОК или ОС). коэффициент усиления по напряжению Кu = Uвых/Uвх; коэффициент усиления по току Кi = Iвых/Iвх; коэффициент усиления по мощности Кр = Рвых/Рвх. Для многокаскадных усилителей коэффициент усиления определяется произведением коэффициентов усиления отдельных каскадов, выраженных в абсолютных единицах:

Входное сопротивление усилителя представляет собой сопротивление между входными зажимами усилителя и определяется отношением входного напряжения ко входному току Zвх = Uвх/Iвх. Характер входного сопротивления зависит от диапазона усиливаемых частот. Выходное сопротивление определяют между выходными зажимами при отключенном сопротивлении нагрузки Zвых = Uвых/Iвых. Коэффициент демпфирования – отношение сопротивления нагрузки к выходному сопротивлению усилителя Кд = Rн/Rвых. Значение этого параметра лежит в пределах от 10 до 100. КПД – отношение выходной мощности, отдаваемой усилителем в нагрузку, к общей мощности, потребляемой от источника питания Чувствительность – напряжение, которое нужно подать на вход усилителя, чтобы получить на выходе заданную мощность. Динамический диапазон – отношение наибольшего допустимого значе-ния входного напряжения к его наименьшему допустимому значению D = Uвх макс/Uвх мин. Диапазон усиливаемых частот (полоса пропускания) – разность между верхней и нижней граничными частотами Δf = fв – fн, в которой коэффициент уси-ления изменяется по определенному закону с заданной точностью.

Линейные искажения определяются зависимостями параметров транзисторов от частоты и реактивными элементами усилительных устройств. Линейные искажения бывают трех видов: частотные, фазовые и переходные. Переходная характеристика усилителя.

Эта характеристика определяет процесс перехода усилителя из одного состояния в другое. Скачкообразное изменение входного напряжения позволяет выяснить реакцию усилителя на это воздействие сразу в двух режимах: переходном и стационарном. Характер переходного процесса в усилителе во многом зависит от наличия реактивных элементов L, C, которые препятствуют мгновенному изменению тока в индуктивности и напряжения на емкости. Напряжение на выходе не может измениться скачкообразно при подаче на вход импульса. Время, в течение которого фронт нормированной переходной характеристики нарастает от уровня 0,1 до уровня 0,9, называется временем нарастания tнар. Превышение мгновенного значения напряжения над установившимся называют выбросом δ и выражают в процентах. Существует так называемое критическое значение выброса, при котором δ не зависит от числа каскадов усилителя. Неравномерность вершины нормированной переходной характеристики обозначается через Δ, измеряется как и выброс в процентах от стационарного значения и не должна превышать 10 % для усилителей высоко- качественного воспроизведения.

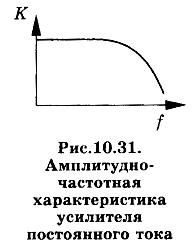

Усилители постоянного тока. Усилители постоянного тока (УПТ) предназначены для усиления медленно изменяющихся во времени сигналов.

Основными параметрами УПТ являются: коэффициент усиления по постоянному току

Если напряжение покоя предыдущего каскада изменяется под действием температуры или других факторов, то оно будет воспринято последующим каскадом как приращение, обусловленное воздействием входного сигнала, и будет далее усиливаться. Таким образом, в УПТ возникает явление, когда входной сигнал отсутствует, а на выходе усилителя присутствует постоянное напряжение некоторой величины. Такое явление называется дрейфом нуля. Различают абсолютный дрейф нуля 1) Температурный дрейф, вызванный температурной нестабильностью режима покоя в каскадах. Наиболее существенный вклад в дрейф усилителя вносят первые каскады, так как их дрейф усиливается последующими каскадами. 2) Старение элементов схемы. С течением времени изменяются как параметры самих транзисторов, так и остальных элементов каскада. 3) Нестабильность источников питания. Колебания напряжения источника питания приводит к колебаниям напряжения покоя и положения рабочей точки: При возникновении дрейфа нуля происходит смещение амплитудной характеристики усилителя.

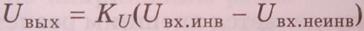

Операционные усилители. Операционный усилитель (ОУ) — усилитель постоянного тока с дифференциальным входом и, как правило, единственным выходом, имеющий высокий коэффициент усиления. ОУ почти всегда используются в схемах с глубокой отрицательной обратной связью, которая, благодаря высокому коэффициенту усиления ОУ, полностью определяет коэффициент передачи полученной схемы.

Инвертирующий вход – фаза на выходе не совпадает, неинвертирующий – совпадает. Идеальный ОУ имеет бесконечно большое входное сопротивление, нулевое выходное сопротивление и бесконечно большой коэффициент усиления. Параметры ОУ: смещение или напряжение сдвига нуля, входные токи смещения, разность входных токов, входное сопротивления, коэффициент ослабления синфазного сигнала, коэффициент шума, выходное напряжение и выходной ток, коэффициент усиления, полоса пропускания, скорость нарастания выходного напряжения, время установления выходного напряжения, время восстановления. Специфические параметры: коэффициент усиления дифференциального сигнала Kд = Uвых /Uвх д (дифференциальный сигнал – напряжения между одним из входов и общей точкой системы); коэффициент ослабления синфазного сигнала – Косл сф = Кд / Ксф (показывает, во сколько раз коэффициент передачи дифференциального сигнала больше коэффициента передачи синфазных сигналов), дифференциальное входное сопротивление (сопротивление со стороны любого входа при подключении другого к общей точке схемы).

Шумы в электронных схемах. ШУМЫ ЭЛЕКТРОННЫХ ПРИБОРОВ, электрические шумы, сопровождающие процессы генерирования, усиления или преобразования полезных сигналов электронными приборами. Определяют мин. (пороговую) величину полезного сигнала, при к-рой он ещё может быть воспроизведён или усилен без искажений, приводят к уширен и ю спектральной линии генерируемых колебаний. В общем случае вклад в Ш. э. п. вносят как естеств. шумы (дробовые, фликкерные, тепловые), так и техн. шумы. Вредное влияние естеств. Ш. э. п. на качество работы прибора может быть значительно ослаблено спец. техн. мерами, учитывающими физ. природу каждого из этих шумов. Так, для снижения уровня дробового шума в ЭВП используют такие режимы их работы, при к-рых ток катода меньше полного тока электронной эмиссии (режим пространств, заряда). При работе в таких режимах вблизи катода возникает минимум потенциала (виртуальный кагод), демпфирующий флуктуации тока катода (явление т. н. депрессии дробового шума пространств, зарядом). Указанный механизм успешно используется в диапазоне достаточно низких частот, для к-рого несущественно влияние эффектов, связанных с конечным временем пролёта эл-нов от катода к аноду (пролётных эффектов). В диапазоне СВЧ механизм подавления дробовых шумов значительно сложнее (см. Электронный поток). Для понижения дробового и фликкерного шумов ЭВП большое значение при разработке и изготовлении этих приборов придаётся повышению однородности катода, тщательному обезгаживанию, приведению всех узлов прибора и его параметров в стабильное состояние в ходе тренировки электронных приборов. Осн. путь снижения тепловых Ш. э. л. (как это следует из ф-лы Найквиста) — уменьшение активных потерь в элект-родинамич. системах приборов, понижение темп-ры (охлаждение приборов). Снижение уровня шумов в ПП приборах достигается след. мерами: уменьшением паразитных контактных сопротивлений; уменьшением времени пролёта носителей заряда; уменьшением ёмкостей ПП приборов; совершенствованием технологич. процесса с целью обеспечения заданного состава исходных материалов и профиля легирования разл. областей структуры ПП прибора (см., напр., Малошумящий транзистор). Технические Ш.». п. Применительно к ПП приборам термин «технические шумы» обычно не употребляется. Среди техн. шумов ЭВП осн. значение имеют шумы токораспре деле ни я, шумы вторичной электронной эмиссии, ионный шум, а также шумы контактные, вибрационные и др. Шумы токораспределеиия возникают из-за случайного перераспределения тока между электродами прибора, что приводит к увеличению флуктуации в его электронном потоке. Осн. средство борьбы с такими шумами — упучше-ние токопрокождения в приборе- Шумы вторичной электронной эмиссии заключаются в дополнит, флук-туациях ВЧ поля, индуцируемого вторичными эл-нами, испускаемыми электродами прибора (в основном коллектором). Такие шумы успешно подавляют, используя для электродов материалы с низким коэф. вторичной эмиссии, а также спец. конструкции коллекторных узлов, препятствующие проникновению вторичных эл-иов в электродина-мич. систему. Ионные шумы обусловлены электронно-ионными столкновениями, бомбардировкой катода ионами, а также плазменными колебаниями ионов, модулирующими ВЧ сигнал. Ионные шумы подавляются тщательным обезга-живанием прибора, устранением в нём ионных ловушек, в частности в области катода. К техн. шумам относят также Ш. э. п. в узкой полосе частот, напр. гудение, вызванное магн. полем тока подогревателя катода, микрофонный эффект, трески, возникающие при вибрации приборов -и попадании в их рабочее пространство посторонних ч-ц, шорохи, появляющиеся при ухудшении межэлектродной изоляции.

При количеств, оценке Ш. э. п. обычно отвлекаются от учёта каждого отд. источника шума, рассматривая нек-рые эквивалентные источники (генераторы шумового тока или шумового напряжения). Напр., шумовые св-ва электронных усилит, ламп характеризуют эквивалентным шумовым сопротивлением, находящимся при темп-ре 293 К и включённым на вход последовательно с источником сигнала. В др. случаях может рассматриваться согласованное с нагрузкой сопротивление, находящееся при нек-рй эквивалентной темп-ре, и ли акти вный четырёхполюсник, характеризуемый нек-рыми обобщёнными параметрами (шума коэффициентом или шумовой темп-рой). Инвертирующий усилитель

По цепи резистора Rо.с. выходной сигнал поступает на вход усилителя в противофазе со входным сигналом, и ОУ охвачен параллельной ООС по напряжению. Поэтому коэффициент усиления по напряжению ОУ определятся:

Минус указывает на инвертирование сигнала.

Входное сопротивление инвертирующего усилителя на ОУ Rвх.инв имеет относительно небольшое значение ввиду сильного влияния параллельной ООС по напряжению:

Выходное сопротивление инвертирующего усилителя невелико и определяется как небольшим Rвых.оу, так и глубокой ООС по напряжению:

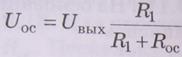

Неинвертирующий усилитель.

Напряжение обратной связи, снимаемое с делителя R1, Rос, пропорционально выходному напряжению усилителя:

Коэффициент усиления: Кuнеив=Uвых/Uвх=(R1+Rос)/R1=1+ Rос/R1 За счет глубокой последовательности ООС, охватывающей усилитель, и большого входного сопротивления ОУ Rвх.оу входное сопротивление неивертирующего усилителя велико и определяется: Rвх.неинв= Rвх.оу*Кuоу/Kuнеинв

Рис. Последовательный ключ на полевом транзисторе с управляющим pn-переходом Если в этой схеме управляющее напряжение Uупр установить меньшим, чем минимально-возможное входное напряжение, по крайней мере на величину порогового напряжения транзистора, транзистор закроется и выходное напряжение станет равным нулю. Для того, чтобы транзистор был открыт, напряжение затвор-исток Uзи следует поддерживать равным нулю, что обеспечивает минимальное сопротивление канала. Если же это напряжение станет больше нуля, управляющий pn-переход откроется, и выход ключа окажется соединенным с цепью управления. Если напряжение Uупр установить большим, чем максимально-возможное входное напряжение ключа, диод VD закроется и напряжение Uзи будет, как это и требуется, равно нулю. При достаточно большом отрицательном управляющем напряжении диод будет открыт, а полевой транзистор закрыт. В таком режиме работы через резистор R1 течет ток от источника входного сигнала в цепь управляющего сигнала. Это не мешает нормальной работе схемы, так как выходное напряжение ключа в этом режиме равно нулю. Нарушение нормального режима работы такой схемы может произойти лишь в случае, если цепь входного сигнала содержит разделительный конденсатор, который при закрытом транзисторе ключа зарядится до отрицательного уровня управляющего напряжения.

ДТЛ-логика Диодно-транзисторная логика (ДТЛ) — технология построения цифровых схем на основе биполярных транзисторов, диодов и резисторов. Своё название технология получила благодаря реализации логических функций (например, И) с помощью диодных цепей, а усиления сигнала — с помощью транзистора Принцип работы:

Показанная на рисунке схема представляет собой типичный элемент 2И-НЕ: Если хотя бы на одном из входов уровень логического нуля то ток R1 течет через диод во входную цепь. На анодах напряжение 0,7В, которого недостаточно для открывания транзистора, для того чтобы его ввести в режим насыщения. На выходе формируется уровень логической единицы. Если на все входы поступает уровень логической единицы, ток R2 течет через R1 в базу транзистора, образуя на анодах падение напряжения 1,4В. Поскольку напряжение уровня логической единицы больше этой величины входы диодов обратносмещены и не учавствуют в работе схемы. Транзистор открыт в режиме насыщения, ток нагрузки втекает в транзистор значительно больший по величине тока нагрузки при уровне логической единицы. Преимущества и недостатки: Основное преимущество ДТЛ над более ранней технологией РТЛ — возможность создания большого числа входов. Задержка прохождения сигнала по-прежнему достаточно высока, из-за медленного процесса утечки заряда с базы в режиме насыщения (когда все входы имеют высокий уровень) при подаче на один из входов низкого уровня. Эту задержку можно уменьшить подключением базы транзистора через резистор к общему проводу или к источнику отрицательного напряжения. В более современной и эффективной технологии ТТЛ данная проблема решена путём замены диодов на мультиэмиттерный транзистор. Это также уменьшает площадь кристалла (в случае реализации в виде интегральной схемы), и соответственно позволяет добиться более высокой плотности элементов. Логические элементы на основе ДТЛ являлись основой для многих ЭВМ второго поколения, например БЭСМ-6, IBM 1401.

КМОП логика

Для примера рассмотрим схему вентиля 2И-НЕ, построенного по технологии КМОП. Если на оба входа A и B подан высокий уровень, то оба транзистора снизу на схеме открыты, а оба верхних закрыты, то есть выход соединён с землёй. Если хотя бы на один из входов подать низкий уровень, соответствующий транзистор сверху будет открыт, а снизу закрыт. Таким образом, выход будет соединён с напряжением питания и отсоединён от земли. В схеме нет никаких нагрузочных сопротивлений, поэтому в статическом состоянии через КМОП-схему протекают только токи утечки через закрытые транзисторы, и энергопотребление очень мало. При переключениях электрическая энергия тратится в основном на заряд емкостей затворов и проводников, так что потребляемая (и рассеиваемая) мощность пропорциональна частоте этих переключений (например, тактовой частоте процессора).

ЭСЛ – логика. Эми́ттерно-свя́занная ло́гика (ЭСЛ) — семейство цифровых интегральных микросхем на основе дифференциальных транзисторных каскадов. ЭСЛ является самой быстродействующей из всех типов логики, построенной на биполярных транзисторах. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения, выход из которого замедлен. Низкие значения логических перепадов в ЭСЛ-логике способствуют снижению влияния на быстродействие паразитных ёмкостей. Основная деталь ЭСЛ-логики — схема потенциального сравнения, собранная не на диодах (как в ДТЛ), а на транзисторах. Схема представляет собой транзисторы, соединённые эмиттерами и подключенные к корпусу (или питанию) через резистор. При этом транзистор у которого напряжение на базе выше пропускает через себя основной ток. Как правило один транзистор в схеме сравнения подключен к опорному уровню, равному напряжению логического порога, а остальные транзисторы являются входами. Выходные цепи схемы сравнения поступают на усилительные транзисторы, а с них — на выходные эмиттерные повторители. Эмиттерный повторитель — способ включения транзистора, когда коллектор подключен к шине питания, а эмиттер является выходом. Напряжение на выходе эмиттера практически соответствует напряжению на базе, куда подаётся входной сигнал. Поэтому он и называется повторителем. Повторитель усиливает ток, не усиливая напряжения. Используется в основном для согласования высокого выходного сопротивление источника сигнала с малым сопротивлением нагрузки. Особенностью ЭСЛ является повышенные скорость (150 МГц уже в первых образцах 60-х годов и 0,5-2ГГц в 70-80хх) и энергопотребление по сравнению с ТТЛ и КМОП (на низких частотах, на высоких — примерно равное), низкая помехоустойчивость, низкая степень интеграции (ограниченная, в частности, большой потребляемой мощностью каждого элемента, что не позволяет разместить в одном корпусе много элементов, т.к. это приведёт к перегреву) и как следствие — высокая стоимость.

D-, T- триггеры. Тактируемый D-триггер. Он имеет информационный выход и вход синхронизации.

ТТЛ-, ТТЛШ-логика. Транзисторно-транзисторная логика наиболее распространена в современных вычислительных устройствах благодаря высокому быстродействию, высокой помехоустойчивости, умеренному энергопотреблению, хорошей нагрузочной способности и малой стоимости. Выходные и входные напряжения этих серий имеют так называемые стандартные уровни ТТЛ и одинаковые напряжения питания 5В.

В современных сериях широкое применение находят транзисторы Шотки. Как известно из принципа работы ключей на биполярных транзисторах, для предотвращения перехода транзистора в режим насыщения в них параллельно коллекторному переходу включается диод Шотки. Это, естественно, существенно повышает быстродействие. Для расширения функциональных возможностей логических элементов у некоторых типов микросхем в серии на выходе установлен транзистор, коллекторная цепь которого остается свободной. Это логические элементы с открытым коллектором. При использовании в схеме в коллекторную цепь включается резистор, светодиод или любая другая нагрузка.

Триггерная ячейка. Основу триггеров составляют простейшие запоминающие ячейки, представляющие собой симметричную структуру из двух логических элементов ИЛИ-НЕ либо И-НЕ, охваченных перекрёстной обратной связью:

Ячейки могут находиться в двух устойчивых состояниях: 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 соответствует единичный сигнал на выходе Q1. Вход, по которому ячейка устанавливается в состояние 1, обозначается буквой S, а в состоянии 0 – буквой R. Когда на обоих информационных кодах существуют логические нули (S=R=0), сигналы на выходе могут иметь одно из двух сочетаний: Q=1, Q1=0 либо Q=0, Q1=1, так как каждый логический элемент ИЛИ-НЕ инвертирует входные сигналы, а переключающим сигналом служит единица. Допустим, что Q=1. Этот сигнал, действуя на входе нижнего элемента создаёт на его выходе Q1=0. В свою очередь, на входах верхнего элемента два нулевых сигнала – со входа R и с выхода Q1, обеспечивает Q=1. Состояние это устойчивое. Если на один из входов подать единичный сигнал, сохраняя нулевой на другом, триггер примет состояние, которое однозначно определяется входной информацией. При входных сигналах S=1, R=0 триггер принимает единичное состояние Q=1, Q1=0, а при S=0, R=1 – нулевое: Q=0, Q1=1. При появлении управляющего сигнала на одном из входов происходит либо опрокидывание триггера, либо подтверждение существующего состояния, если оно совпадает с требуемым. Если одновременно подать переключающие сигналы на оба входа (S=R=1), на обоих выходах появятся логические нули (Q=Q1=0) и устройство утратит свойства триггера. Поэтому комбинацию S=R=1 называют неопределённой (н/о). Переход от неопределённой комбинации к нейтральной (S=R=0) называют запрещенной комбинацией, так как состояние выходов при этом восстанавливается, но с равной вероятностью оно может стать единичным, так и нулевым, т.е. ведёт к непредсказуемому поведению триггера. Триггер, который переключается сигналами логической единицы, т.е. на логических элементах ИЛИ-НЕ, называют триггером с прямым управлением (RS-триггер). Триггер, который переключается сигналами логического нуля, т.е. на логических элементах И-НЕ, называют триггером с инверсными входами (

Элемент И Логический элемент И выполняет операцию логического умножения (конъюнкция) над своими входными данными и имеет от 2 до 8 входов и один выход (как правило, выпускаются элементы с двумя, тремя, четырьмя и восемью входами). На рис. 1. изображены условные графические обозначения (УГО) логических элементов И с двумя, тремя и четырьмя входами соответственно. Элементы И обозначаются как NИ, где N - количество входов логического элемента (например, 2И, 3И, 8И и т.д.).

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкция) над своими входными данными и, также как и логический элемент И, имеет от 2 до 8 входов и один выход. На рис. 2. изображены УГО логических элементов ИЛИ с двумя, тремя и четырьмя входами соответственно. Элементы ИЛИ обозначаются также, как и элементы И (2ИЛИ, 4ИЛИ и т.д.).

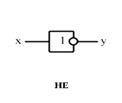

Элемент НЕ (инвертор) Логический элемент НЕ выполняет операцию логического отрицания над своими входными данными и имеет один вход и один выход. Иногда его называют инвертор, так как он инвертирует входной сигнал. На рис. 3 изображено УГО элемента НЕ. Элемент И-НЕ

Элемент ИЛИ-НЕ

Этот логический элемент выполняет логическую операцию сложения по модулю 2 и, как правило, имеет 2 входа и один выход. Такой элемент, в основном, используется в схемах аппаратного контроля. УГО элемента приведено на рис. Комбинационные логические элементы

Ключ на переключателе тока. Для повышения быстродействия ключевых схем используют переключатели тока, характеризующиеся тем, что при переключении схемы биполярный транзистор работает в активном режиме или на границе режима насыщения, когда коллекторный переход немного смещен в прямом направлении, при котором инжекция основных носителей из коллектора в базу незначительна.

Связь между транзисторами в переключателе тока осуществляется через генератор тока, включенный в неразветвленную цепь эмиттеров транзисторов.

Комплементарный ключ. Ключ состоит из двух последовательно включенных МДП-транзисторов с каналами n- и p-типа.

Важнейшей особенностью комплементарных ключей является то, что они практически не потребляют энергию в обоих состояниях. Микросхемы на комплементарных МДП-транзисторах имеют высокое быстродействие, поскольку перезаряд емкости нагрузки как при включении, так и при выключении происходит через открытый транзистор, однако их быстродействие меньше достигнутого биполярными микросхемами.

JK-триггеры. JK-триггеры подразделяются на универсальные и комбинированные. Универсальность JK-триггера состоит в том, что при соответствующем подключении информационных входов он может выполнять функции RS-, D-, T-триггеров. Комбинированный JK-триггер отличается от универсального наличием дополнительных входов S и R, предназначенных для предварительной установки триггера в определенное состояние (логической единицы или нуля).

Таблица состояний JK-триггера.

Мультиплексоры.

|

|||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-09-18; просмотров: 2144; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.225.35.81 (0.134 с.) |

(раз) или суммой коэффициентов усиления, выраженных в децибелах:

(раз) или суммой коэффициентов усиления, выраженных в децибелах:

.

. Переходная характеристика выражает зависимость от времени выходного напряжения усилителя, на вход которого подан мгновенный скачок напряжения (рис. 10.7).

Переходная характеристика выражает зависимость от времени выходного напряжения усилителя, на вход которого подан мгновенный скачок напряжения (рис. 10.7). Связь источника сигнала со входом усилителя и междукаскадные связи не могут быть осуществлены в УПТ с помощью реактивных элементов – конденсаторов и трансформаторов. Эти связи могут быть только непосредственными (гальваническими) - в этом случае выходное напряжение предыдущего каскада, содержащего постоянную составляющую режима покоя и приращение, вызванное воздействием входного сигнала, полностью подается на вход следующего каскада. Элементами гальванической связи могут быть резисторы, диоды, проводники.

Связь источника сигнала со входом усилителя и междукаскадные связи не могут быть осуществлены в УПТ с помощью реактивных элементов – конденсаторов и трансформаторов. Эти связи могут быть только непосредственными (гальваническими) - в этом случае выходное напряжение предыдущего каскада, содержащего постоянную составляющую режима покоя и приращение, вызванное воздействием входного сигнала, полностью подается на вход следующего каскада. Элементами гальванической связи могут быть резисторы, диоды, проводники. ; верхняя граничная частота

; верхняя граничная частота  , определяющая ширину полосы пропускания. Фазочастотная характеристика имеет отрицательный фазовый сдвиг в области верхних частот.

, определяющая ширину полосы пропускания. Фазочастотная характеристика имеет отрицательный фазовый сдвиг в области верхних частот.

(напряжение при нулевом входном сигнале) и приведенный

(напряжение при нулевом входном сигнале) и приведенный  (показывающий, какое постоянное напряжение обратной полярности требуется подать на вход усилителя, чтобы скомпенсировать величину абсолютного дрейфа). Величина дрейфа может меняться с течением времени. Причины возникновения дрейфа:

(показывающий, какое постоянное напряжение обратной полярности требуется подать на вход усилителя, чтобы скомпенсировать величину абсолютного дрейфа). Величина дрейфа может меняться с течением времени. Причины возникновения дрейфа:

Входной сигнал подан на инвертирующий вход, поэтому выходное напряжение находится в противофазе со входным напряжением. Резистор R1 учитывает также внутреннее сопротивление Rг источника сигнала Ег. Неинвертирующий вход соединен с общей шиной (землей) через резистор R2.

Входной сигнал подан на инвертирующий вход, поэтому выходное напряжение находится в противофазе со входным напряжением. Резистор R1 учитывает также внутреннее сопротивление Rг источника сигнала Ег. Неинвертирующий вход соединен с общей шиной (землей) через резистор R2.

Коэффициент усиления по напряжению:

Коэффициент усиления по напряжению:

В этом усилителе входной сигнал подается на неинвертирующий вход ОУ, а на инвертирующий вход подается сигнал обратной связи через делитель R1 и Rос.

В этом усилителе входной сигнал подается на неинвертирующий вход ОУ, а на инвертирующий вход подается сигнал обратной связи через делитель R1 и Rос.

При увеличении глубины ООС в неинвертирующем усилителе коэффициент усиления Kuнеинв уменьшается и при 100%-й ООС стремится к единице. Неинвертирующий усилитель становится повторителем напряжения.

При увеличении глубины ООС в неинвертирующем усилителе коэффициент усиления Kuнеинв уменьшается и при 100%-й ООС стремится к единице. Неинвертирующий усилитель становится повторителем напряжения.

КМОП (К-МОП; комплементарная логика на транзисторах металл-оксид-полупроводник; англ. CMOS, Complementary-symmetry/metal-oxide semiconductor) — технология построения электронных схем. В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки. Подавляющее большинство современных логических микросхем, в том числе, процессоров, используют схемотехнику КМОП.

КМОП (К-МОП; комплементарная логика на транзисторах металл-оксид-полупроводник; англ. CMOS, Complementary-symmetry/metal-oxide semiconductor) — технология построения электронных схем. В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки. Подавляющее большинство современных логических микросхем, в том числе, процессоров, используют схемотехнику КМОП. Технология:

Технология: Если уровень сигнала на входе C= 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе. При этом на входы RS-триггера с инверсными входами поступают пассивные уровни.При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D.

Если уровень сигнала на входе C= 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе. При этом на входы RS-триггера с инверсными входами поступают пассивные уровни.При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Здесь Qt означает логический уровень на прямом выходе до подачи импульса синхронизации, а Qt+1 - логический уровень на этом выходе после подачи импульса синхронизации.. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному на вход. на время паузы между синхросигналами. Тактируемые D-триггеры могут быть с потенциальным динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С=1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации.

Здесь Qt означает логический уровень на прямом выходе до подачи импульса синхронизации, а Qt+1 - логический уровень на этом выходе после подачи импульса синхронизации.. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному на вход. на время паузы между синхросигналами. Тактируемые D-триггеры могут быть с потенциальным динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С=1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации.  Схема базового логического элемента ТТЛ серии К155 приведена Базовый элемент состоит из входного каскада на многоэмиттерном транзисторе VT1, выполняющим функцию "И", каскада управления выходными ключами на транзисторе VT2 и выходных ключей VT3, VT4, выполняющих функцию усиления и инвертирования. При подаче на входы, или хотя бы на один из них, низкого уровня напряжения соответствующие эмиттерные переходы смещаются в прямом направлении. Ток базы транзистора VT3 определяется резистором R2 и он открыт. При этом на выходе логического элемента присутствует высокий уровень напряжения. При подаче на все входы высокого уровня напряжения напряжения эмиттерные переходы VT1 смещены в обратном направлении. На выходе логического элемента действует напряжение открытого до режима насыщения транзистора VT4 - низкий уровень. В соответствии с приведенным описанием базовый логический элемент ТТЛ выполняет логическую функцию "И-НЕ". В современных логических элементах для защиты от выбросов напряжения на входе обычно ставятся диоды.

Схема базового логического элемента ТТЛ серии К155 приведена Базовый элемент состоит из входного каскада на многоэмиттерном транзисторе VT1, выполняющим функцию "И", каскада управления выходными ключами на транзисторе VT2 и выходных ключей VT3, VT4, выполняющих функцию усиления и инвертирования. При подаче на входы, или хотя бы на один из них, низкого уровня напряжения соответствующие эмиттерные переходы смещаются в прямом направлении. Ток базы транзистора VT3 определяется резистором R2 и он открыт. При этом на выходе логического элемента присутствует высокий уровень напряжения. При подаче на все входы высокого уровня напряжения напряжения эмиттерные переходы VT1 смещены в обратном направлении. На выходе логического элемента действует напряжение открытого до режима насыщения транзистора VT4 - низкий уровень. В соответствии с приведенным описанием базовый логический элемент ТТЛ выполняет логическую функцию "И-НЕ". В современных логических элементах для защиты от выбросов напряжения на входе обычно ставятся диоды. // (В дальнейшем в шпоре Q c черточкой = Q1)

// (В дальнейшем в шпоре Q c черточкой = Q1) -триггер). Для такого триггера неопределённая комбинация (н/о): S=R=0.

-триггер). Для такого триггера неопределённая комбинация (н/о): S=R=0. Элемент ИЛИ

Элемент ИЛИ

Логический элемент И-НЕ выполняет операцию логического умножения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент И-НЕ - это элемент И с инвертором на выходе. УГО элемента 3И-НЕ приведено на рис..

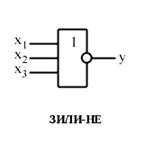

Логический элемент И-НЕ выполняет операцию логического умножения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент И-НЕ - это элемент И с инвертором на выходе. УГО элемента 3И-НЕ приведено на рис.. Логический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ - это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис.

Логический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ - это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис. Элемент сложения по модулю 2

Элемент сложения по модулю 2 Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис., сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4.

Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис., сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4. К одному из входов подается постоянное напряжение Ео, которое называется опорным. Это напряжение обеспечивает ток в общей цепи эмиттеров, равный Iэ, при котором транзистор работает в активном режиме.

К одному из входов подается постоянное напряжение Ео, которое называется опорным. Это напряжение обеспечивает ток в общей цепи эмиттеров, равный Iэ, при котором транзистор работает в активном режиме. Транзистор VT1 является ключевым, его исток соединен с заземленной шиной питания, а сток подсоединяется к стоку нагрузочного транзистора VT2. Подложка n-канального транзистора заземлена, а p-канального – подключена к положительному выводу источника питания Uи.п. Затворы обоих транзисторов объединены и являются входом ключа.

Транзистор VT1 является ключевым, его исток соединен с заземленной шиной питания, а сток подсоединяется к стоку нагрузочного транзистора VT2. Подложка n-канального транзистора заземлена, а p-канального – подключена к положительному выводу источника питания Uи.п. Затворы обоих транзисторов объединены и являются входом ключа. Триггер не имеет запрещенных комбинаций входных сигналов, и при J=K=1 осуществляется инверсия предыдущего состояния. При J=K=0 и при наличии синхросигнала на входе С состояние триггера не изменяется, так как сигнал логического нуля на одном входе элемента И-НЕ отменяет прохождение сигналов от других входов, и на выходе имеется сигнал логической единицы. Для перевода триггера в единичное состояние необходимо одновременное присутствие сигналов на C- и J-входах. При подаче на входы J и K одновременно напряжений логической единицы и наличие синхросигнала триггер переключается в состояние, противоположное предыдущем.

Триггер не имеет запрещенных комбинаций входных сигналов, и при J=K=1 осуществляется инверсия предыдущего состояния. При J=K=0 и при наличии синхросигнала на входе С состояние триггера не изменяется, так как сигнал логического нуля на одном входе элемента И-НЕ отменяет прохождение сигналов от других входов, и на выходе имеется сигнал логической единицы. Для перевода триггера в единичное состояние необходимо одновременное присутствие сигналов на C- и J-входах. При подаче на входы J и K одновременно напряжений логической единицы и наличие синхросигнала триггер переключается в состояние, противоположное предыдущем.