Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Конфигурируемая логическая матрица (CSL)

Логическая матрица располагает гибкими, программируемыми ресурсами для построения почти любых комбинаторных и последовательностных логических функций, непосредственно связана с внутренней системной шиной и является идеальной основой для создания программных модулей, необходимых микроконтроллеру. Матрица состоит из нескольких однотипных банков. Каждый банк представляет собой прямоугольный массив из логических ячеек, число которых зависит от модификации микросхемы. Наибольшей плотностью ячеек обладает микросхема ТЕ532, которая содержит 25 банков, расположенных в пять столбцов и пять строк, как показано на рис.17 и в таблице 6, наименьшей плотностью – микросхема ТЕ502, ее матрица содержит всего два банка.

Рис.17. Состав матриц пяти представителей семейства конфигурируемых систем на кристалле Состав логической матрицы микросхемы Таблица 6

Вертикальные и горизонтальные брейкеры разделяют банки между собой, как показано на рис.18, и являются частью системной шины. Горизонтальные брейкеры расположены между смежными колонками банков, а вертикальные – над каждым банком. Горизонтальные брейкеры предназначены для распределения адресных сигналов между банками, а вертикальные – распределяют входные и выходные сигналы селекторов, сигналы, используемые при отладке, сигналы временной задержки и буферные сигналы. Шина данных для чтения также размещена в вертикальных брейкерах. Сигналы от одного банка к другому могут передаваться только через брейкеры, что является причиной возникновения временной задержки. Сигналы Side-band возникают и распространяются только по периметру микросхемы.

Рис.18. Вертикальные и горизонтальные брейкеры разделяют банки логической матрицы Ресурсы банка Каждый банк состоит из 8 колонок и 16 строк логических ячеек, что, в общем, составляет 128 ячеек на банк, как показано на рис.19. Две смежные ячейки представляют собой элементарную основу сложных функций. На колонку из 16 логических ячеек приходится один селектор, который предназначен для передачи адреса.

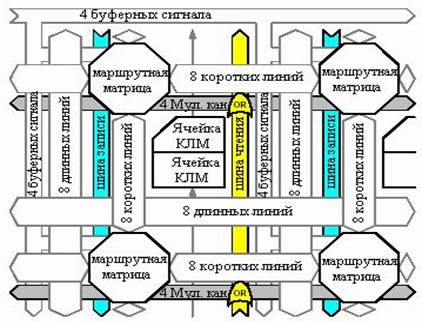

Вокруг ячеек расположена программируемая шина, которая позволяет взаимодействовать ячейкам между собой одного банка и с ячейками другого. По шине осуществляется передача сигналов к ячейке и обратно. Шина основного назначения Шина основного назначения, представленная на рис.20, предназначена для распределения сигналов внутри банка. Физические проводники различной длины и назначения связаны с каждой ячейкой в отдельности, с вертикальными и горизонтальными брейкерами, с массивом маршрутных матриц. Каждая маршрутная матрица обеспечивает связь между различными линиями, входящими и выходящими из сегмента. Ресурсы шины представлены ниже.

Рис.19. Каждый банк состоит из 8 колонок и 16 строк, что составляет 128 ячеек

Рис.20. Шина основного назначения 1. 8 коротких сегментных линий в каждом вертикальном и горизонтальном каналах; 2. 8 длинных линий в каждом вертикальном и горизонтальном каналах размещены по всей длине и ширине банка. Вертикальные линии предназначены для распределения выходных сигналов селекторов, размещенных в вертикальном брейкере, а горизонтальные линии – для распределения адресных сигналов, поступающих с системной шины; 3. шина тактирования и 3 из 6 буферных линий в каждом вертикальном канале (см. рис.21.). Сигналы тактирования подводятся ко всем ресурсам микросхемы, а 3 из 6 буферных сигналов предназначены для распространения внутри банка логической матрицы; 4. сигналы переноса и каскадирования предназначены для реализации быстрых арифметических и объемных логических функций.

Рис.21. В пределах банка логической матрицы доступны основные сигналы тактирования и 3 из 6 буферных сигнала Шина данных Помимо распространения сигналов общего назначения, программируемая шина предназначена для передачи и приема данных. 1. шина данных для записи доступна каждой маршрутной матрице. 2. 4 мультиплексорных канала проходят через весь банк и действуют подобно шинам с тремя состояниями, двунаправленные, с защитой от конфликта и с соответствующим энергопотреблением, поскольку все сигналы однонаправленные. 3. шина данных для чтения содержит значения с каждой линии данных со всего устройства, и все сигналы, таким образом, поступают на системную шину. Сигналы с каждой битовой линии объединяются через узлы логического сложения OR.

Рис.22. Шина данных для записи и чтения

Направления сигналов Шинная архитектура предполагает следующее распространение сигналов внутри матрицы, как показано на рис.23. Тактовые сигналы распространяются по вертикальным каналам, что преимущественно для буферных сигналов, имеющихся в распоряжении банка, или выгодно для прямого соединения тактовых входов ячеек с длинными вертикальными линиями. Сигналы контроля и разрешения также распространяются по вертикальным каналам. Адресные сигналы, дешифрированные селекторами, тоже предполагают распространение по вертикальным каналам, поскольку распределяются вертикальными линиями в вертикальных брейкерах. Объемные логические и арифметические функции требуют наличие встроенной шины каскадирования и расширения, которая предполагает вертикальное расположение, а именно, снизу вверх. Возможно и другое расположение, но в меньшей вероятности. Индивидуальные адресные сигналы системной шины распространяются по длинным горизонтальным линиям, а, следовательно, занимают горизонтальные каналы, как и двунаправленные мультиплексорные каналы.

Рис.23. Шинная архитектура предполагает соответствующее распределение сигналов Возможности ячейки матрицы Ячейка логической матрицы, представленная на рис.24. состоит из триггерных защёлок и комбинаторных функций, которые могут функционировать независимо друг от друга или в тандеме, в зависимости от реализуемой функции. Логическая ячейка является элементарной основой для реализации различных логических и арифметических функций, а также элементов памяти.

Рис.24. Ячейка логической матрицы В отдельности ячейка может выполнять следующие функции: 1. логическую; 2. арифметическую; 3. функцию памяти; 4. шины; 5. последовательностную. Большинство логических функций реализовано с использованием таблиц просмотра LUT – Look up table. Такая таблица предназначена для реализации любой функции с четырьмя входами и одним выходом, независимо от сложности логики. Специальный метод позволяет двум смежным ячейкам логической матрицы организовывать такую таблицу, но уже с пятью входами, и некоторые логические функции с числом входов до девяти. На рис.24. затемненные мультиплексоры предоставляют тот поток данных, который предопределяется в процессе конфигурации или после системного сброса внешним сигналом RST. Логическая функция Логическая ячейка способна выполнять множество комбинаторных функций при соответствующем числе входов, как показано в таблице 8. Используя одну ячейку, можно реализовать комбинаторную функцию любой сложности с числом входов до четырех, а, используя две ячейки в тандеме, функцию с пятью входами или от шести до девяти включительно. Реализуя последовательность функций с четырьмя или пятью входами, можно фактически увеличить разрядность функции. Производительность некоторых логических функций представлена в таблице 7. Логические функции и их производительность Таблица 7

Логические функции, реализуемые ячейками логической матрицы Таблица 8

Арифметическая функция Логическая ячейка способна выполнять простые арифметические функции, такие как сложение, вычитание и умножение. Функции, представленные в таблице 10, представляют собой общую структуру для построения сумматоров, аккумуляторов, инкрементных, декрементных и двоичных счетчиков, умножителей и других функций. Производительность некоторых арифметических функций представлена в таблице 9. Арифметические функции и их производительность Таблица 9

Арифметические функции, реализуемые ячейками логической матрицы Таблица 10

Функция памяти

Логическая ячейка способна выполнять различные функции памяти, включая ОЗУ с одним и двумя портами, ПЗУ и 8-ми разрядный регистр последовательного ввода/вывода. ОЗУ в составе каждой ячейки является идеальной основой для построения небольших регистровых файлов и области FIFO. Память, организованная на элементарных устройствах ОЗУ логической матрицы, отличается быстротой доступа и качеством хранения. Устройства памяти, реализуемые ячейками логической матрицы Таблица 11

ОЗУ с одним портом ввода/вывода (RAM 16 x 1, RAM 32 x 1) Логическая ячейка матрицы в качестве ОЗУ с одним портом ввода/вывода располагает следующими компонентами: 1. 4 адресных входа для памяти емкостью 16 бит и 5 адресных входов для памяти емкостью 32 бит; 2. одноразрядный порт ввода данных; 3. один вывод для сигнала разрешения записи, сигнал активен по уровню логической единицы; 4. инверсный вход синхронизации. Первоначальное содержимое ОЗУ может быть предопределено и загружено после сброса системы при включении питания. Операция записи синхронизирована тактовыми сигналами, что упрощает временное согласование данных, адреса и сигнала разрешения записи. Также, не возникает необходимости во временной задержке для какого-либо из входов ОЗУ после появления активного тактового сигнала на входе синхронизации. Операция чтения протекает асинхронно и зависит только от адресных входов. ОЗУ с двумя портами ввода/вывода (RAMDUAL) В этом случае ОЗУ, реализованное на двух логических ячейках матрицы, обладает соответствующими возможностями и достоинствами перед ОЗУ с одним портом ввода/вывода, поскольку позволяет одновременно выполнять операции записи и чтения, и располагает следующими компонентами: 1. два четырех – разрядных адресных канала для памяти емкостью 16 бит; 2. два одноразрядных порта ввода данных; 3. два вывода для сигналов разрешения записи, сигналы активны по уровню логической единицы; 4. один инверсный вход синхронизации; 5. детектор ошибки, который предназначен для выявления возможной ошибки при записи разных значений в одно и то же битовое размещение. Первоначальное содержимое ОЗУ может быть предопределено и загружено после сброса системы при включении питания. Операция записи синхронизирована тактовыми сигналами, что упрощает временное согласование данных, адреса и сигнала разрешения записи. Также, не возникает необходимости во временной задержке для какого-либо из входов ОЗУ после появления активного тактового сигнала на входе синхронизации.

Операция чтения протекает асинхронно и зависит только от адресных входов. ПЗУ (ROM 16 x 1, ROM 32 x 1) Одноразрядное ПЗУ может быть емкостью 16 или 32 бит, что в свою очередь влияет на число адресных входов. Для первого варианта достаточно четырех адресных входов, а для второго – пять. Значение адресных линий используется только в целях определения бита памяти, значение которого требуется считать. ПЗУ емкостью 16 бит организовано одной ячейкой матрицы, а ПЗУ емкостью 32 бит – двумя, работающими в тандеме. Содержимое ПЗУ определяется пользователем в процессе проектирования, загружается в процессе конфигурации и не может быть изменено в дальнейшем. 8-разрядный регистр последовательного ввода/вывода (SHIFT8) Последовательные данные поступают в регистр через вход SDI. Через вход DI можно задать значение определенного бита, на который указывает адрес на входах A[2:0], при этом сигнал SH (сигнал изменения/загрузки значения регистра) должен быть низкого уровня. Через вход SDI осуществляется последовательная загрузка значений битов регистра, начиная с нулевого и до седьмого, значение которого можно считать на выходе SDO. Значение бита, на который указывает адрес на входах A[2:0], можно считать с асинхронного выхода O. Сигнал EN разрешает либо запрещает какие-либо операции с регистром, если оказывается высокого либо низкого уровня соответственно. Последовательностная функция Каждая логическая ячейка состоит из триггерной защелки D–типа, которая содержит следующие входы управления: 1. вход сигнала разрешения, активного по уровню логической единицы; 2. инверсный вход тактирования по срезу; 3. асинхронный вход перезагрузки триггера, чтобы установить или очистить его в зависимости от того, что определит пользователь в процессе проектирования. В процессе конфигурации каждый триггер загружается значением логической единицы или нуля, как определит пользователь в процессе проектирования, и это значение защищено от случайной записи, которая может возникнуть еще до окончания процесса конфигурации. Последовательностные функции Таблица 12

«INITV» – первоначальное значение, которое определяется пользователем и загружается в процессе конфигурации. «ASYNCV» – значение для асинхронной перезагрузки, определяемое пользователем. 0* – активный уровень логического нуля, предусмотренный по умолчанию, если вывод окажется неиспользуемым. 1* – активный уровень логической единицы, предусмотренный по умолчанию, если вывод окажется неиспользуемым.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 418; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.218.218.230 (0.056 с.) |

F(4)

F(4)

F(5)

F(5)