Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

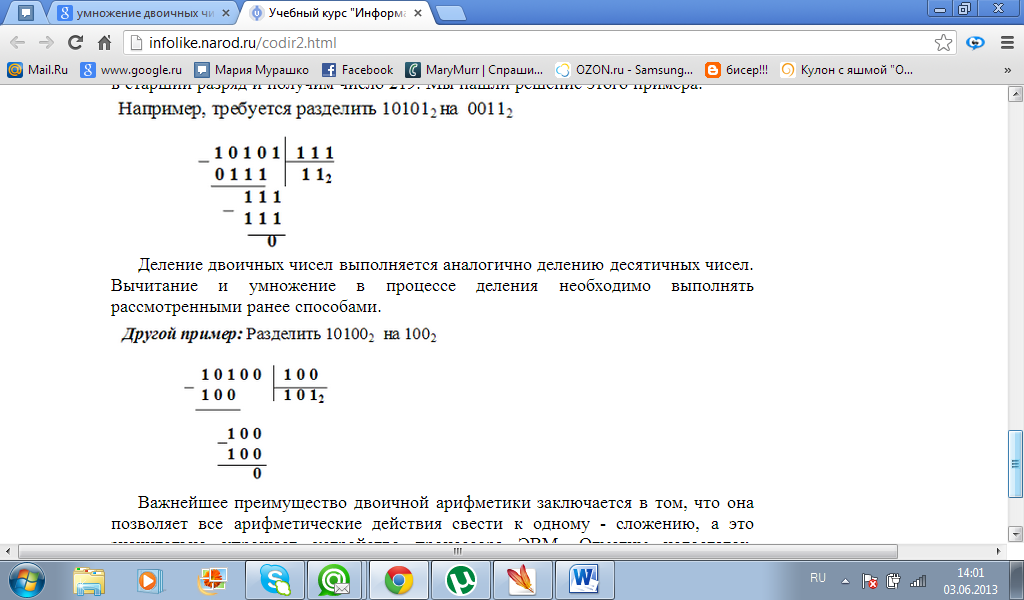

Умножение двоичного числа на 2. Для этого достаточно осуществить сдвиг влево на 1 разряд.

5 х 2 = 10 0101 = 10102 = 10

5.7.3 Деление на 2, осуществляется сдвиг вправо. Деление двоичных чисел.

Универсальная опрерационная схема. (арифметич. логич. АЛУ устройство) Pi Ai Входные I-ая ступень II-ая ступень III ступень Одноразрядные логической генерации формирова- Двоичные операции переходов тель суммы числа Bi

So S1 S2 S3 S4 Pi So, S1, S2, S3, S4 – входы для команды управления АЛУ.

Если записать последовательность микрокоманд в устройство памяти и поочередно считывать эти команды выполнения операций над числами Ai, Bi, то можно заставить работать АЛУ по определенной программе вычисления, причем промежуточные результаты сложно. ЗАМЕЧАНИЕ: для действия над n – разрядными двоичными числами потребуется «n» – малое выше приведенных схем.

Последовательные цифровые схемы (ПЦС). Схемы с памятью

В ПЦС сигналы на выходе зависят не только от сигналов на входе в данном такте, а также от состояния схемы в предыдущем такте.

х1 КЦС1 у1 у2 х2 у3 хi уi

OС

Так как здесь есть цепь обратной связи, то ПЦС может работать как некоторый конечный автомат. Алгоритм работы конечного аппарата может записываться: 1) аналитически; 2) таблицей переходов (таблицей состояний), похожую на таблицу истинности и с помощью графов. Граф состоит из узла, указывающего состояние автомата, и линии связи перехода автомата из одного состояния в другое, с указанием условий этого перехода.

7.1 Триггеры (простейшие ЦПС) Основой для их построения получила бистабильная ячейка (схема), имеющая два устойчивых состояния.

1 1

7.1.1 Основные понятия о триггерах. Устройство для хранения, запоминание одного разряда двоичного числа.

х1 Т Q х1, х2 – информационные входы __ х2 Q

Если триггер работает с синхронизацией, т.е. может переключаться только при синхронизирующих (тактовых) импульсах, то он называется синхронным и для синхроимпульсов есть специальный вход. В противном случае триггер называется асинхронным. х1 x1 Q c Т __ х2 x2 Q

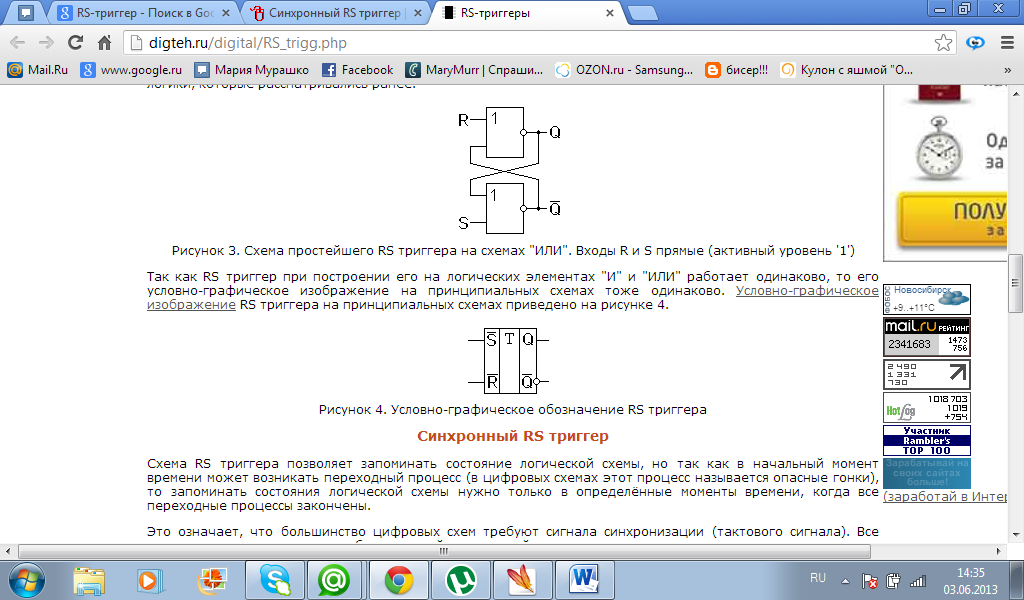

7.1.2. RS - триггер S – set – установка в «1» R – reset - сброс

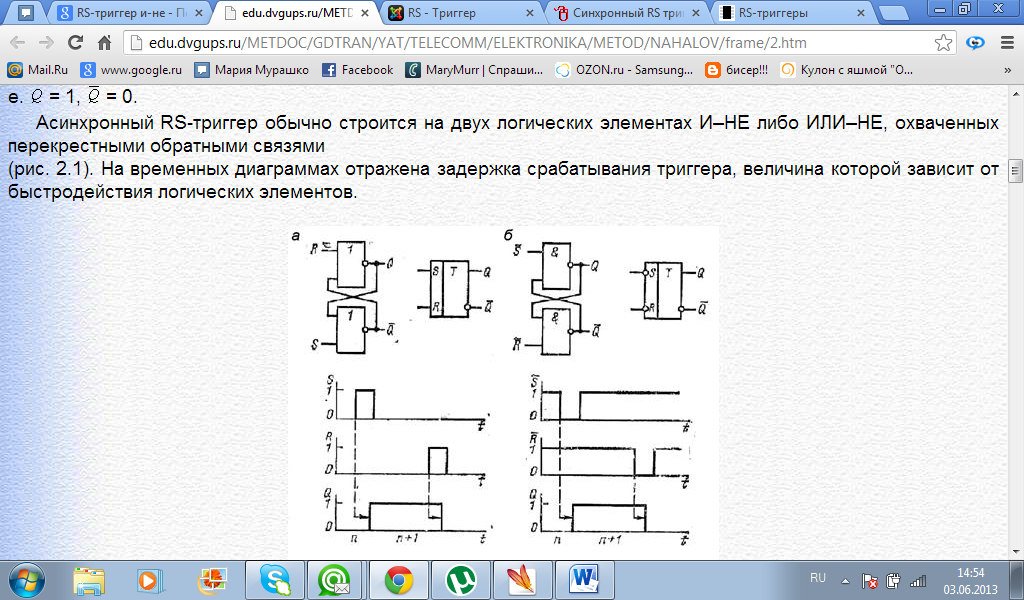

Асинхронный RS-триггер: на логических элементах ИЛИ-НЕ; на логических элементах И–НЕ

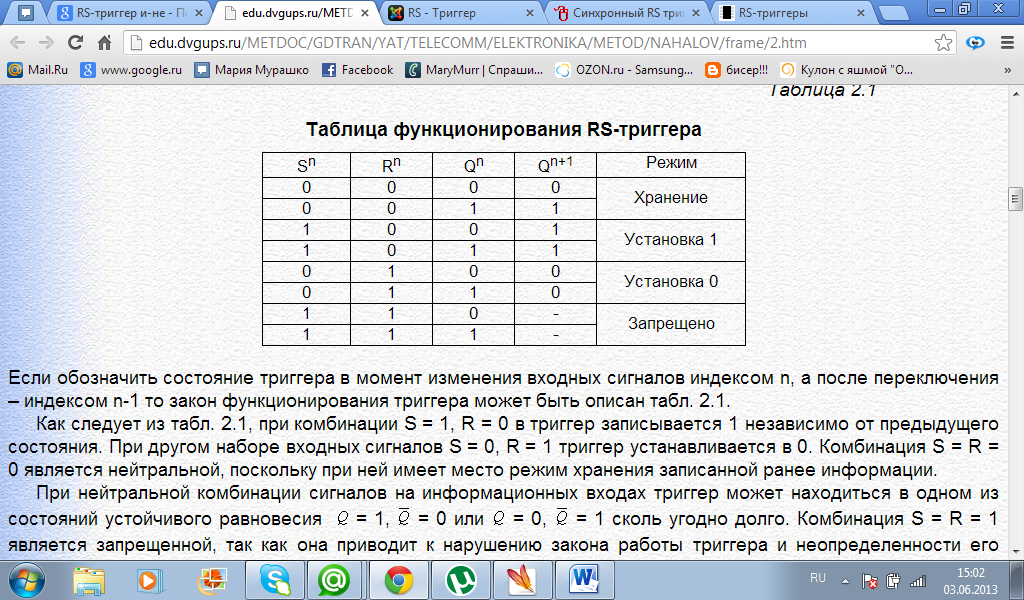

Если обозначить состояние триггера в момент изменения входных сигналов индексом n, а после переключения – индексом n-1 то закон функционирования триггера может быть описан табл. 2.1. Как следует из табл., при комбинации S = 1, R = 0 в триггер записывается 1 независимо от предыдущего состояния. При другом наборе входных сигналов S = 0, R = 1 триггер устанавливается в 0. Комбинация S = R = 0 является нейтральной, поскольку при ней имеет место режим хранения записанной ранее информации.

Устанавливается 0.

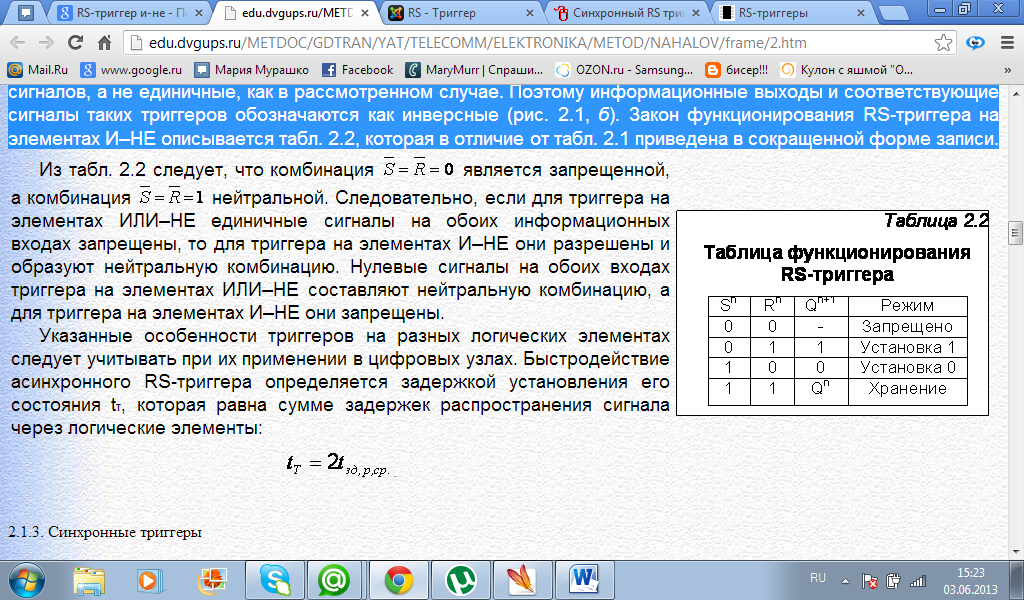

Для триггера на элементах И–НЕ управляющим действием обладают нулевые уровни информационных сигналов, а не единичные, как в рассмотренном случае. Поэтому информационные выходы и соответствующие сигналы таких триггеров обозначаются как инверсные Закон функционирования RS-триггера на элементах И–НЕ описывается табл.2, которая в отличие от табл.1 приведена в сокращенной форме записи.

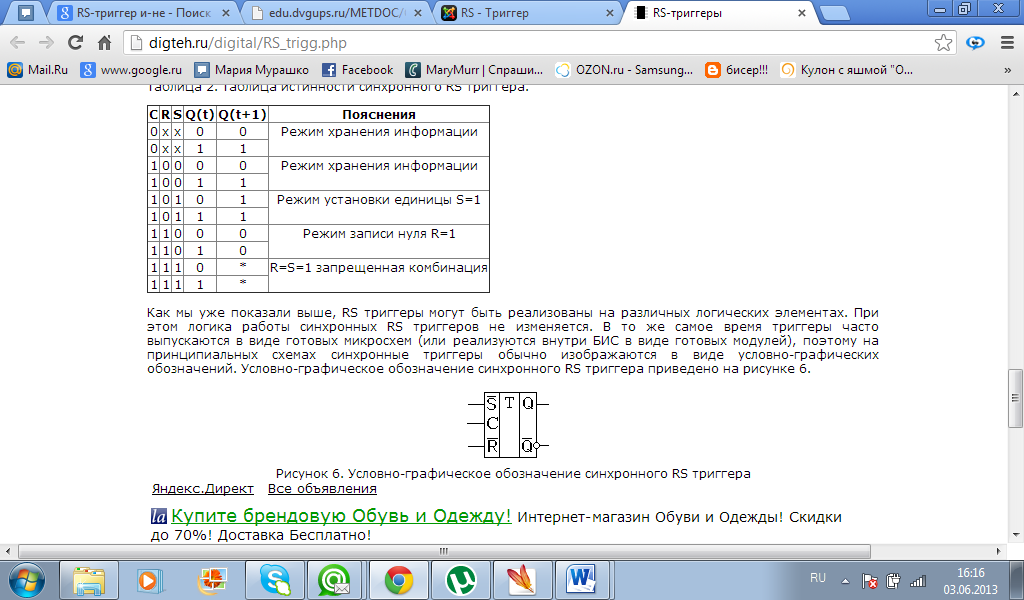

7.1.3 RS – синхронный однотактный триггер. Синхронный одноступенчатый RS-триггер отличается от асинхронного наличием С-входа для синхронизирующих (тактовых) импульсов. Синхронный триггер состоит из асинхронного RS-триггера и двух логических элементов на его входе.

В таблице 3 приведена таблица истинности синхронного RS триггера. В этой таблице символ x означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера. Таблица 3. Таблица истинности синхронного RS триггера.

7.1.4 Двухтактный RS Этот триггер меняет свое состояние только после окончательного действия сигнала синхронизации, т.е. по заднему его фронту.

S S S

C C R R R

C 1

Первый RC триггер срабатывает при наличии синхроимпульса (см.выше) перезапись из него во 2 триггер происходит только после окончания синхроимпульса, т.к. на 2 RS триггер сигнал передается через схему «не».

С

S TT

S C 0 1

R R 0 0 1

Q

0 1

ТТ – двухтактный; Такой триггер позволяет синтезировать цифровые автоматы.

7.1.5. D – триггер (задержки)

D ТТ

C D – триггер запоминает входной сигнал (или «1» или «0») по одному входу и хранит ее до прихода следующего двоичного сигнала и синхроимпульса. D

0 1 0 0 t C

t Q

0 1 0 0 t

реализация

Q S TT __ C Q R

7.1.6 Т – триггер. Это одноразрядный двоичный счетчик, переключающийся (считающий) каждый входящий импульс. Срабатывает (переключается) на выходе в противоположное состояние при подаче на его вход единицы (импульса).

а) однотактный асинхронный m триггер

Т Q Хсч

Реализуется на RS триггере:

1 0(1) Т Q S C __ R Q 0 1(0)

б) двухтактный асинхронный Т- триггер работает аналогично, только по заднему фронту импульса. Х

t Q

t

в) двухтактовый синхронный Реализация:

Т ТТ Q Xсч & S TT C & R

Он будет срабатывать только при наличии синхроимпульсов

7.1.7 j – k триггер Это универсальный триггер. Он аналогичен RS – триггер, но не имеет на входе запрещающих комбинаций, т.е. вход j º S, а k º R. K TT Q C J

Таблица состояний:

реализация:

S TT Q 0(1) j C

R k

Универсальность j-k - триггера На нем можно реализовать все виды триггеров а) RS – триггер (то же самое) j=S, k=R б) D – триггер на j-k триггере

J TT Q C

K

в) Т – триггер на j-k триггере

Хсч J TT Q C

K

Так как при подаче считаемых единиц импульсов на оба j и k триггер переключается в противоположное состояние.

г) Типовая схема j-k триггера в интегральных схемах.

S TT Q j

j C K

R

Такие схемы & на входе j-k триггера создаются для специального ускоренного режима счета импульсов.

|

||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 126; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.129.13.201 (0.035 с.) |

- прямой и инверсионный входы

- прямой и инверсионный входы

Если для триггера на элементах ИЛИ–НЕ единичные сигналы на обоих информационных входах запрещены, то для триггера на элементах И–НЕ они разрешены и образуют нейтральную комбинацию. Нулевые сигналы на обоих входах триггера на элементах ИЛИ–НЕ составляют нейтральную комбинацию, а для триггера на элементах И–НЕ они запрещены.

Если для триггера на элементах ИЛИ–НЕ единичные сигналы на обоих информационных входах запрещены, то для триггера на элементах И–НЕ они разрешены и образуют нейтральную комбинацию. Нулевые сигналы на обоих входах триггера на элементах ИЛИ–НЕ составляют нейтральную комбинацию, а для триггера на элементах И–НЕ они запрещены.

– инверсия

– инверсия